Interface circuit and achievement method for limiting output port voltage slew rate

A technology of output terminal voltage and interface circuit, which is applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc. It can solve the problem that the interface circuit cannot take into account the limitation of voltage slew rate and high transmission rate, etc. To achieve the effect of increasing the transmission rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

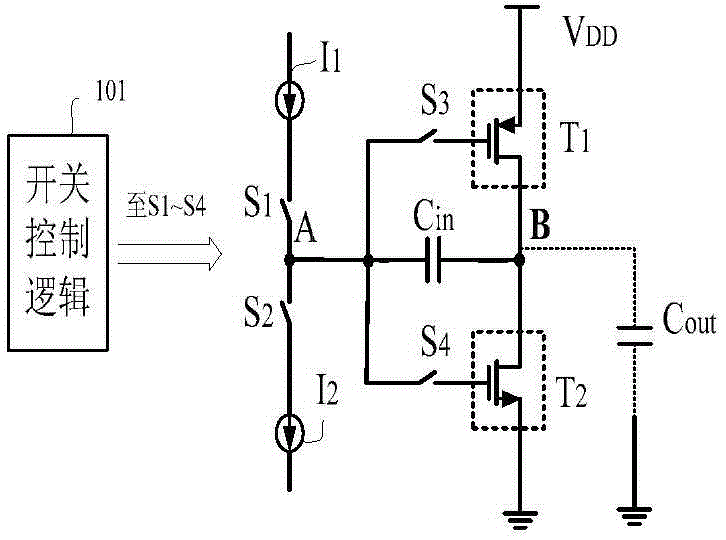

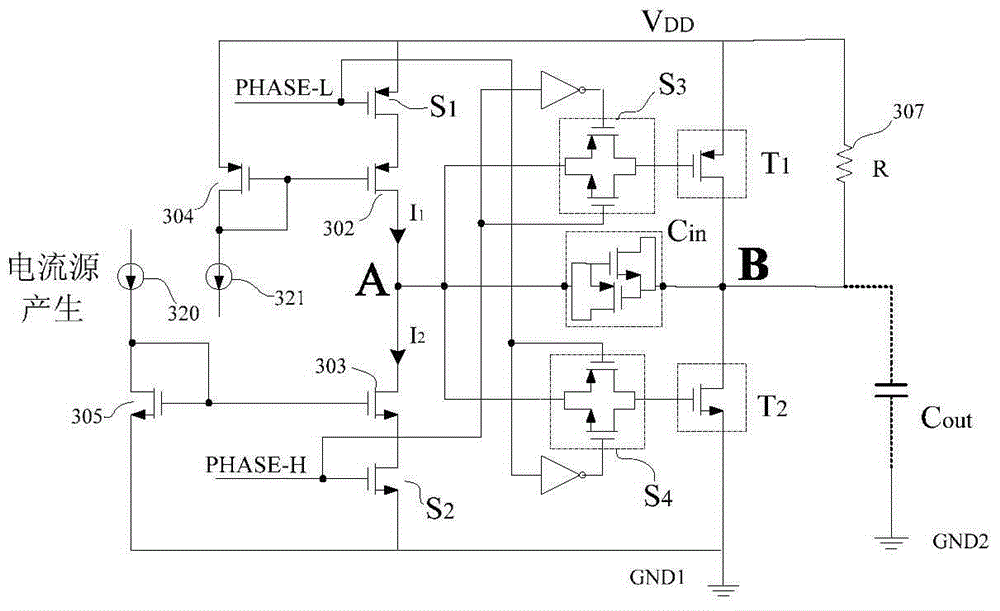

[0018] An interface circuit that limits the voltage slew rate at the output, see figure 1 The circuit principle shown includes: a current source I1, a current sink I2, a first switch S1 and a second switch S2 connected in series with the current source I1 and the current sink I2 respectively, and the switches connected in series between the power supply and the ground The first PMOS transistor T1 and the first NMOS transistor T2, the third switch S3 connected to the gate of the first PMOS transistor T1, the fourth switch S4 connected to the gate of the first NMOS transistor T2, the first PMOS transistor T1 and the first NMOS transistor The connection point of T2 is used as the output end of the interface circuit; the current source I1 branch and the current sink I2 branch are connected at the common end A, and the common end is connected to the other end of the third switch S3 and the fourth switch S4; the common end is connected to the output An on-chip capacitor Cin is conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More