Testing method of single bus chip

A test method and single-bus technology, applied in the direction of electronic circuit testing, etc., can solve the problems of inconvenient test operation, unsuccessful test, confusion of two pins, etc., and achieve the effect of improving test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

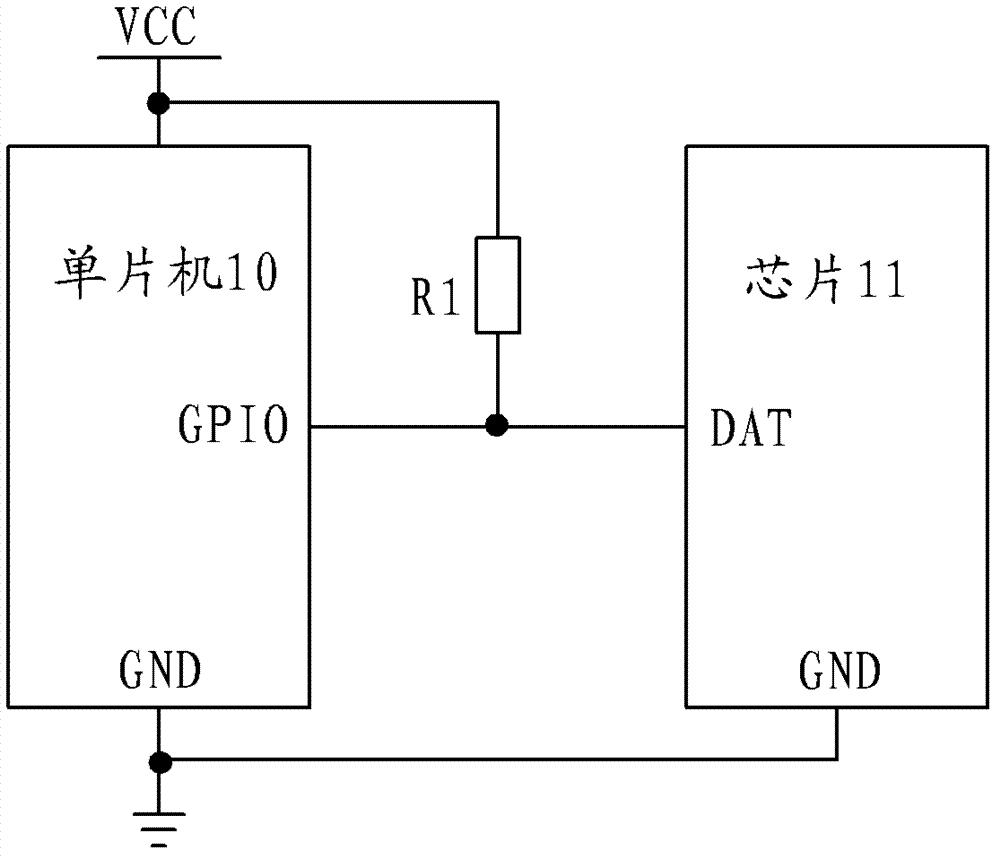

[0018] The present invention uses a test host to test a single-bus chip. The test host used in this embodiment is a single-chip microcomputer. Of course, a programmable device such as a field programmable gate array (FPGA) can also be used as a test host. The tested chip in this embodiment is a DS2432 chip produced by Dallas Company, which has two pins, namely a ground pin GND and a data pin DAT.

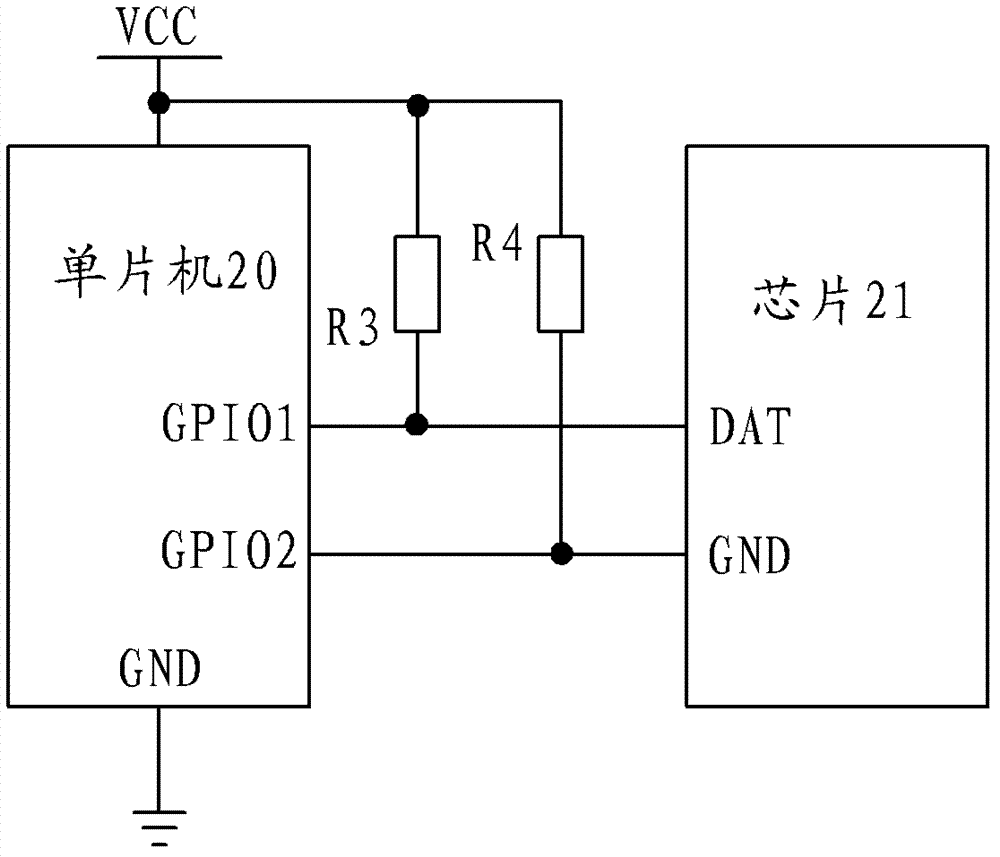

[0019] When testing, first connect the MCU to the chip, and the electrical schematic diagram of the connection between the MCU and the chip is as follows: figure 2 shown.

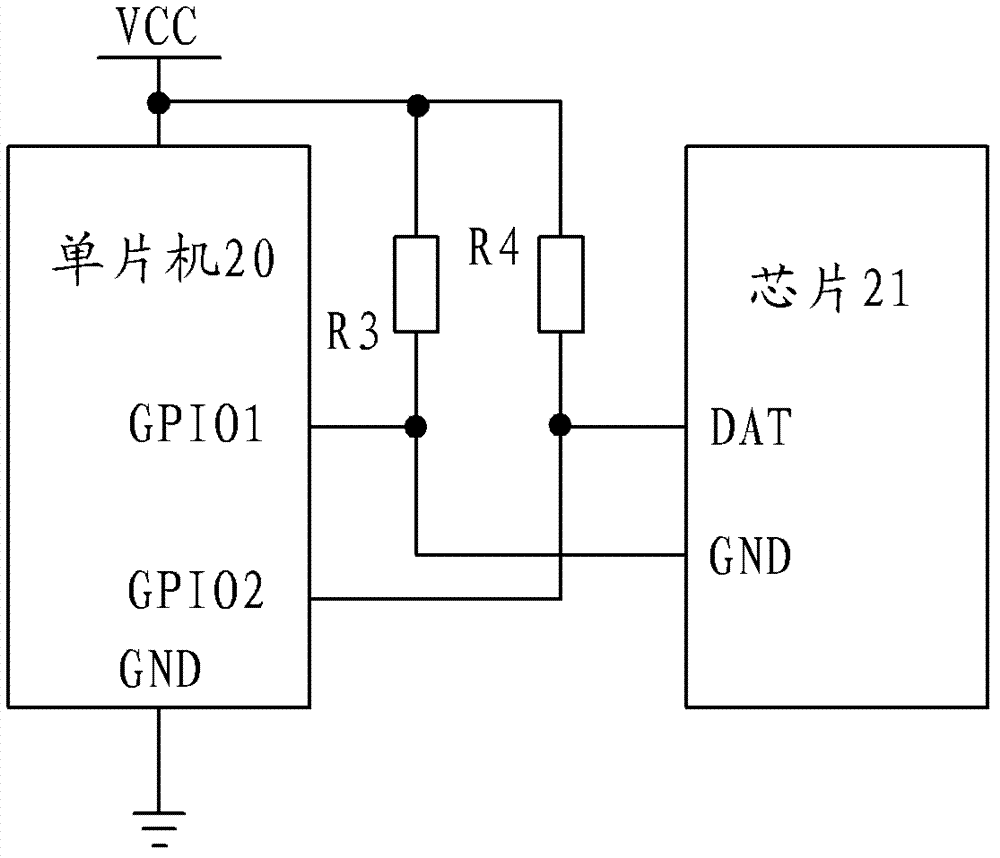

[0020] When connecting, first connect the power supply pin of the single-chip microcomputer 20 to the DC power supply VCC, ground the ground pin GND, and then connect the two pins of the chip 21 to be tested to the two pins of the single-chip microcomputer 20 . Since the two pins of chip 21 are not clearly identified, after connection, the following two connection situations may occur:

[0021] 1. The first pi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More