Classified power saving circuit and method for dram

A circuit and management circuit technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve problems such as failure, short effective width of data information, unstable reading command data sampling, etc., to improve stability and reduce transient State power consumption, the effect of improving practicality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

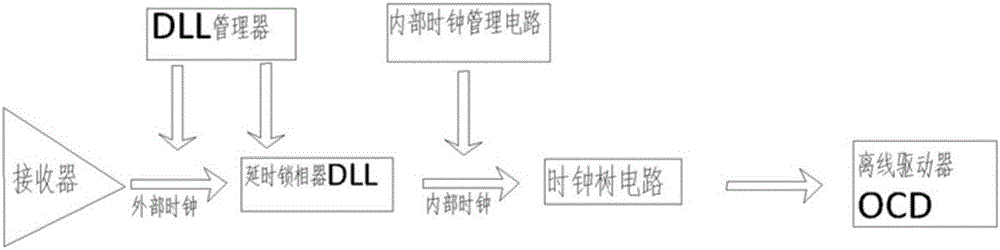

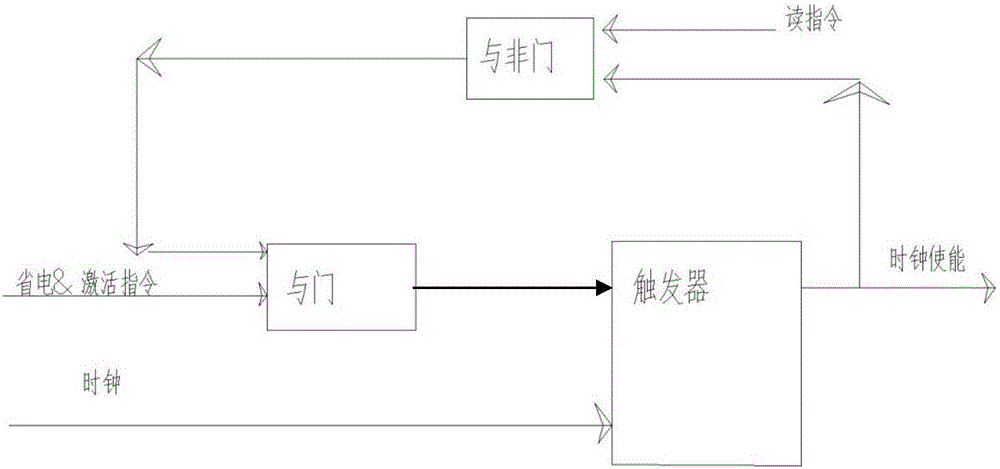

[0023] The present invention proposes a DRAM power-saving mode that can reduce transient consumption. The specific method is as follows:

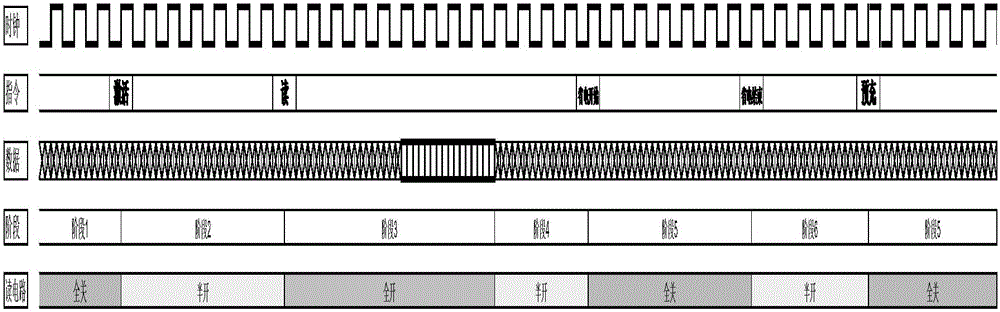

[0024] Normal read command sequence:

[0025] 1. The DRAM is in the stage of power-on completion and is in the state of waiting for instructions. The circuit will make the chip read-related circuits in a fully closed state.

[0026] 2. Activate the word line of the DRAM. The circuit will make the circuit related to the chip read in a half-open state.

[0027] 3. Activate the bit line of the DRAM and send the read command. The circuit will make the chip read related circuit fully open.

[0028] 4. Wait for the read data to be transmitted. The circuit will make the circuit related to the chip read in a half-open state.

[0029] 5. Precharge brings the DRAM back into standby mode. The way will make the chip read-related circuits in a fully closed state.

[0030] Read command sequence 1 including power saving command:

[0031] 1. The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com