Processor with polymorphic instruction set architecture

An instruction processing and set system technology, applied in the direction of concurrent instruction execution, machine execution devices, etc., can solve the problem of unable to redefine the processor instruction set, and achieve the effect of improving processing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0040] The present invention proposes a processor capable of dynamically reconfiguring a polymorphic instruction set architecture after tape-out (trial production).

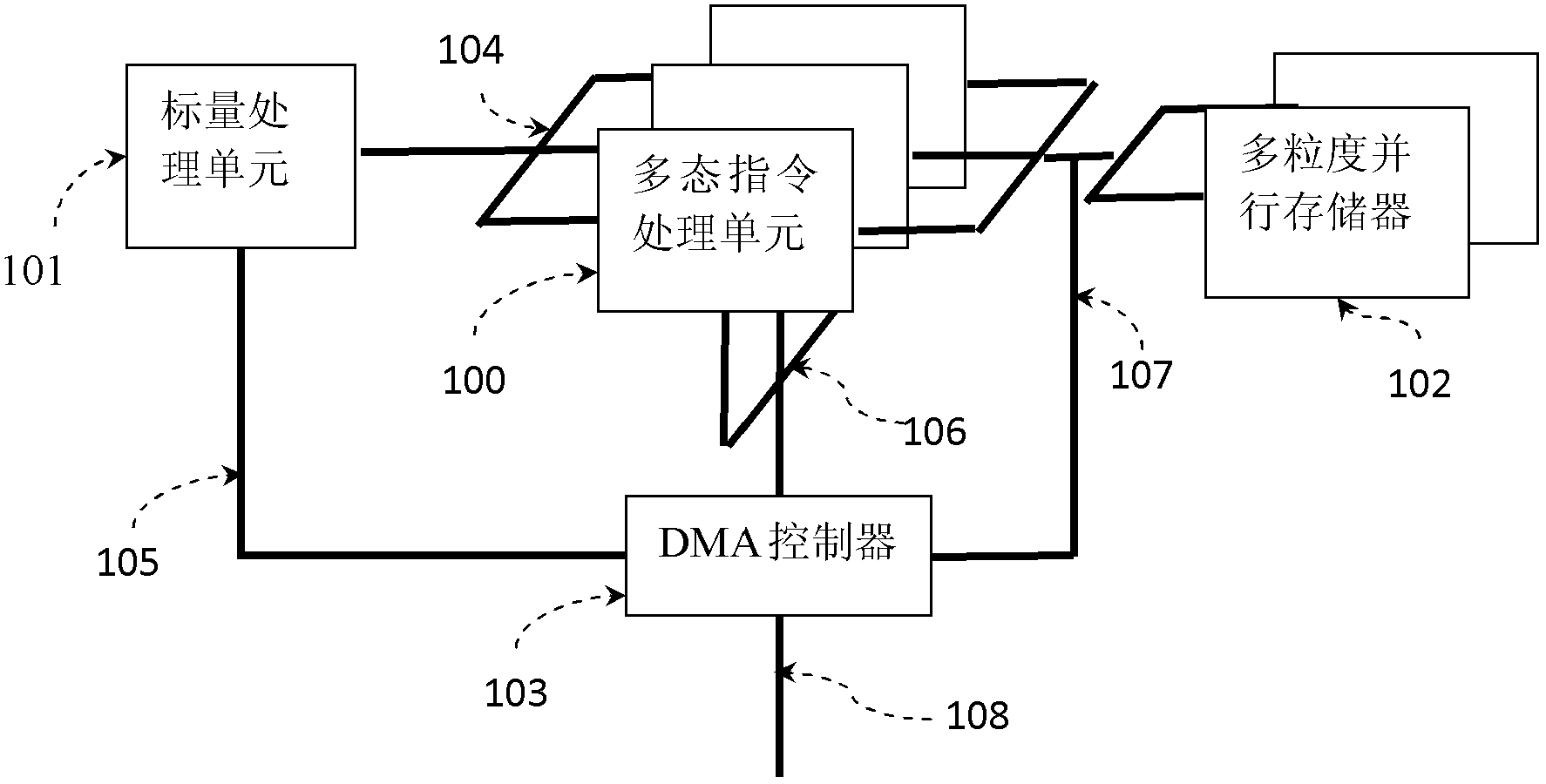

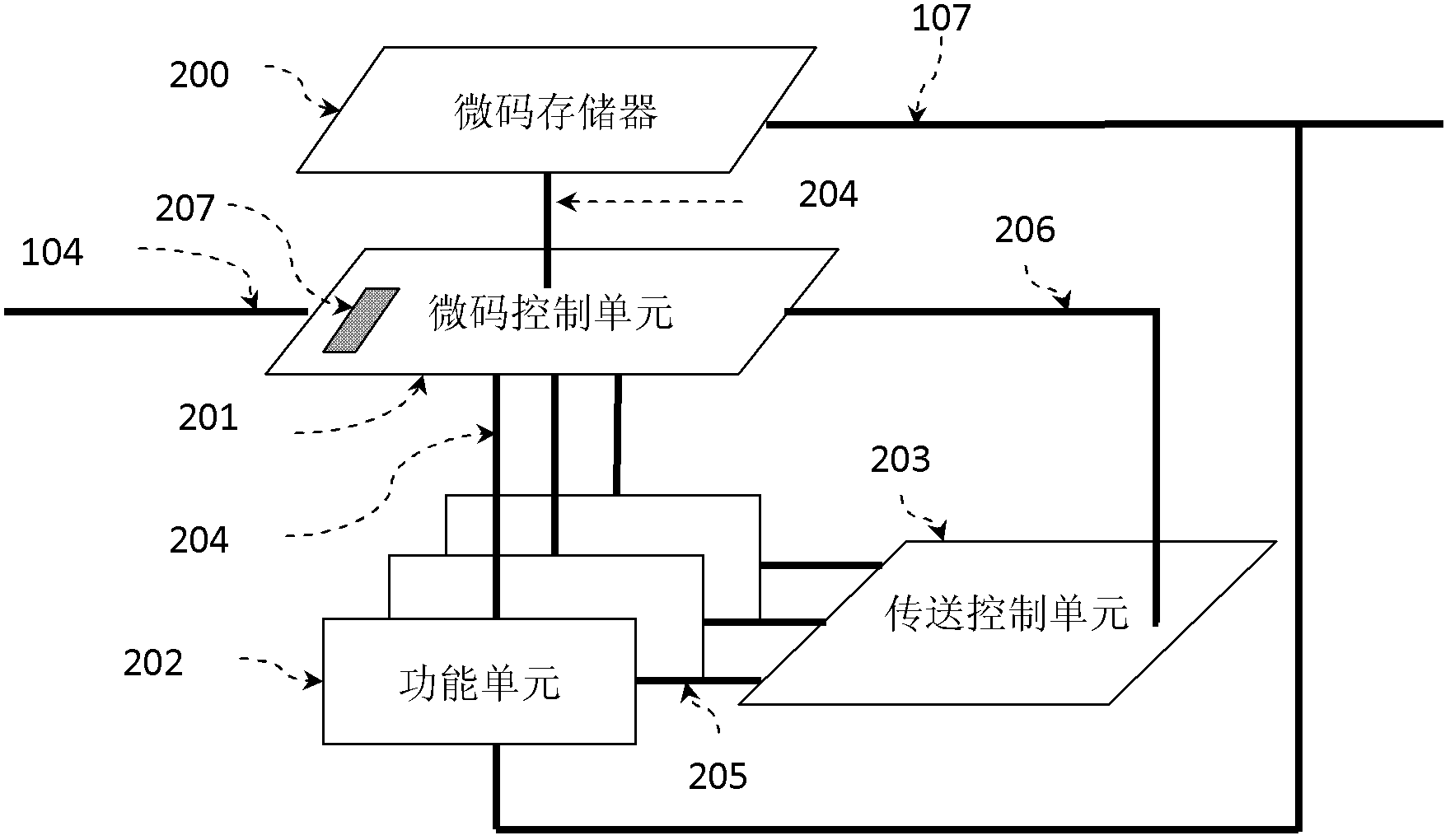

[0041] The structure of the processor of the present invention is as figure 1 As shown, it mainly includes the following components: a scalar processing unit 101 , at least one polymorphic instruction processing unit 100 , at least one multi-granularity parallel memory 102 and a DMA controller 103 . The polymorphic instruction processing unit 100 includes at least one functional unit.

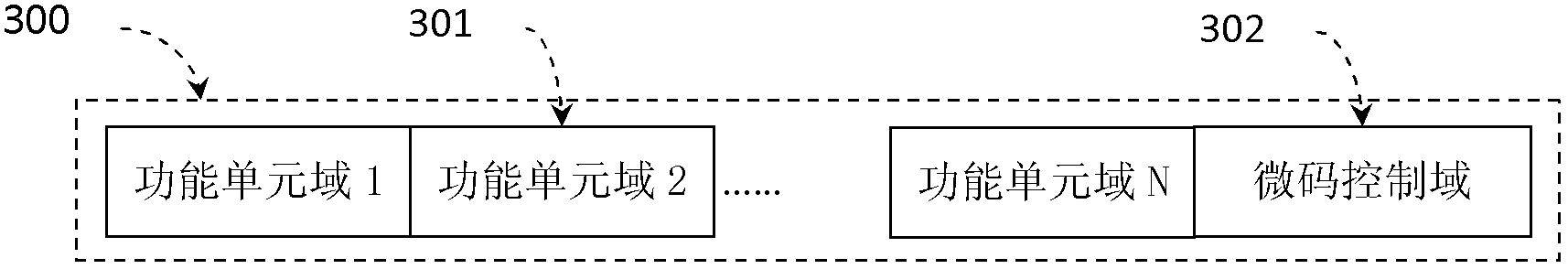

[0042] The polymorphic instruction refers to a sequence of multiple consecutively executed microcode records. The polymorphic instruction set is a collection of polymorphic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More