Scenario-based processor system-level verification completeness measurement method

A technology of processor system and measurement method, which is applied in the direction of function inspection and detection of faulty computer hardware, etc., can solve the problems of inability to test processor coverage, etc., and achieve the effect of fast verification speed and high verification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

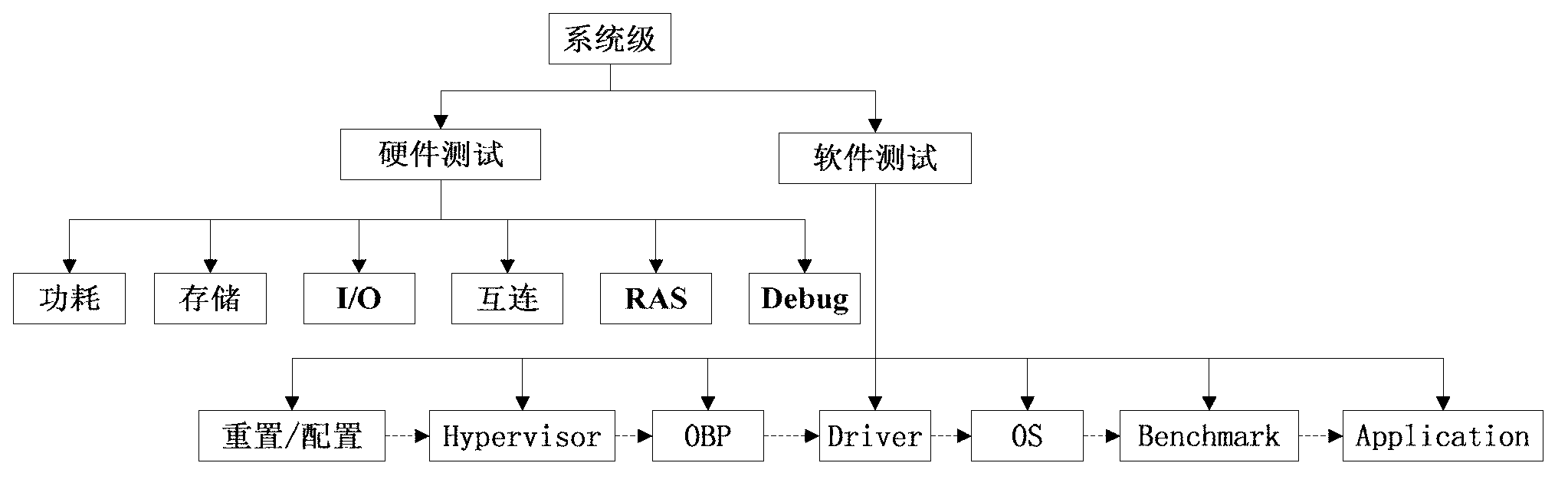

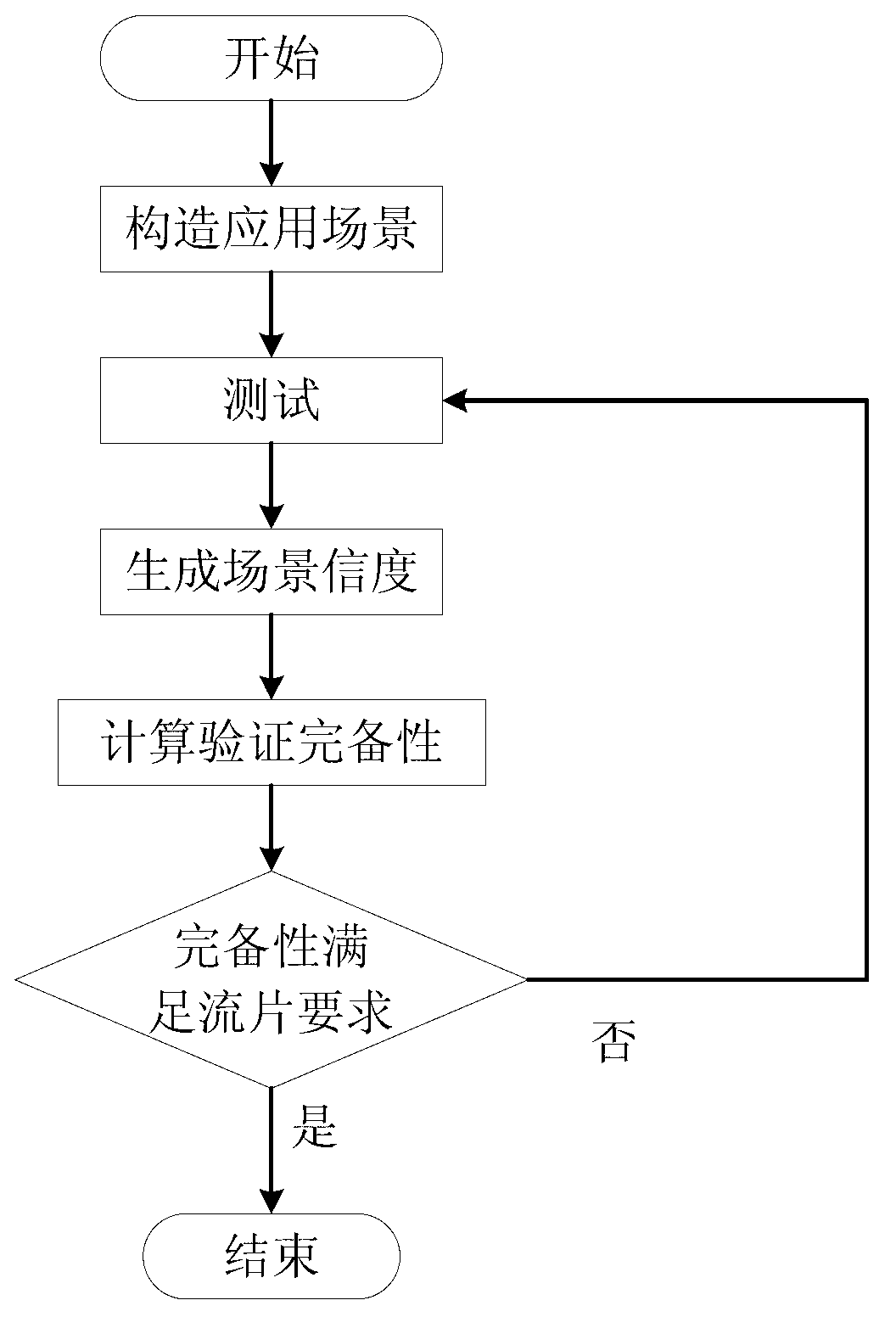

[0032] Such as figure 2 and image 3As shown, the implementation steps of the scenario-based processor system-level verification completeness measurement method in this embodiment are as follows:

[0033] 1) Construct typical application scenarios according to the application field of the processor;

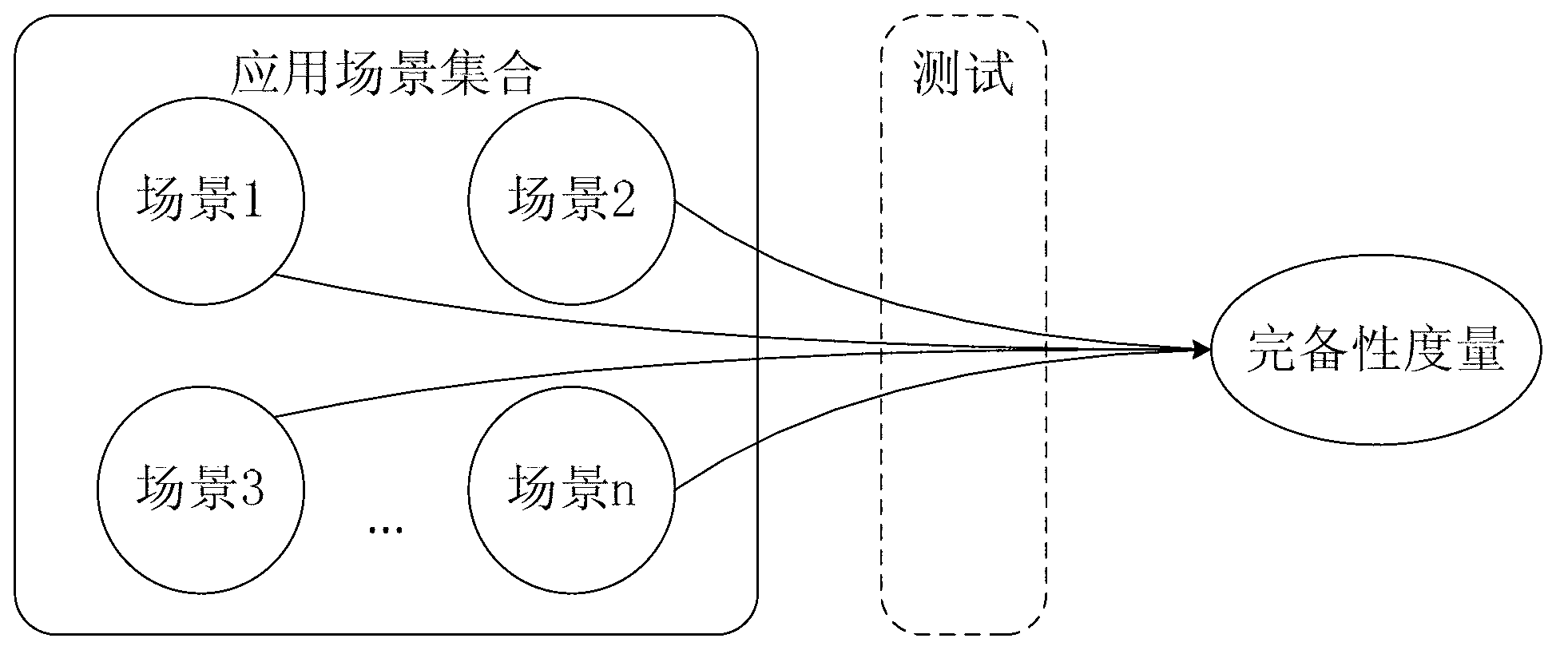

[0034] 2) Select an application scenario from the typical application scenarios as the current application scenario, and use test cases at the operating system level to test the processor for the current application scenario, and the number of correctly completed test cases accounts for the total number of all test cases in the current application scenario The ratio of the scenario reliability is generated, and the scenario reliability of the untested application scenario is defined as 0, and the weighted average of the scenario reliability of all application scenarios is used as the system-level verification completeness measurement value; the system obtained according to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More