Circuit partitioning method for parallel circuit simulation

A circuit simulation and circuit technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as differences and affect the efficiency of parallel simulation, and achieve the effect of low time complexity and effective control of load balance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described below in conjunction with the drawings and embodiments.

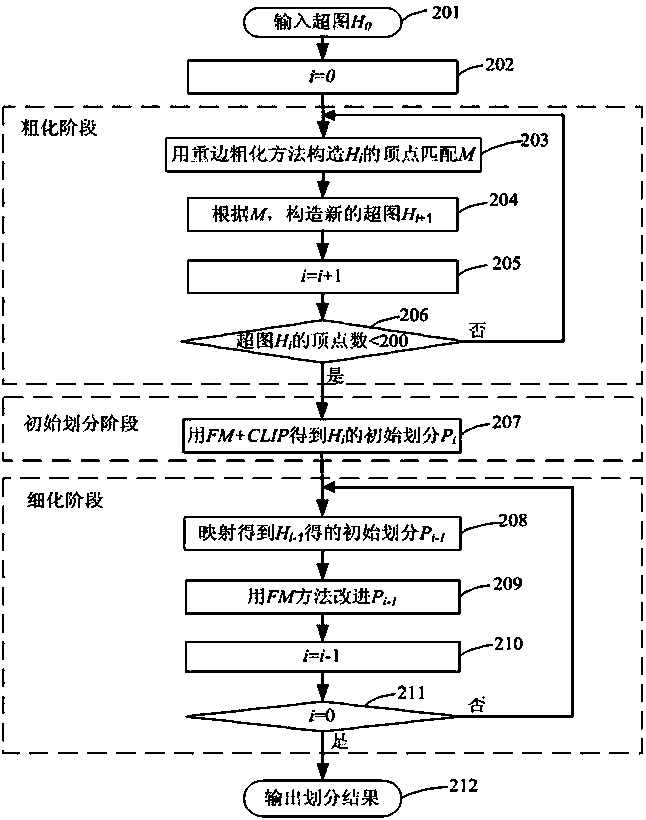

[0028] This embodiment provides a circuit division method for parallel circuit simulation, which is characterized by including the following steps:

[0029] (1) Express the circuit as a hypergraph H={V,E};

[0030] (2) H′ 0 =H;

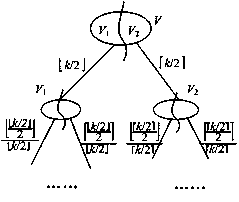

[0031] (3) Use the heavy edge roughening method for H′ 0 Perform coarsening to construct a series of hypergraphs H′ 1 , H′ 2 ,..., H′ m ;

[0032] (4) Use the FM+CLIP method to obtain H′ with the smallest cut as the goal m The division of P m ;

[0033] (5) To P m Perform mapping and optimize using FM method to obtain a series of partitions P m-1 , P m-2 ,..., P 0 ;

[0034] (6) According to P 0 Structure H′ 0 Subgraph H′ 01 And H′ 02 ;

[0035] (7) Let H′ 0 =H′ 01 And H′ 0 =H′ 02 , Repeat the process of (3)-(6) until the division number is k;

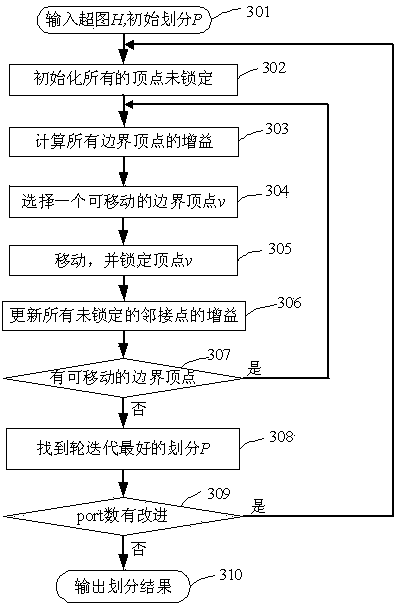

[0036] (8) Initialize that all vertices are not locked;

[0037] (9) According to the port number ∑ e ∈ C λ e ,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More