Patents

Literature

41 results about "Circuit partition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Integrated circuit partitioning placement and routing system

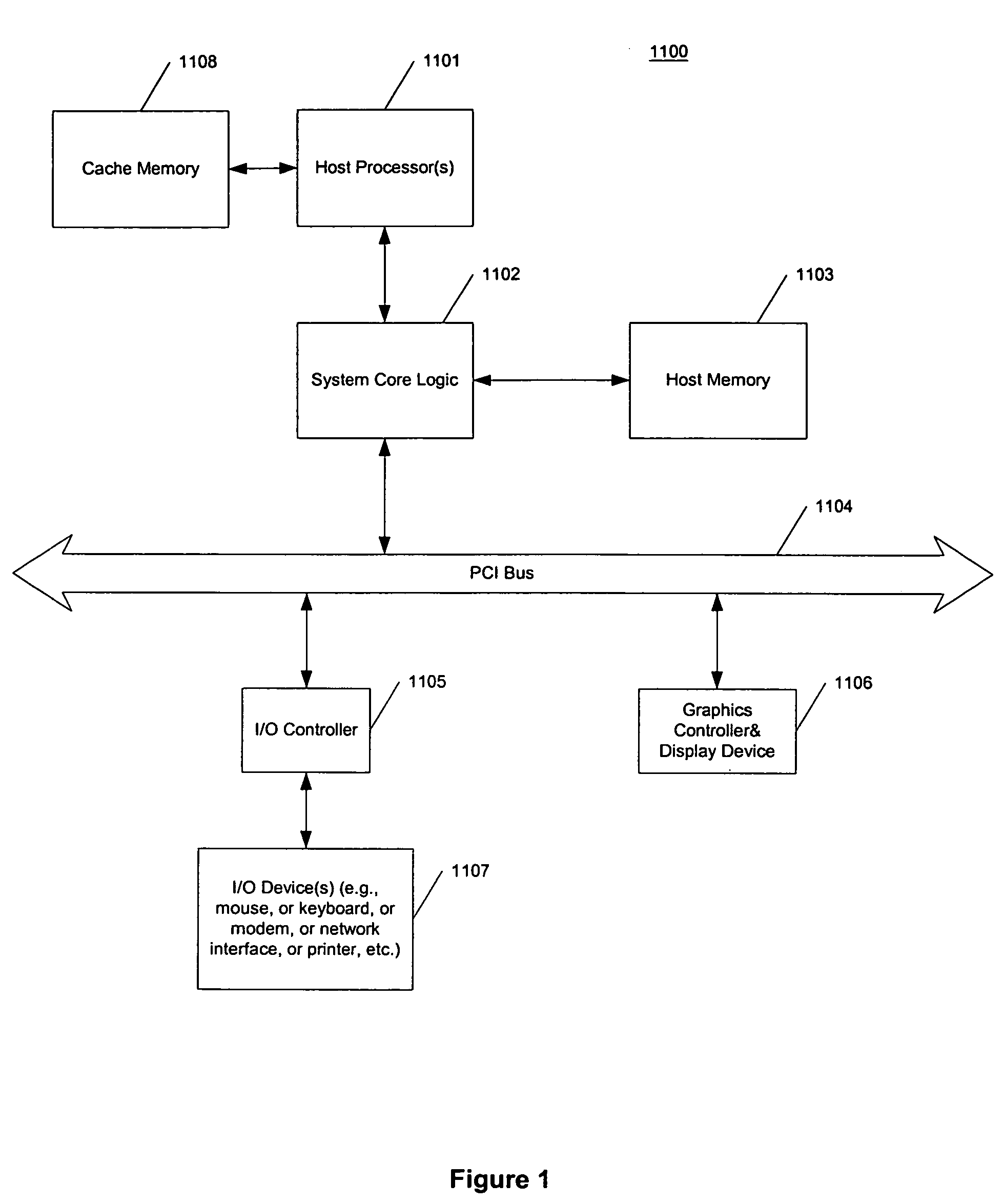

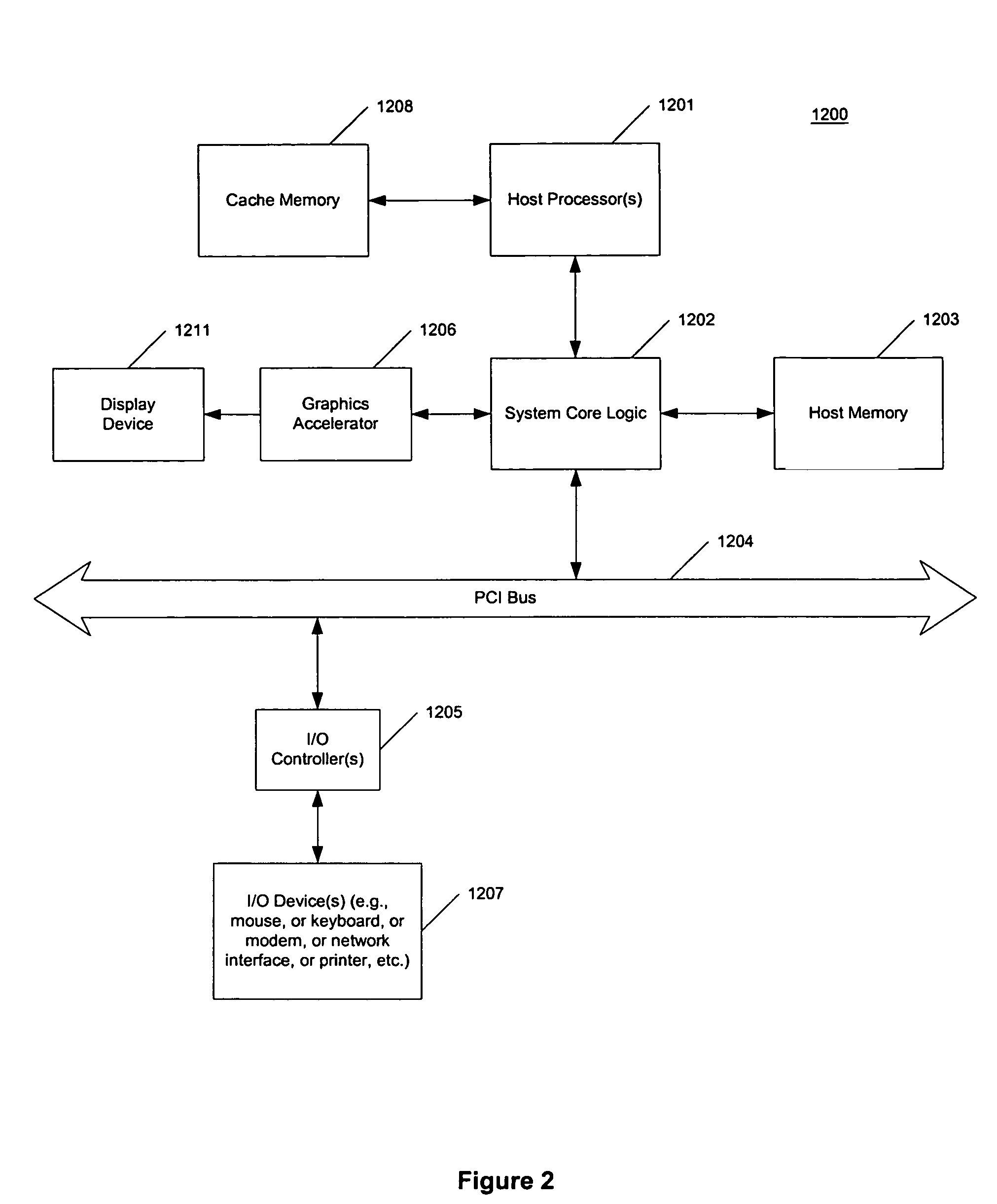

InactiveUS6519749B1Improve accuracySolid-state devicesSemiconductor/solid-state device manufacturingFloor planComputer module

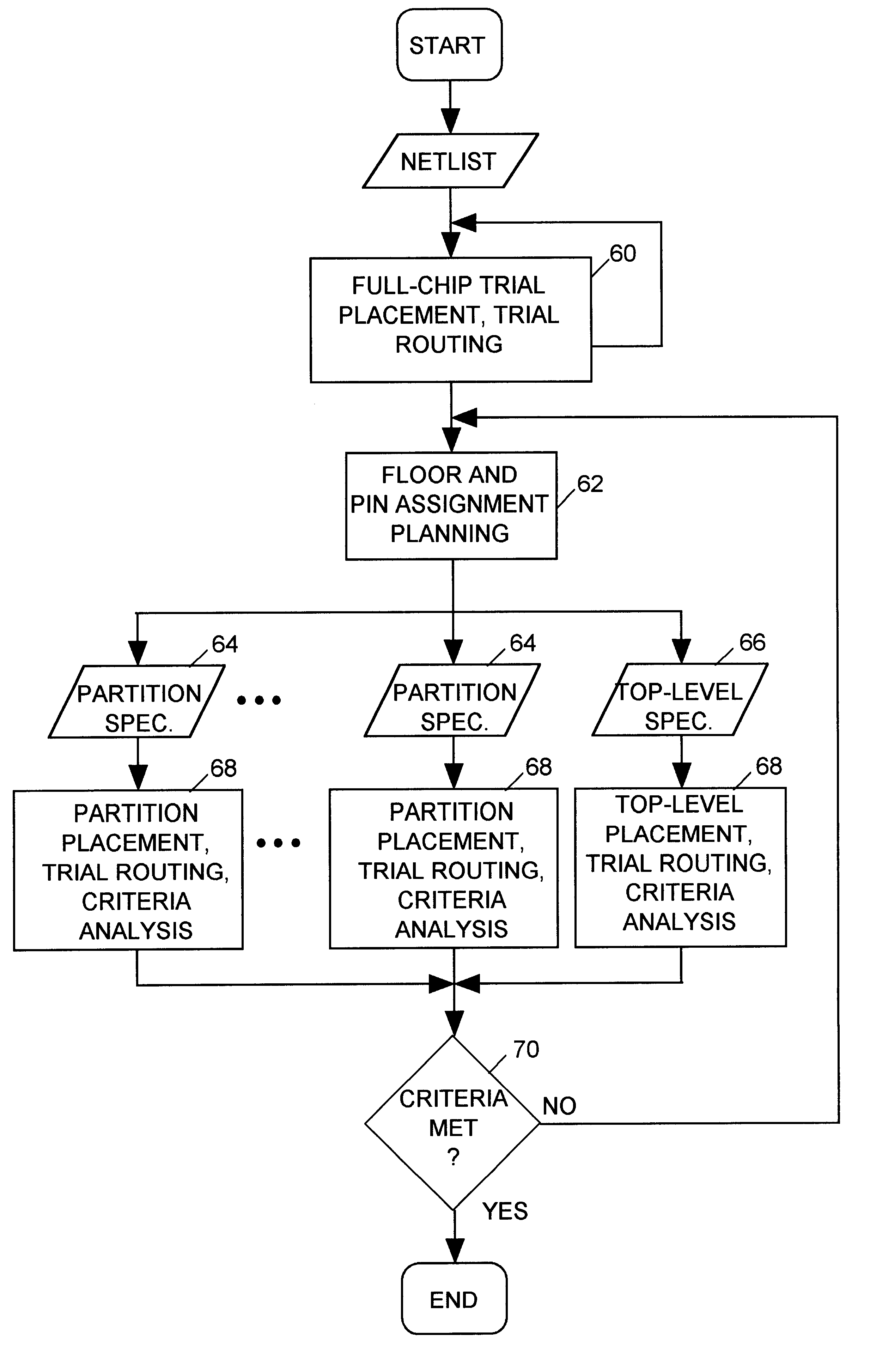

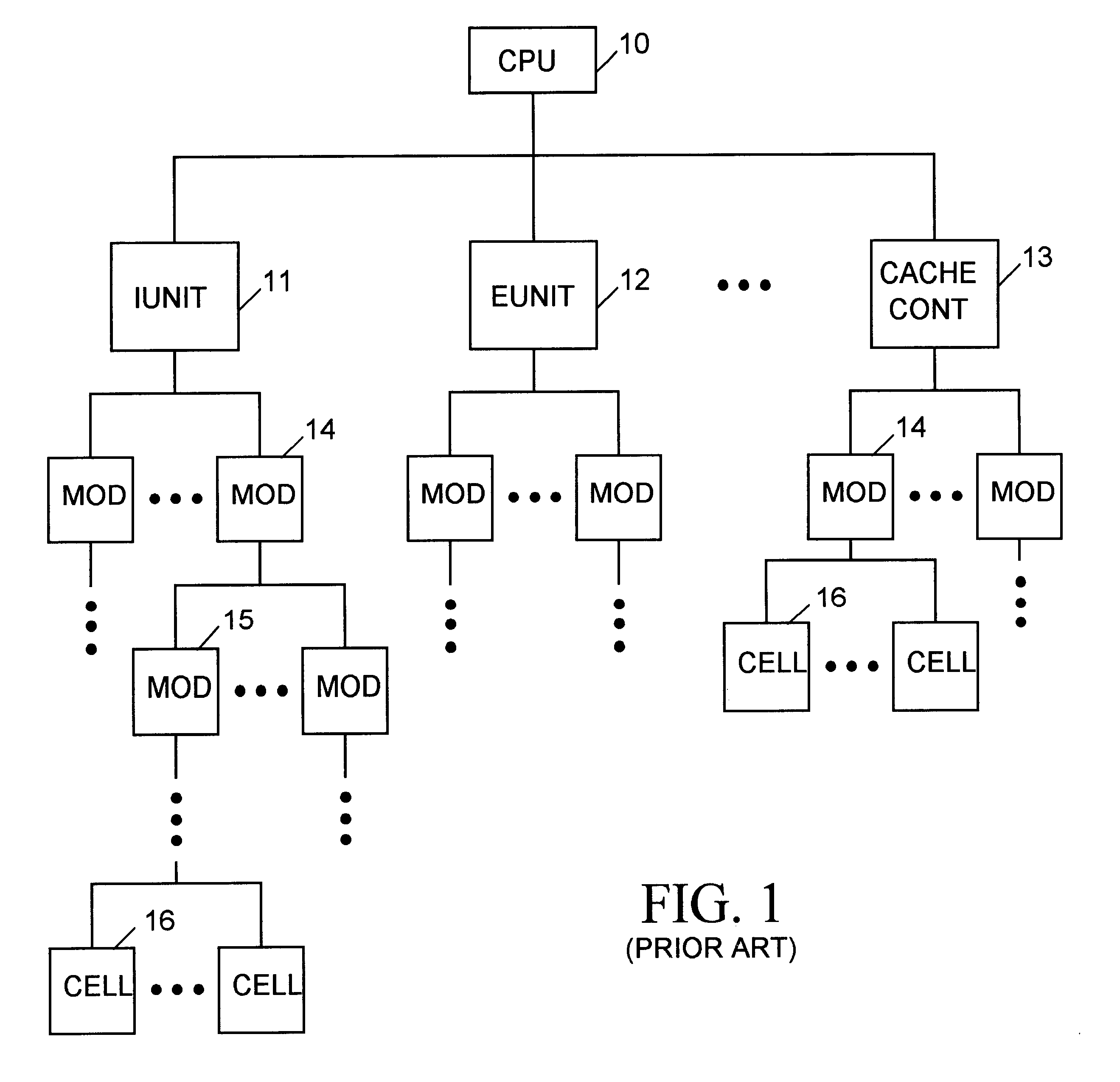

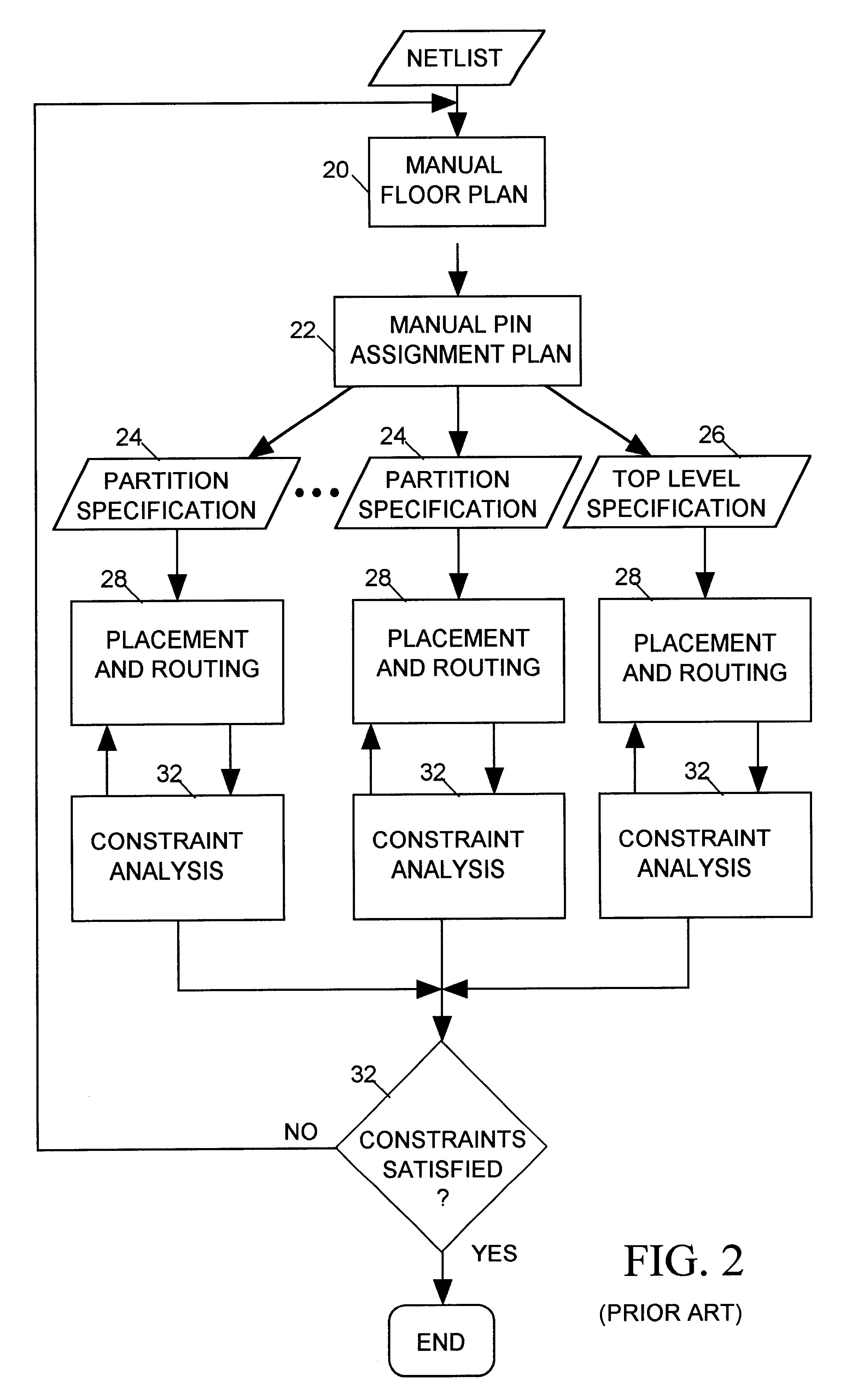

Disclosed herein is a method for dividing an integrated circuit (IC) design into several circuit partitions, each including one or more circuit modules, and then separately carrying out placement and routing for each circuit partition, with each partition being implemented within a separate area of an IC substrate. The method initially generates a whole-chip trial placement that tends to cluster cells of each circuit module together. An IC substrate floor plan assigning modules to various partitions is prepared, with the size, shape and relative position of each partition being determined by size, shape and relative position of areas of the substrate occupied by those modules in the trial floor plan. A trial routing is also performed with information on which to base a pin assignment plan for each module. A detailed placement and routing process is then independently performed for each partition, with placement and routing of cells within each partition constrained by the floor plan and pin assignment plan.

Owner:CADENCE DESIGN SYST INC

Apparatus for parallel vector table look-up

InactiveUS7055018B1General purpose stored program computerProgram controlExecution unitCircuit partition

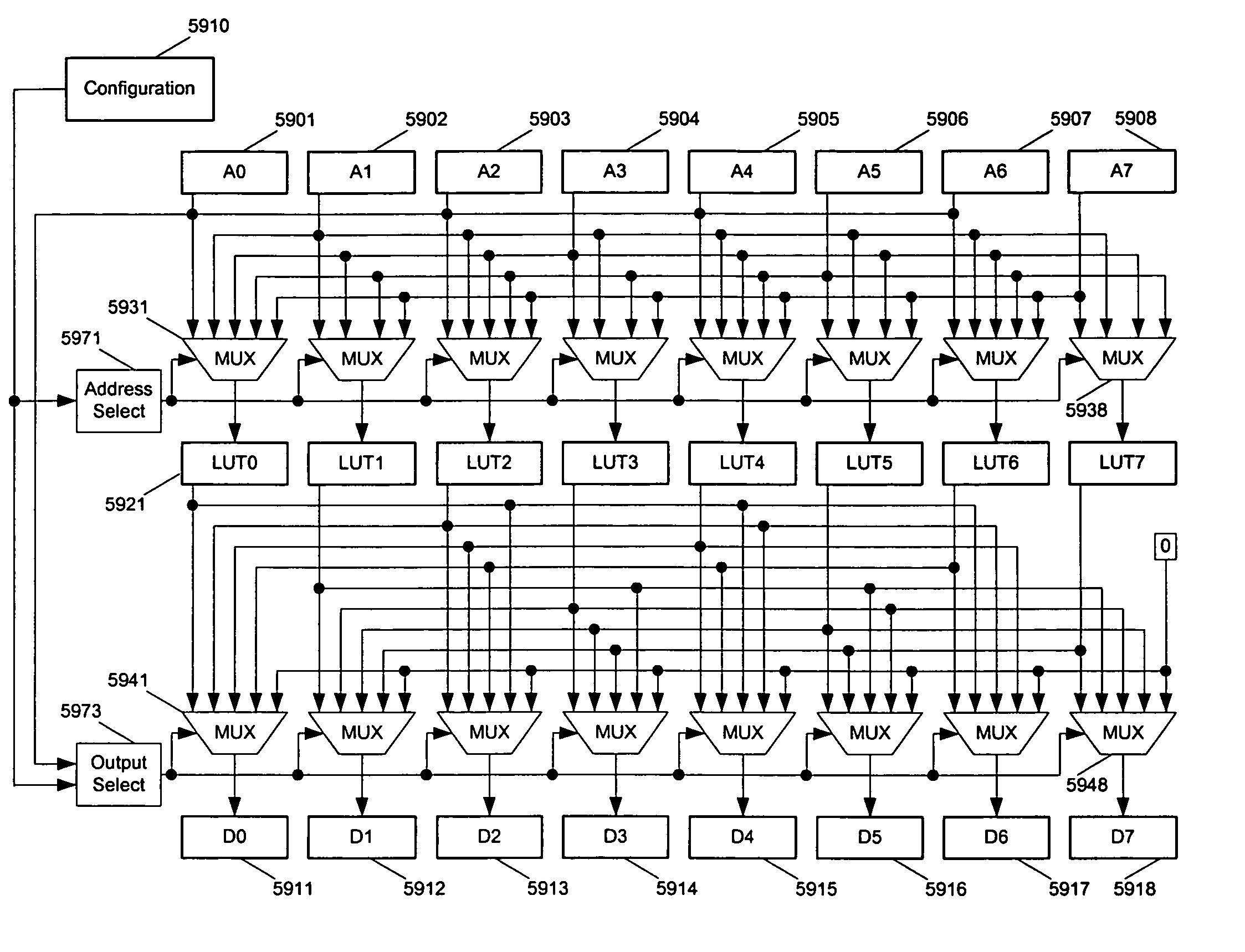

Methods and apparatuses for performing simultaneous table look-up using multiple look-up tables. In one aspect of the invention, an execution unit in a microprocessor includes: look-up memory and a first circuit coupled to the look-up memory. In response to the microprocessor receiving a first instruction, the first circuit partitions the look-up memory into a first plurality of look-up tables. In response to the microprocessor receiving a second instruction, the first circuit partitions the look-up memory into a second plurality of look-up tables; and the second plurality of look-up tables simultaneously look up a plurality of entries.

Owner:APPLE INC

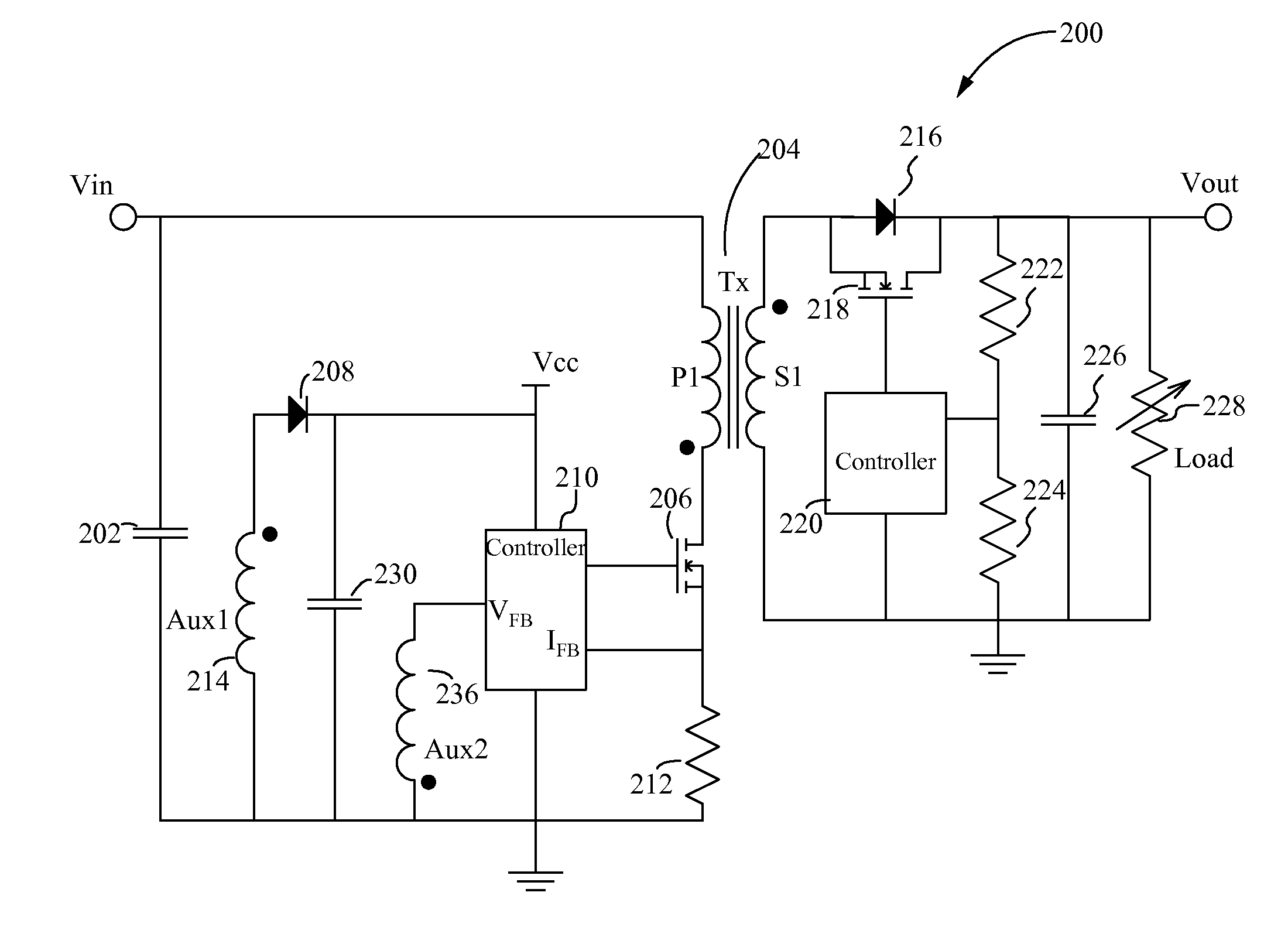

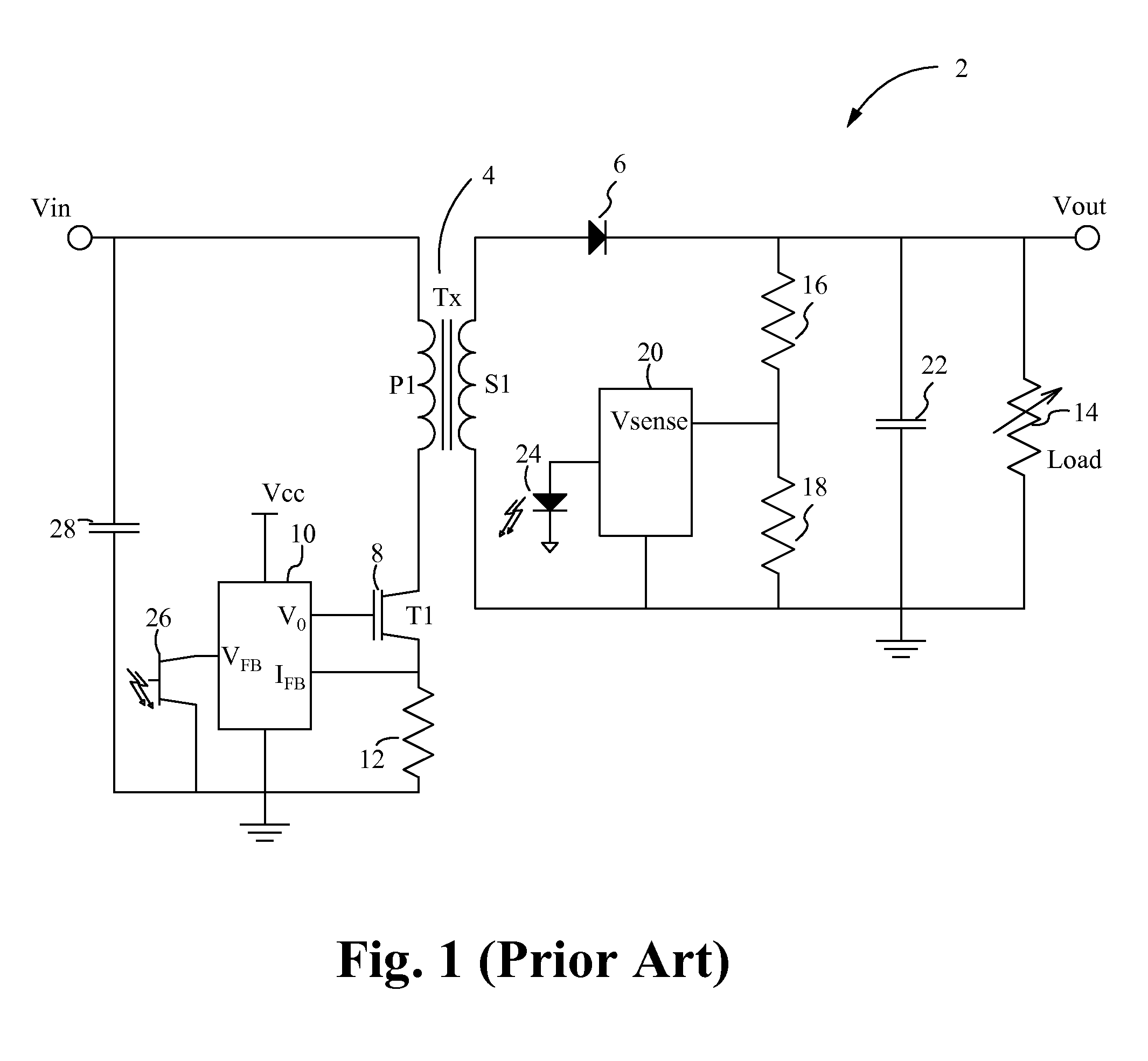

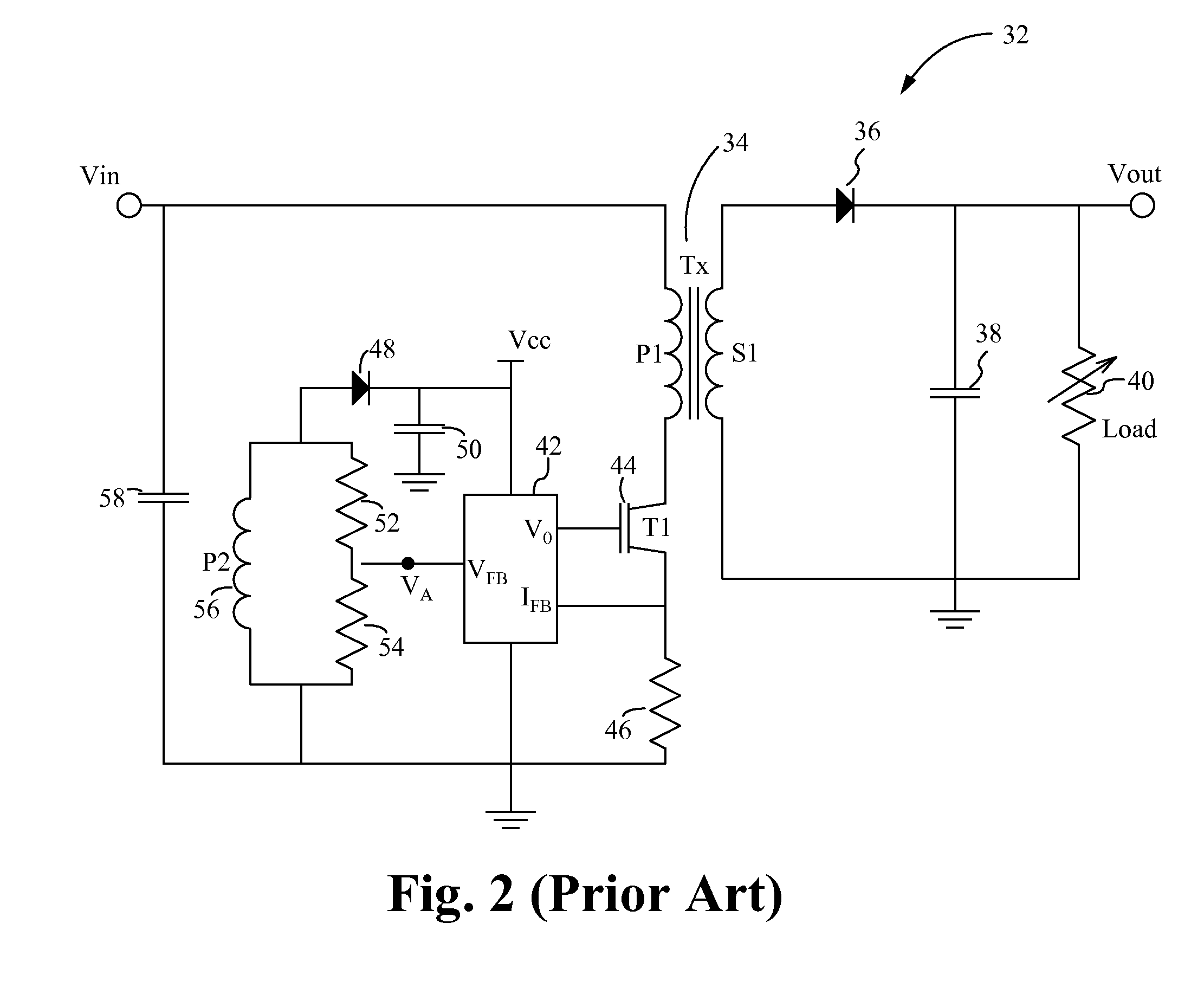

Power management integrated circuit partitioning with dedicated primary side control winding

ActiveUS20140268911A1Speed up the processEfficient power electronics conversionDc-dc conversionControl signalPulse sequence

A switched mode power converter having a feedback mechanism by which a coded train of pulses with well defined integrity is generated on a secondary side of the power converter and transmitted to a dedicated control signal winding on the primary side for decoding and application to regulate the power converter output. The control signal winding enables separation of control signal transmission and power transmission resulting in improved processing of the control signal by a primary side controller. The pulse train is modulated by a secondary side controller, transmitted across a transformer and received by the control signal winding, and supplied to the primary side controller. Coded information is included in the coded pulse train by modulating pulses of the pulse train.

Owner:FLEXTRONICS AP LLC

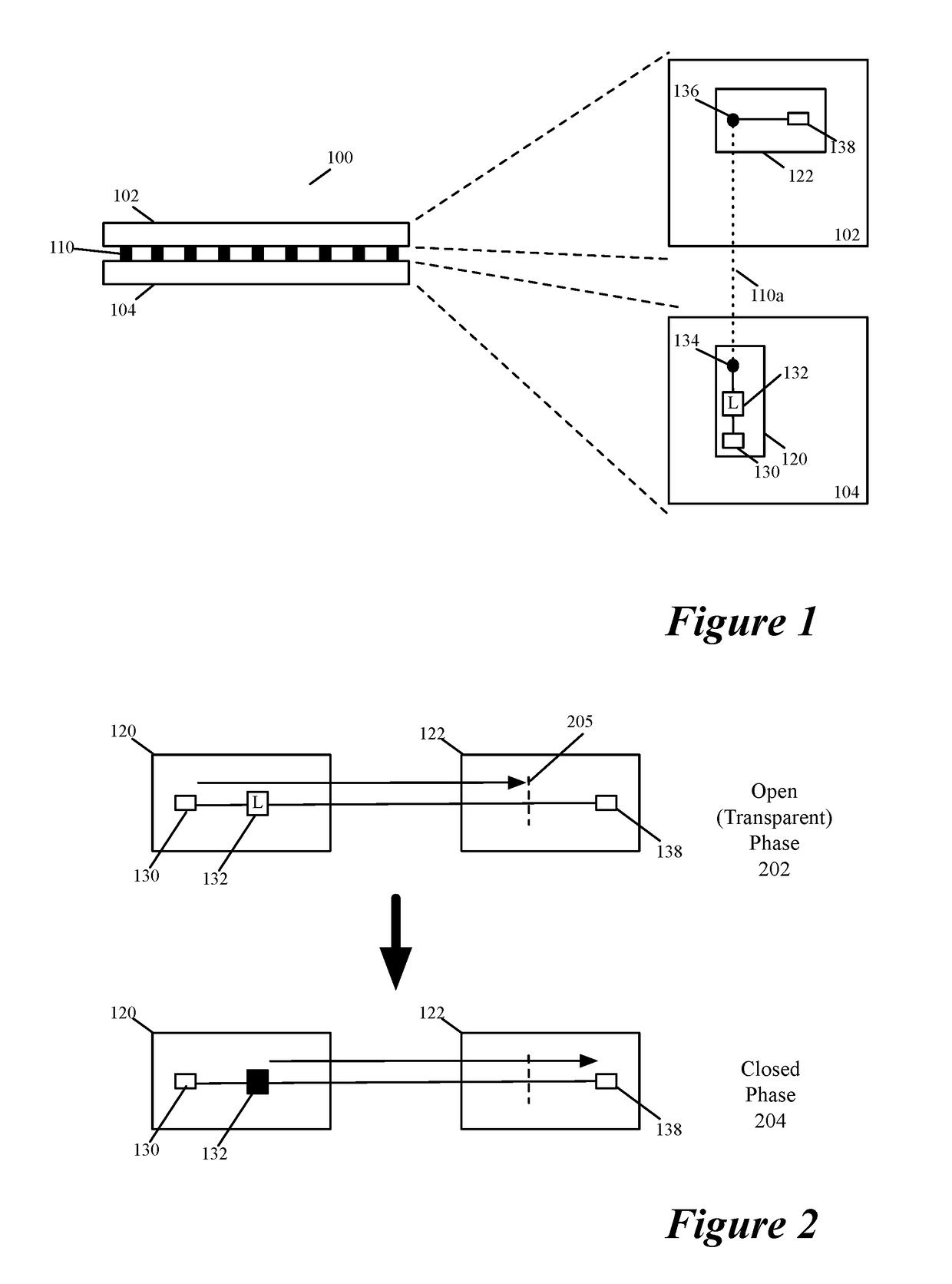

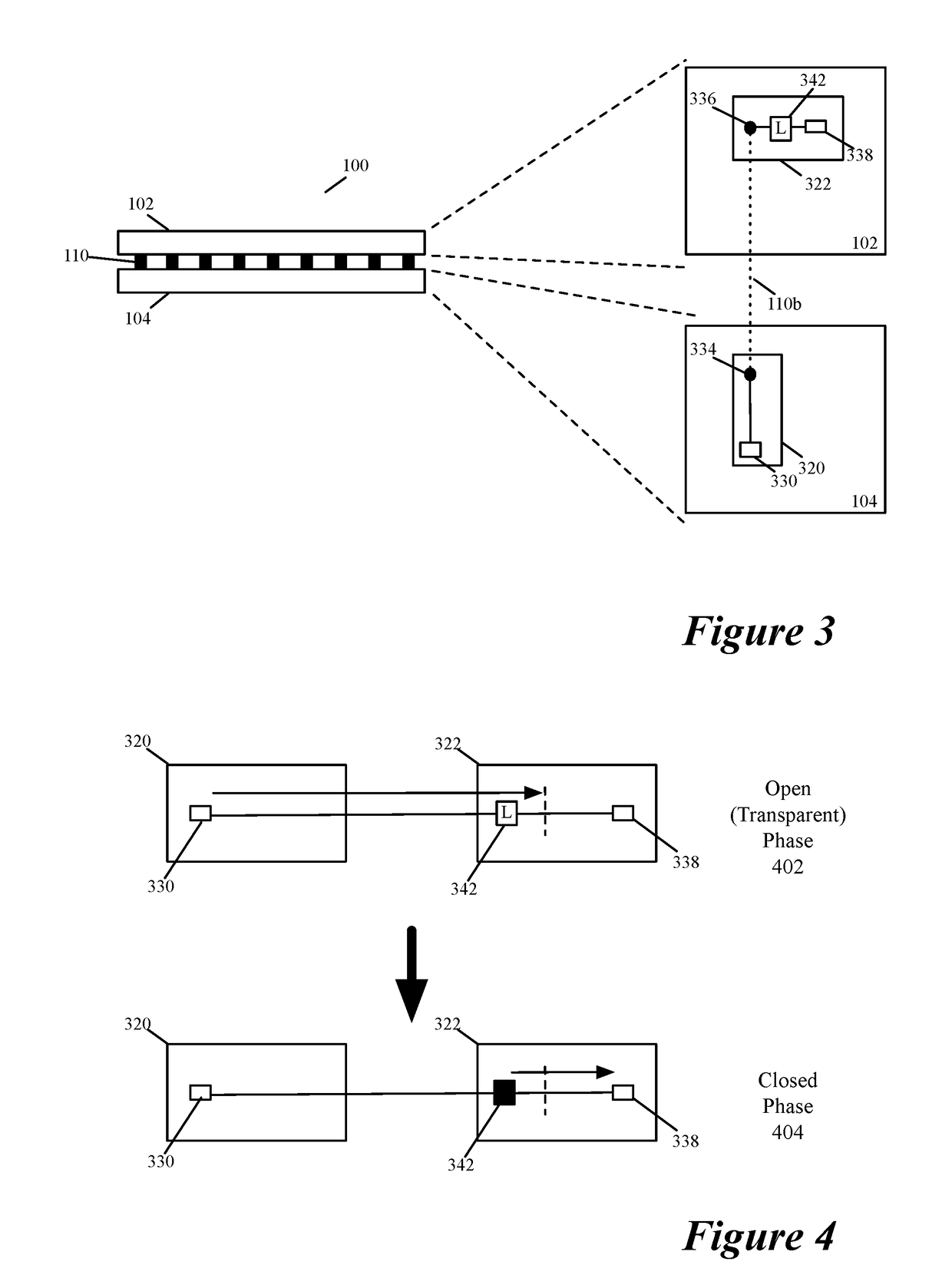

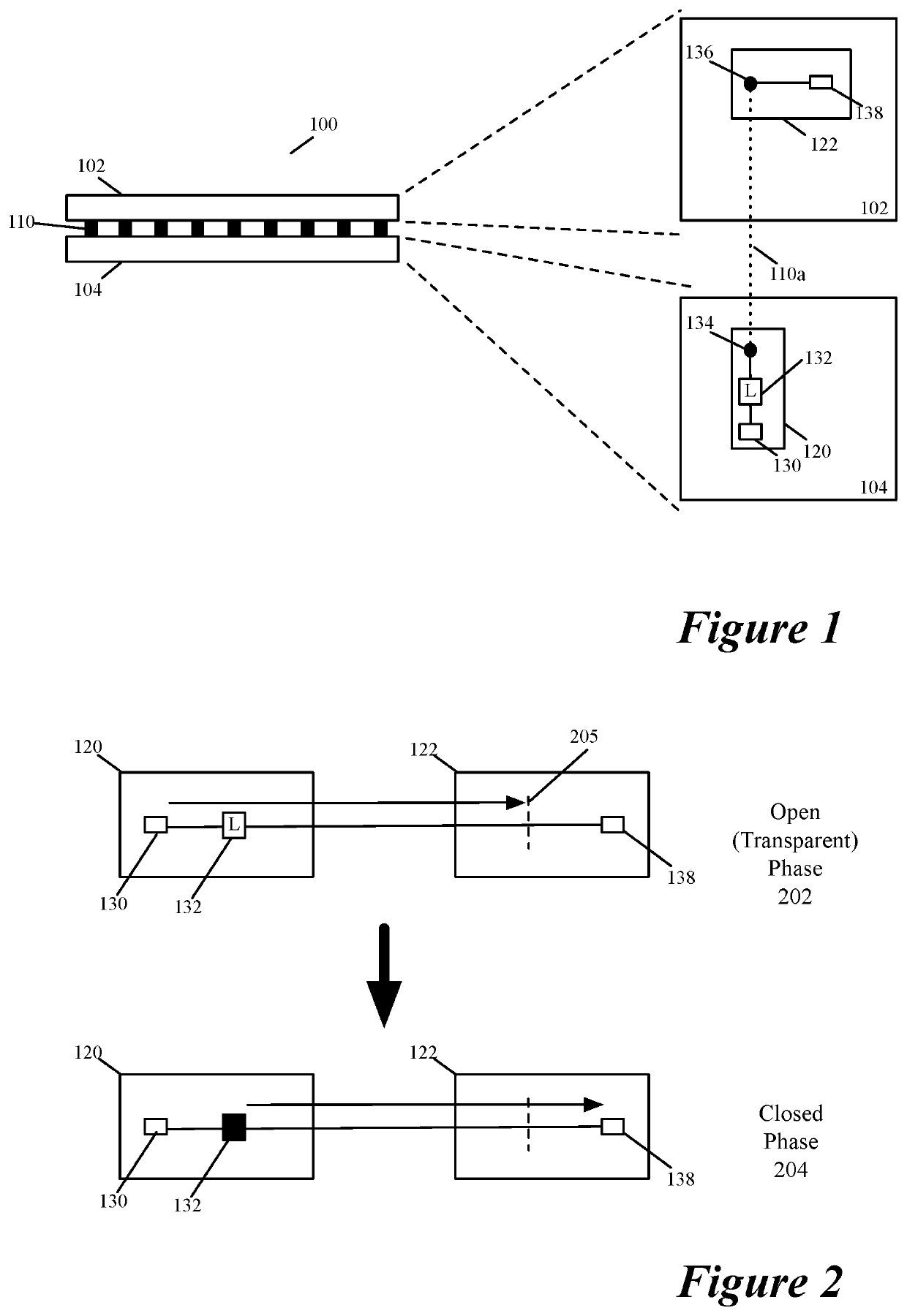

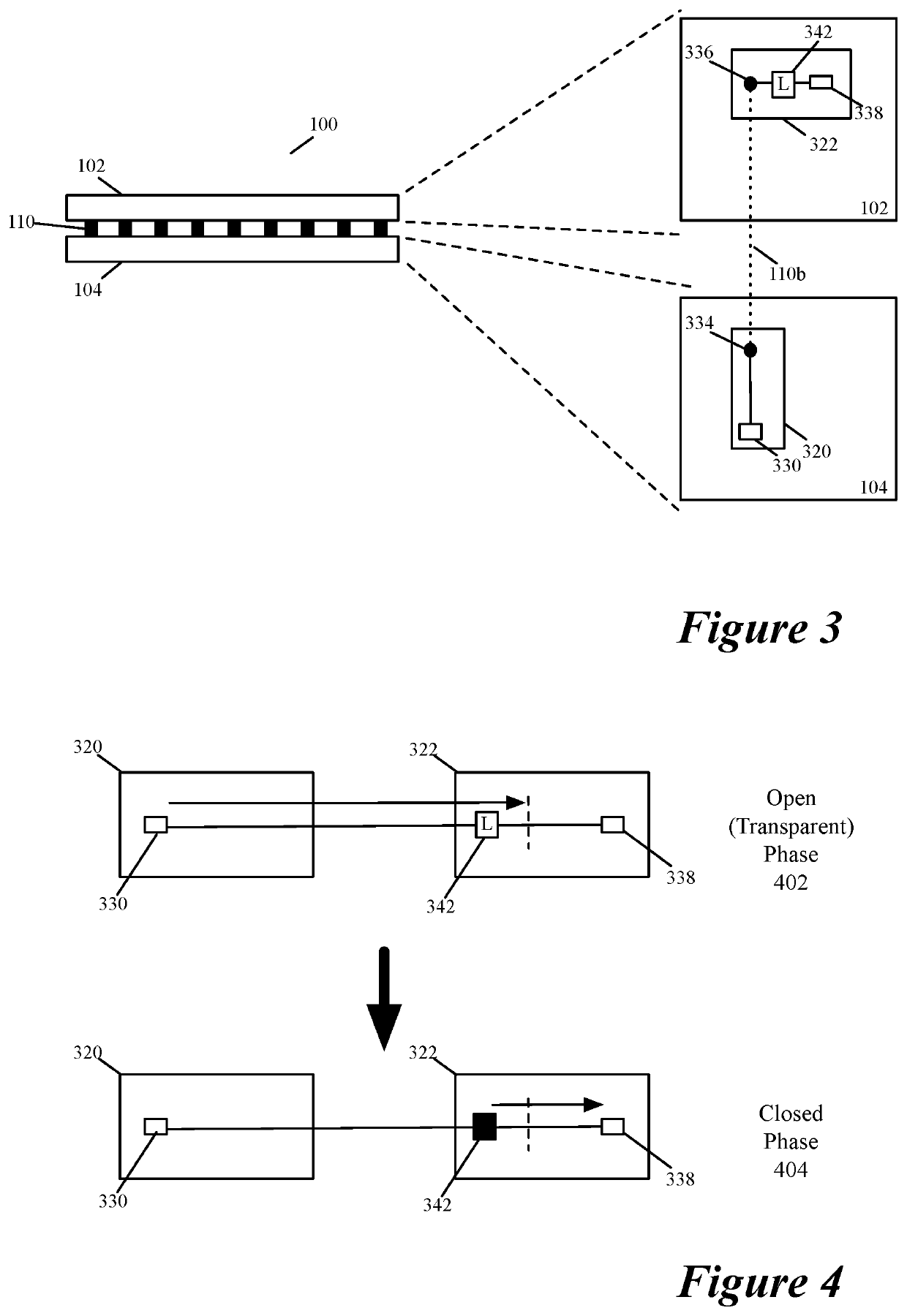

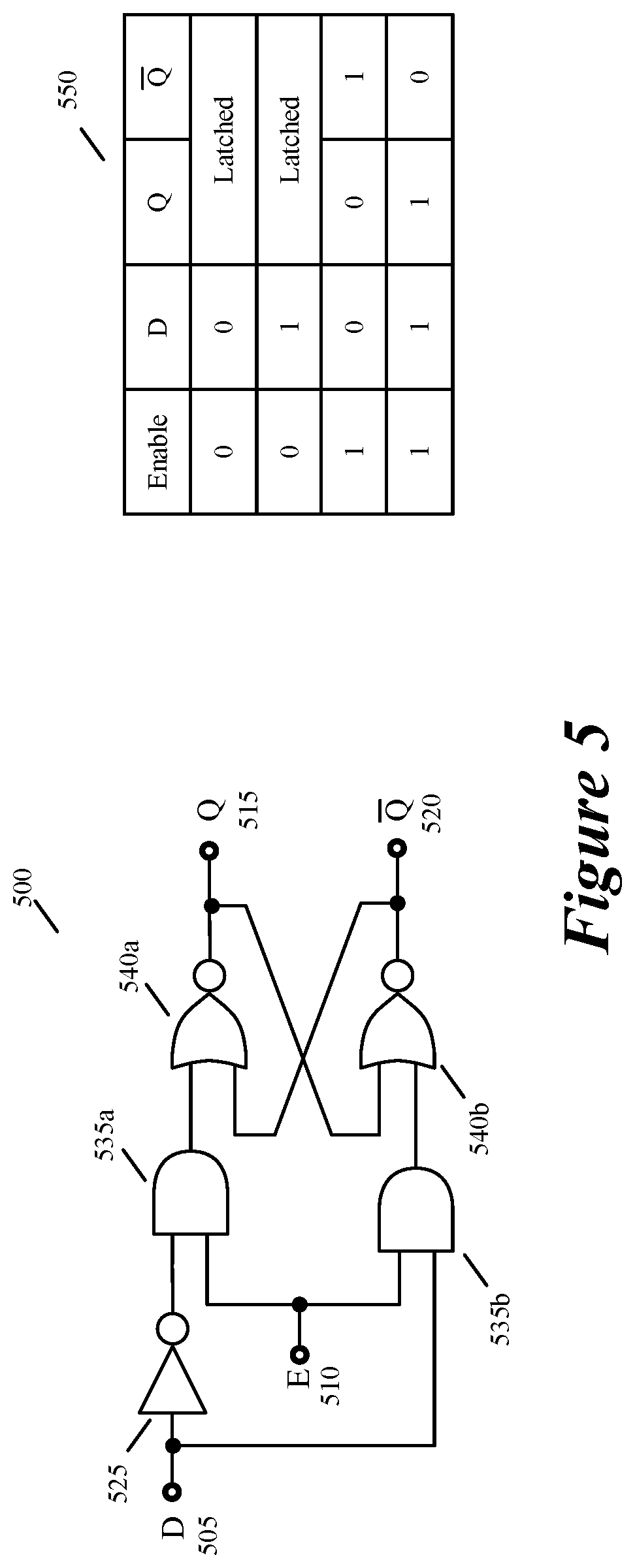

Time borrowing between layers of a three dimensional chip stack

ActiveUS20190042912A1Reduce loadExclusive-OR circuitsError detection/correctionEngineeringThree-dimensional integrated circuit

Some embodiments of the invention provide a three-dimensional (3D) circuit structure that uses latches to transfer signals between two bonded circuit layers. In some embodiments, this structure includes a first circuit partition on a first bonded layer and a second circuit partition on a second bonded layer. It also includes at least one latch to transfer signals between the first circuit partition on the first bonded layer and the second circuit partition on the second bonded layer. In some embodiments, the latch operates in (1) an open first mode that allows a signal to pass from the first circuit partition to the second circuit partition and (2) a closed second mode that maintains the signal passed through during the prior open first mode. By allowing the signal to pass through the first circuit partition to the second circuit partition during its open mode, the latch allows the signal to borrow time from a first portion of a clock cycle of the second circuit partition for a second portion of the clock cycle of the second circuit partition.

Owner:XCELSIS CORP

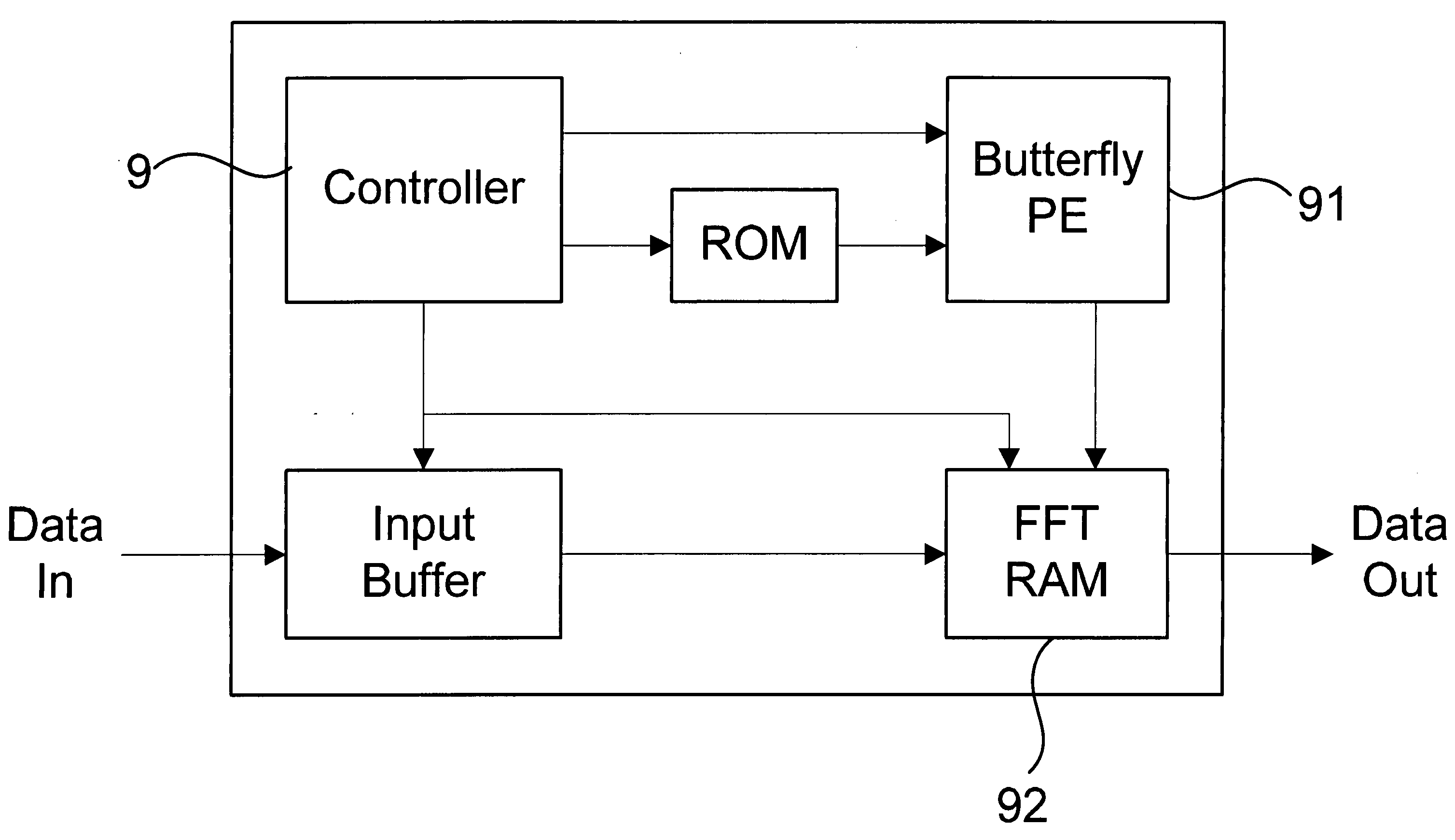

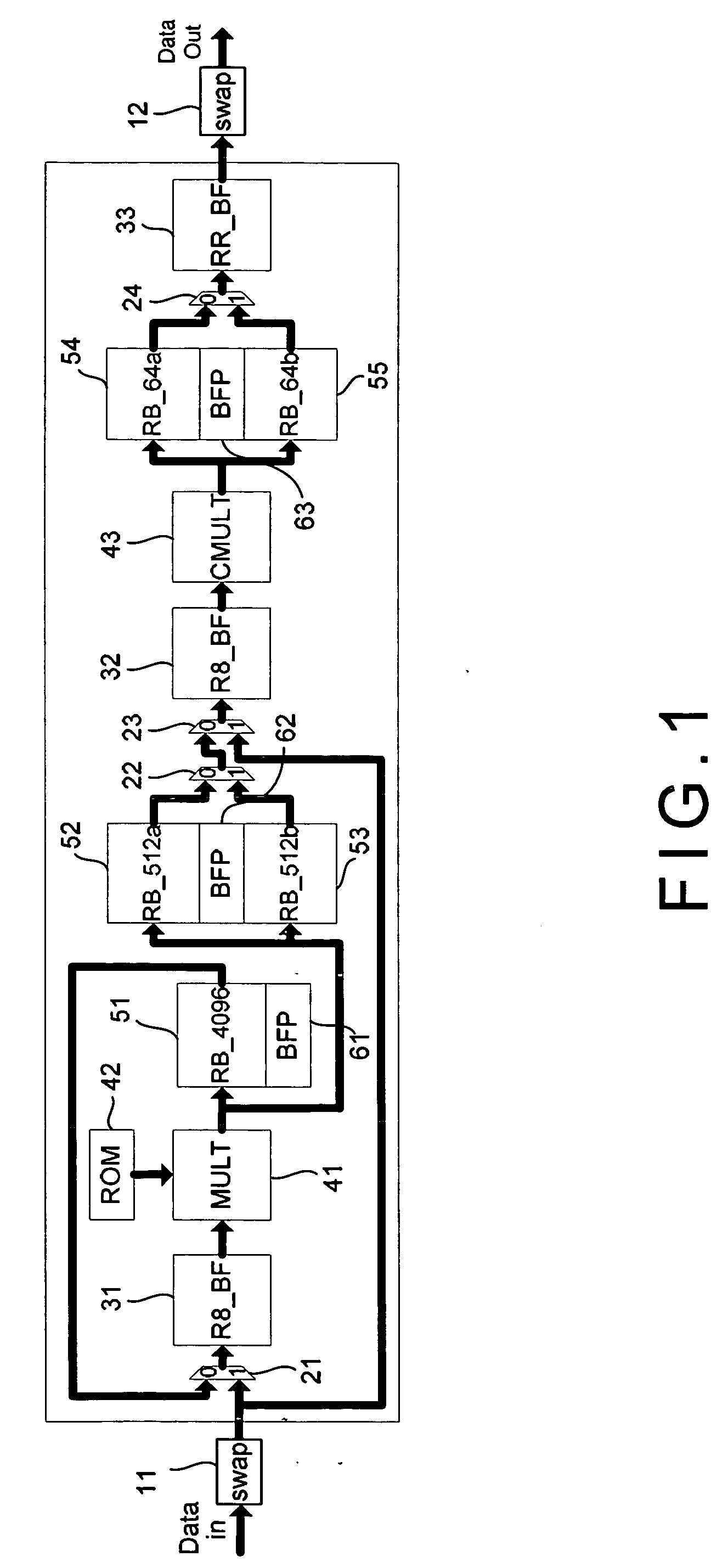

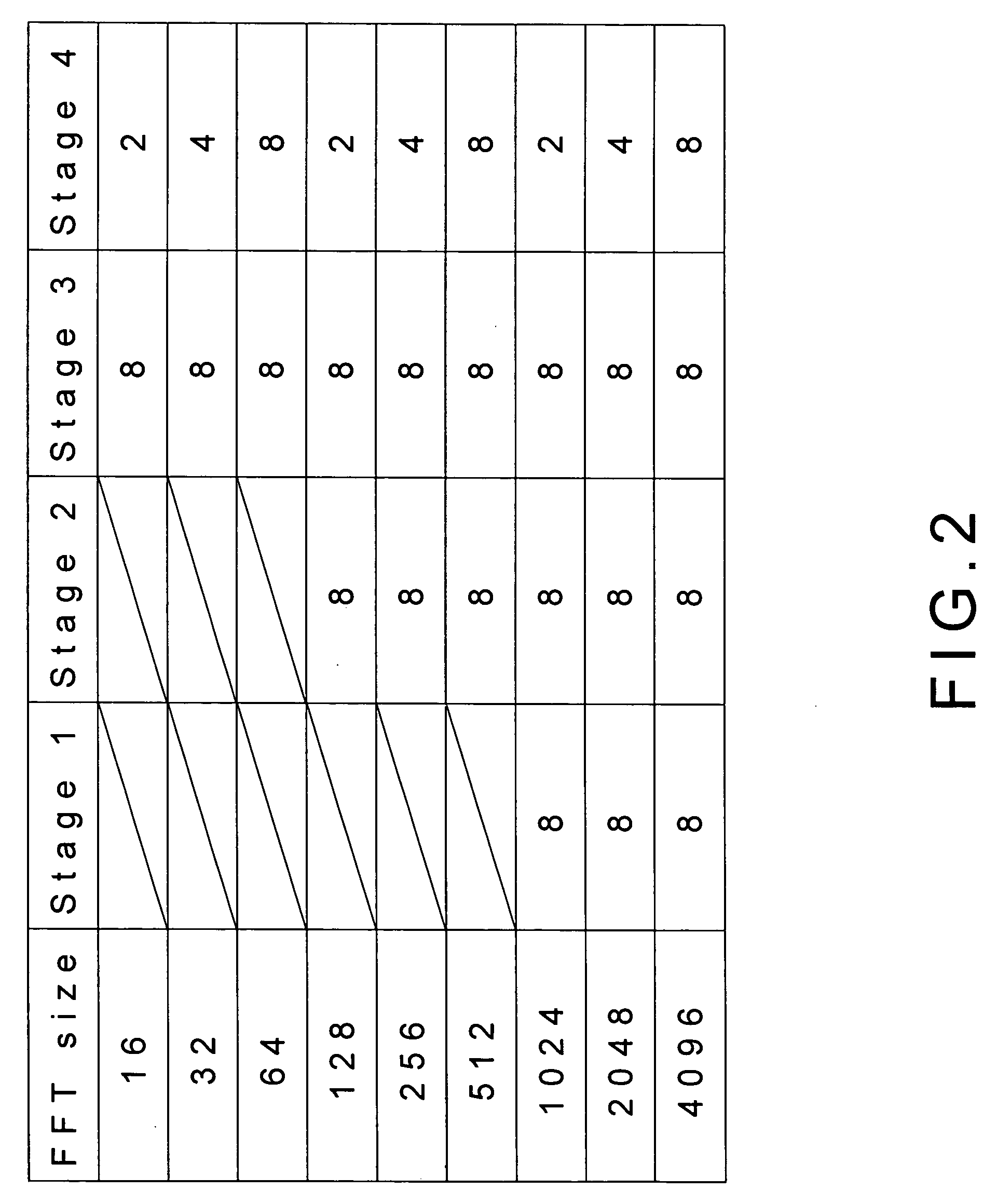

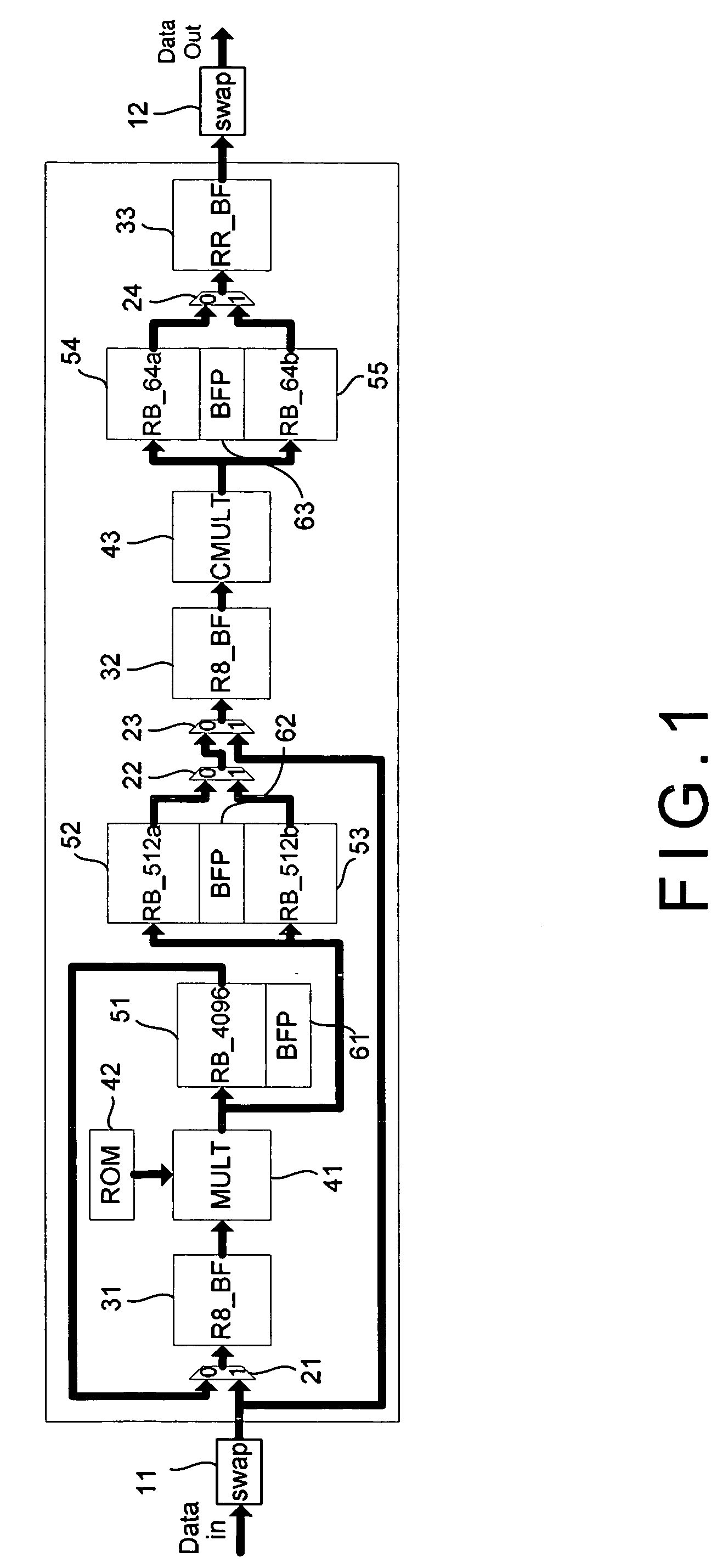

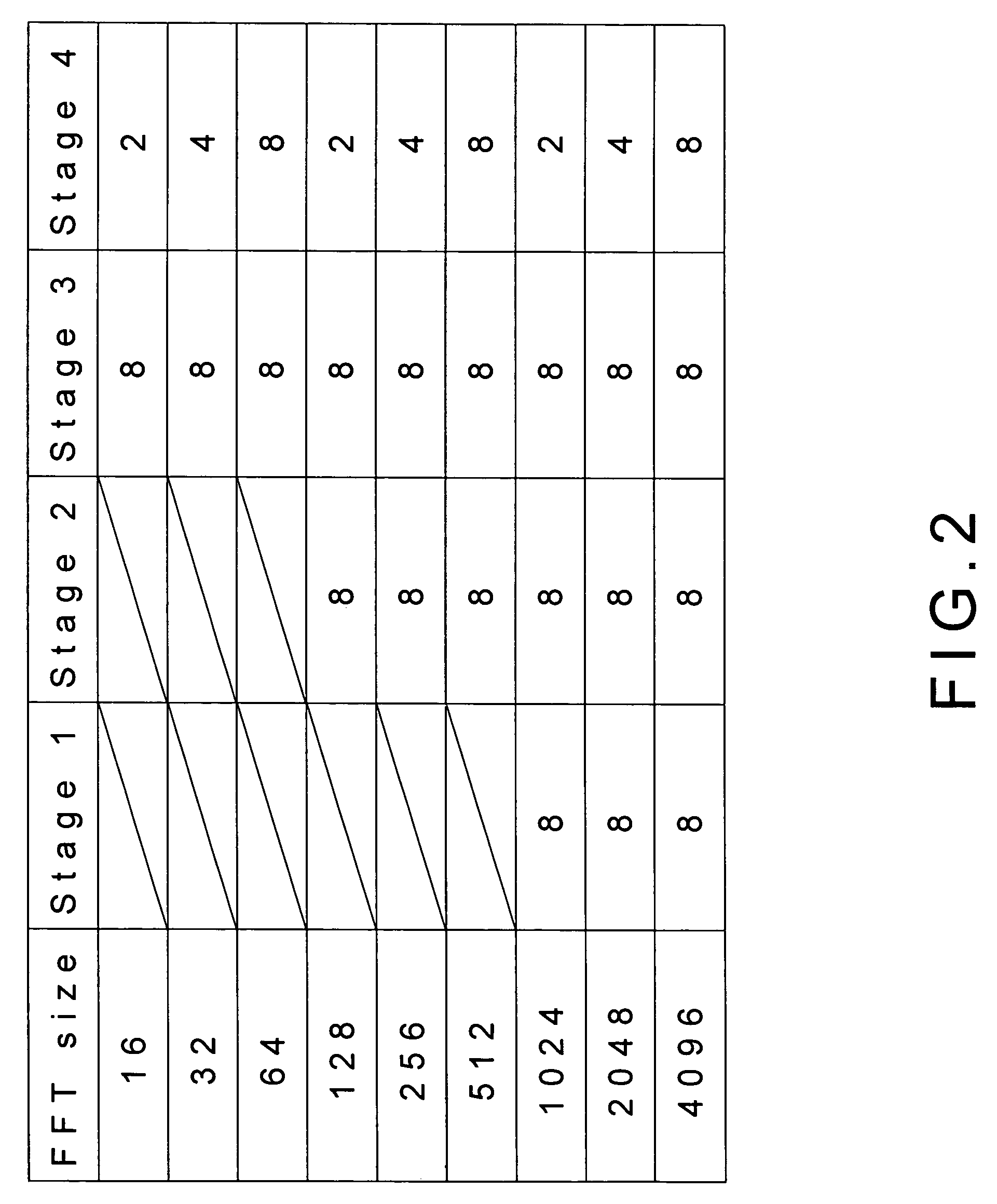

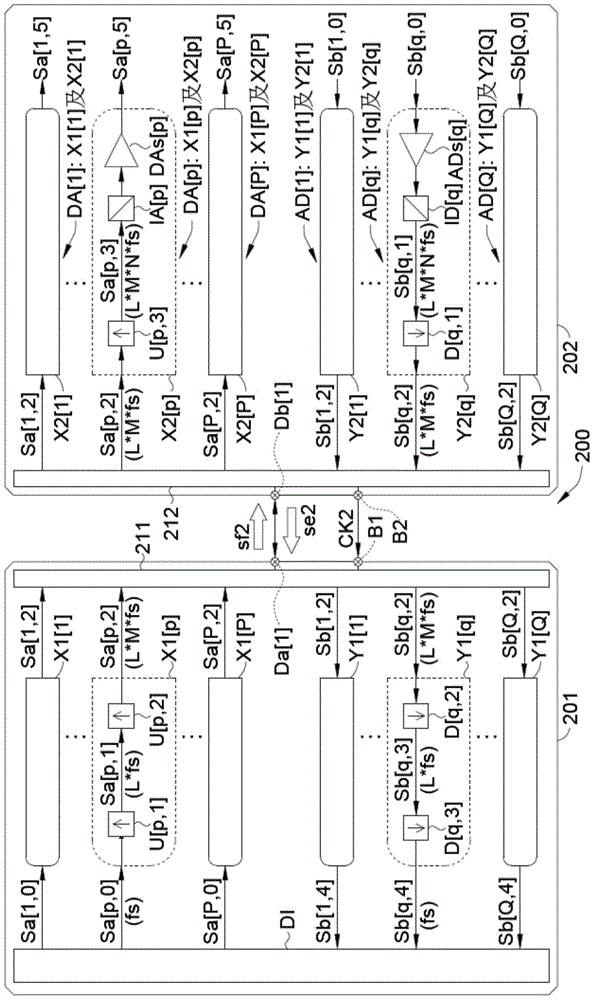

Pipeline-based reconfigurable mixed-radix FFT processor

ActiveUS20080155003A1Reduce computing time costsReduce hardware costsDigital computer detailsComplex mathematical operationsSignal-to-noise ratio (imaging)Block floating-point

The present invention discloses a fast Fourier transform (FFT) processor based on multiple-path delay commutator architecture. A pipelined architecture is used and is divided into 4 stages with 8 parallel data path. Yet, only three physical computation stages are implemented. The process or uses the block floating point method to maintain the signal-to-noise ratio. Internal storage elements are required in the method to hold and switch intermediate data. With good circuit partition, the storage elements can adjust their capacity for different modes, from 16-point to 4096-point FFTs, by turning on or turning off the storage elements.

Owner:NAT CHIAO TUNG UNIV

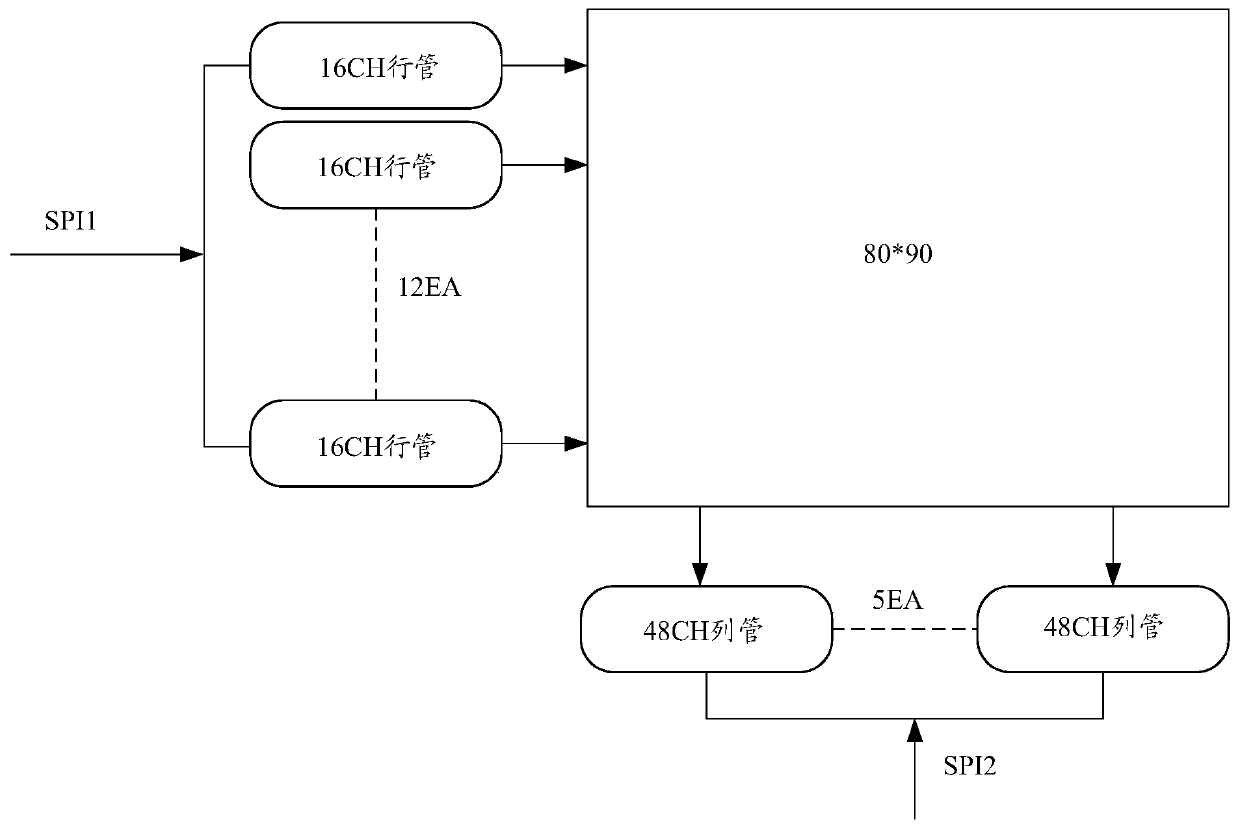

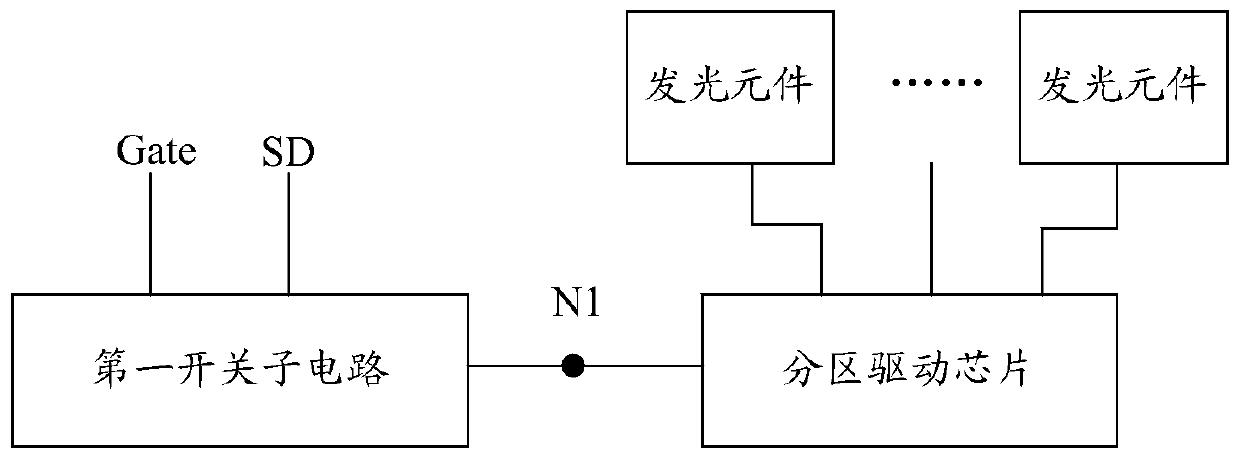

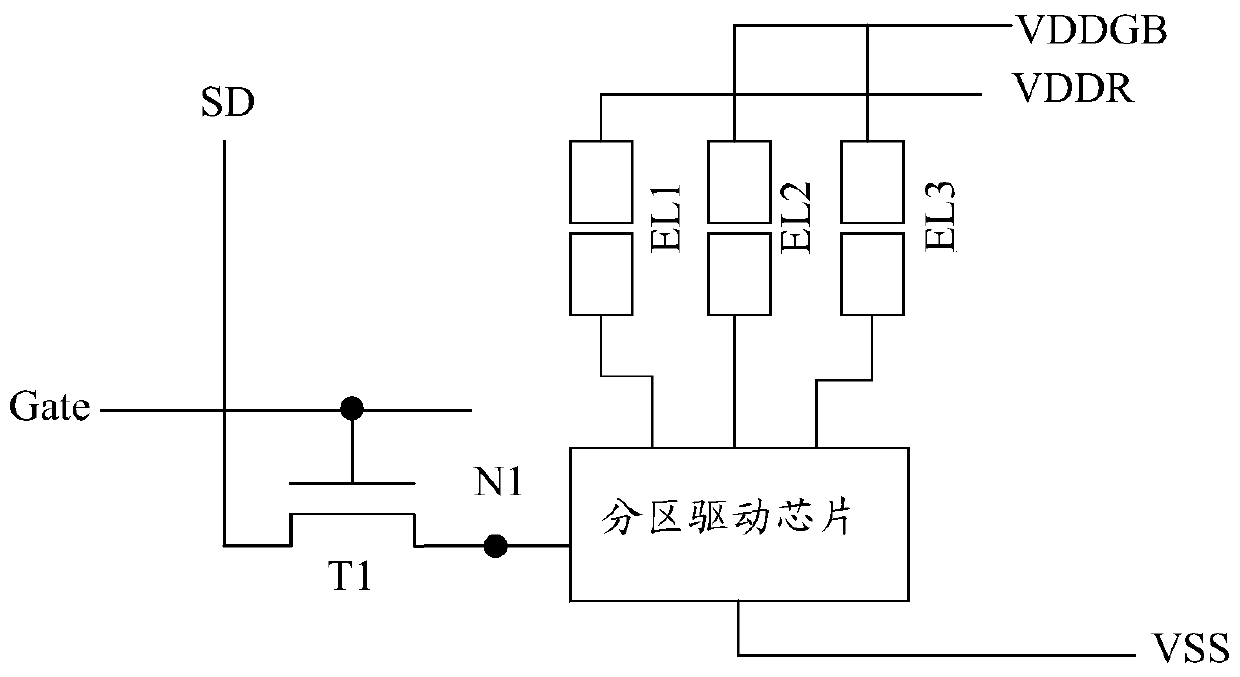

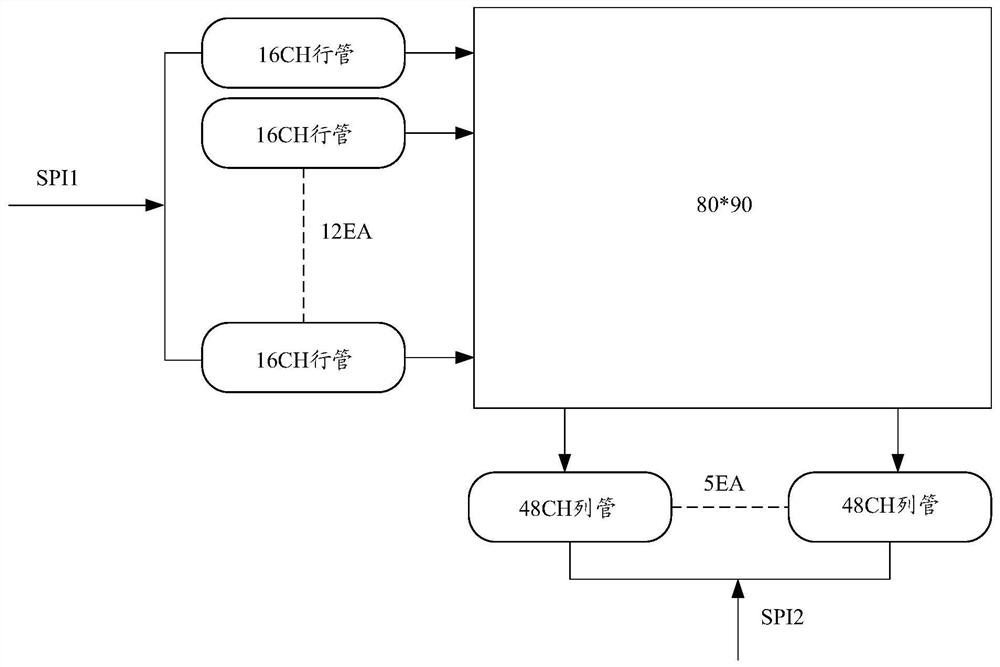

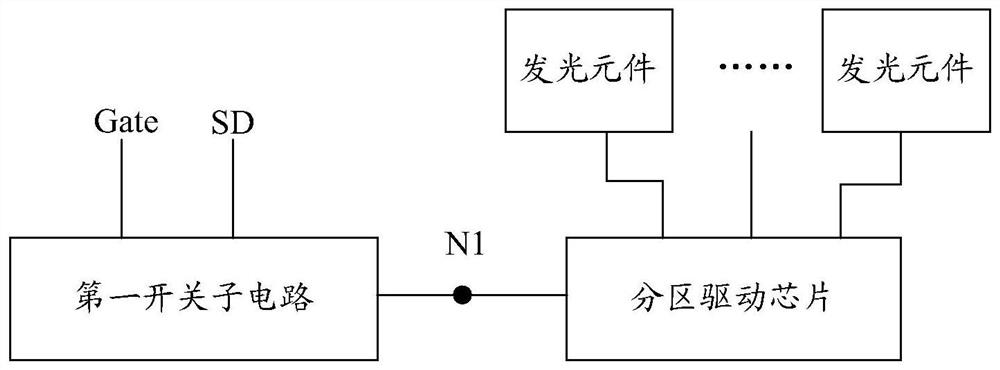

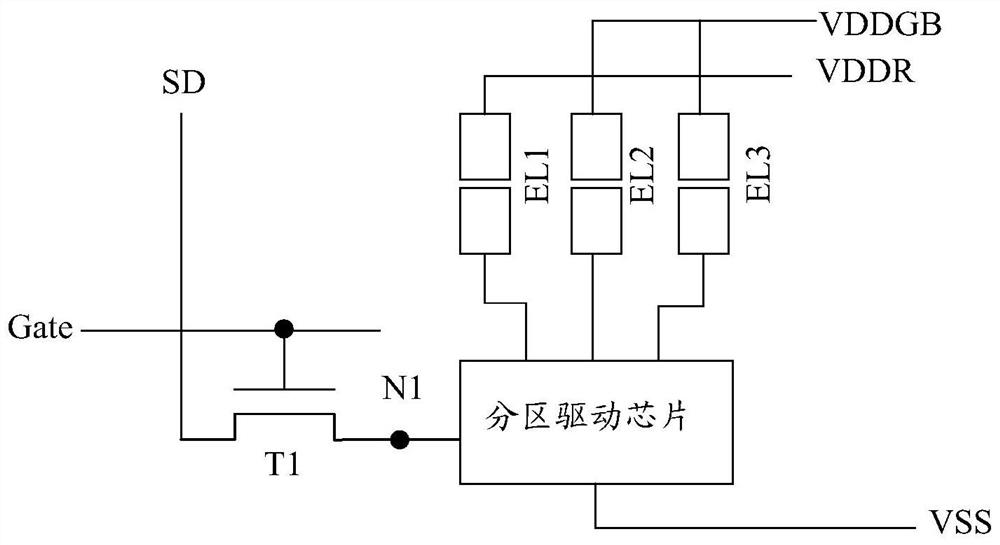

Pixel circuit, driving method thereof and display device

ActiveCN111243496AReduce the number of tracesReduce drive power consumptionStatic indicating devicesScan lineDisplay device

The invention discloses a pixel circuit, a driving method thereof and a display device. The pixel circuit comprises a first switch sub-circuit, a partition driving chip and a plurality of light-emitting elements. The first switch sub-circuit is respectively connected with a scanning line, a data line and a first node and is used for writing a data voltage signal of the data line into the first node under the control of the scanning line; and the partition driving chip is connected with the first node and the plurality of light-emitting elements respectively and is used for judging driving timecorresponding to each light-emitting element according to a data voltage signal input by the first node, and driving the light-emitting elements to emit light by using the data voltage signal withinthe corresponding driving time. Active site selection driving is realized through the first switch sub-circuit and the partition driving chip, so that the number of glass-based wires is effectively reduced, the difficulty of a side edge wire routing process is greatly reduced, the driving power consumption and the driving cost of the whole display module are reduced, and the competitive advantageof a product is greatly improved.

Owner:BOE TECH GRP CO LTD +1

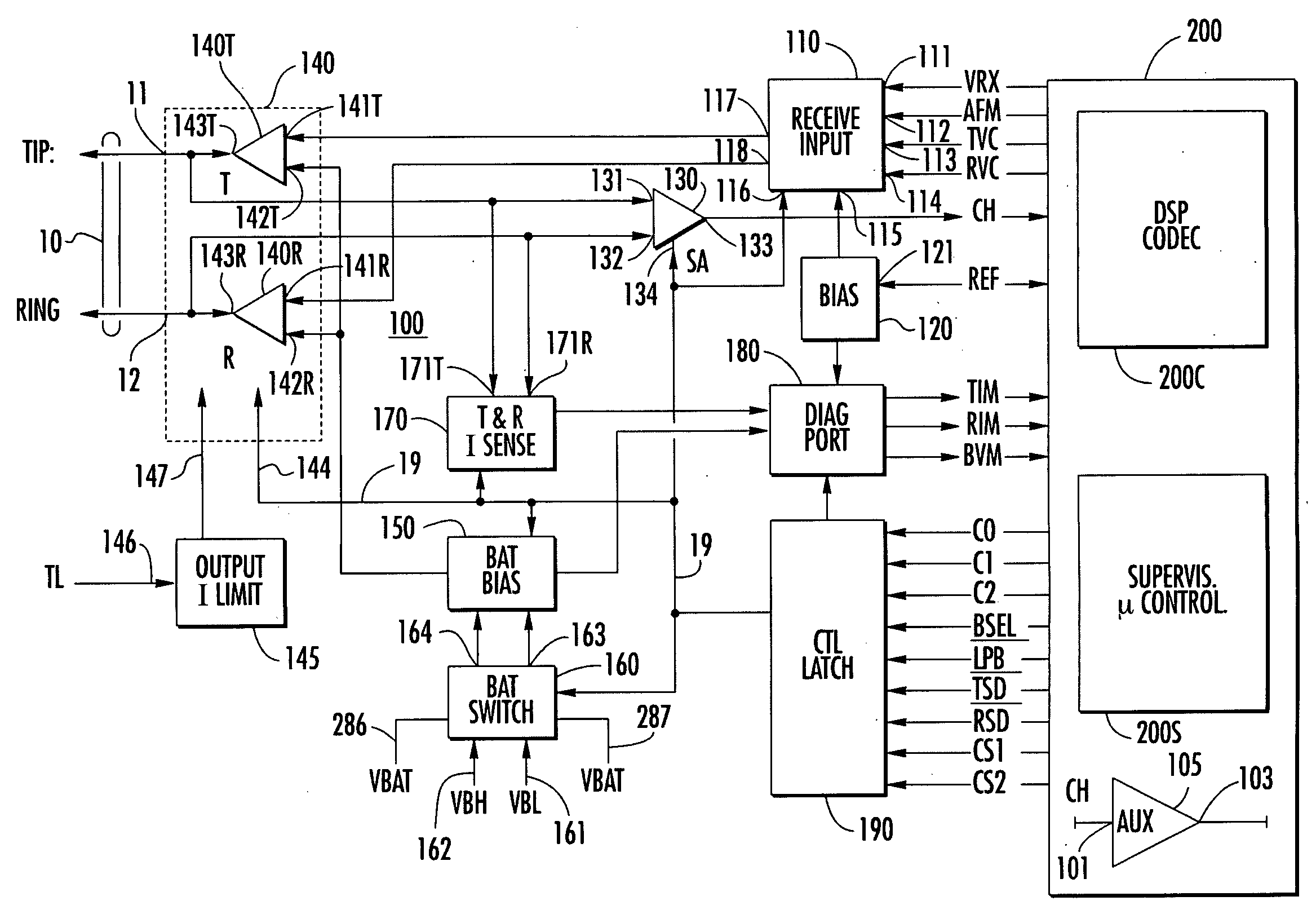

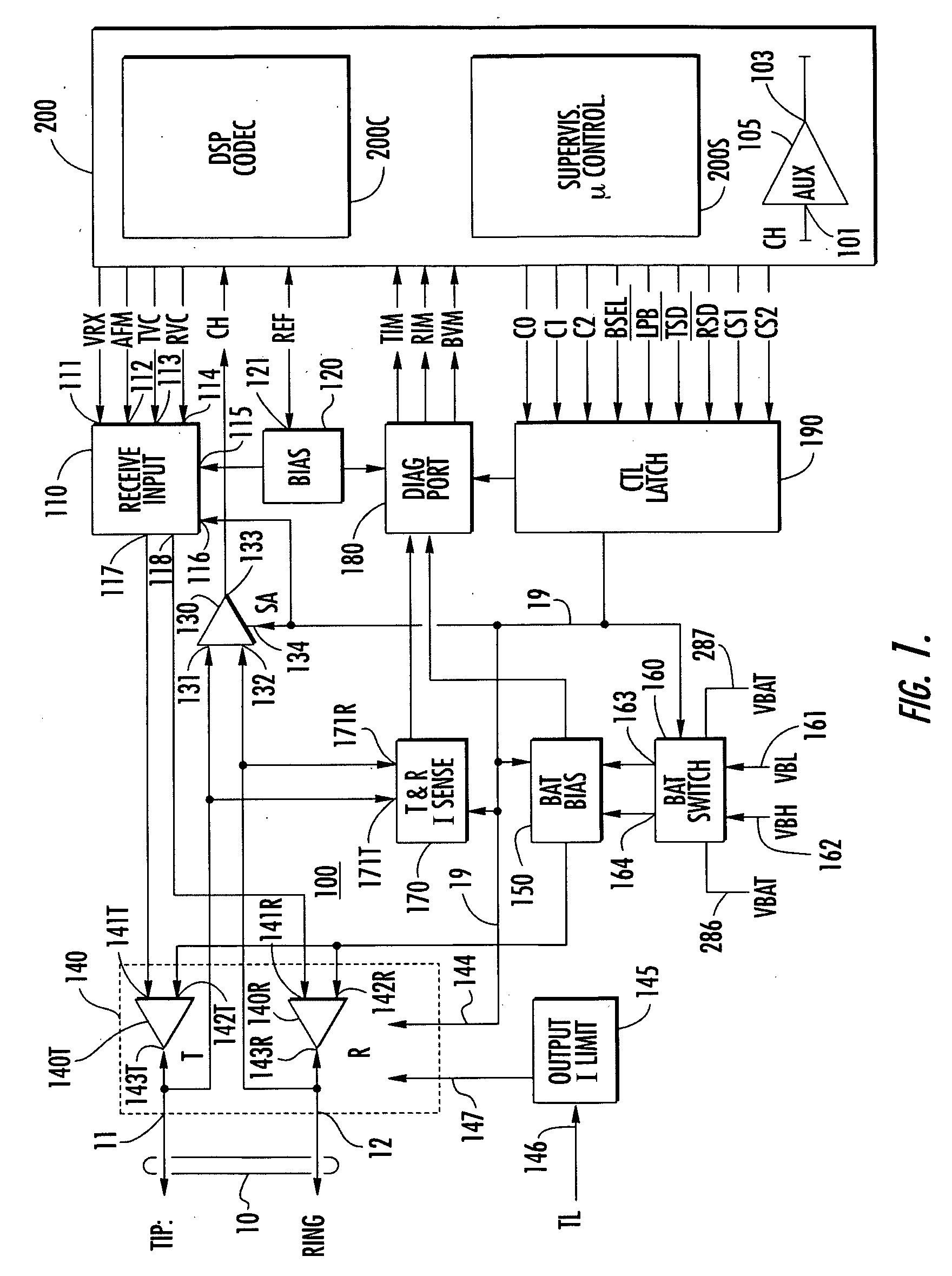

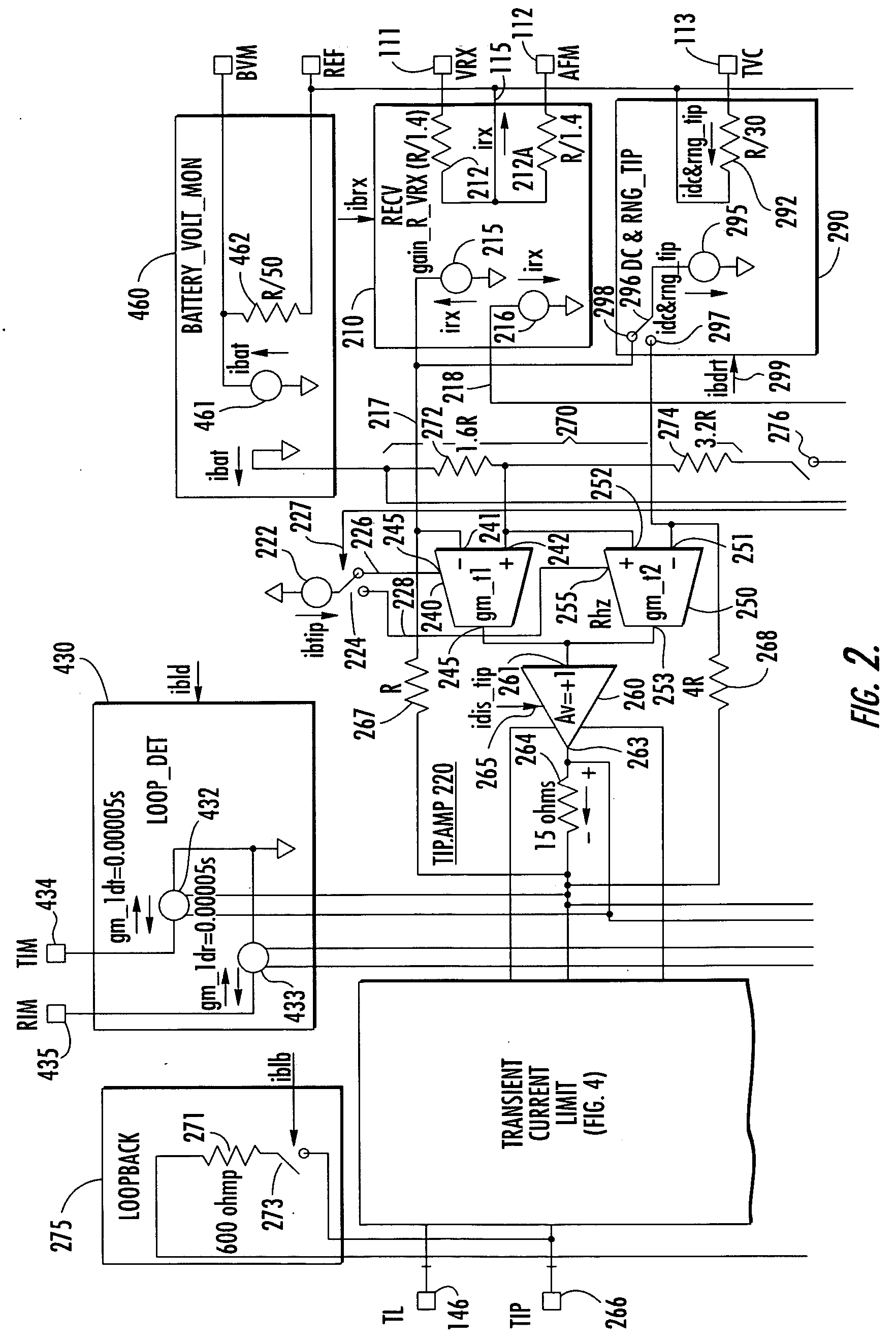

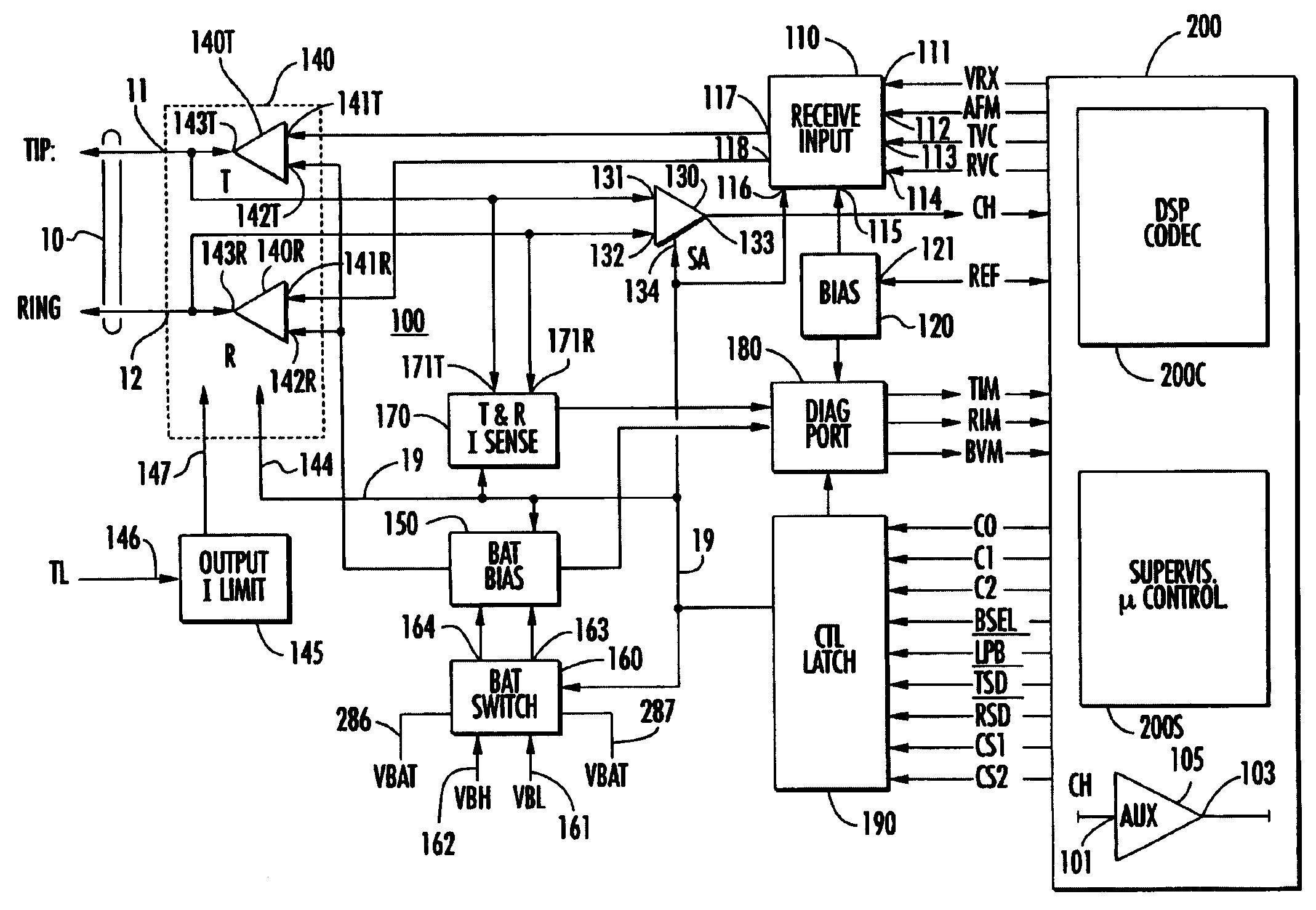

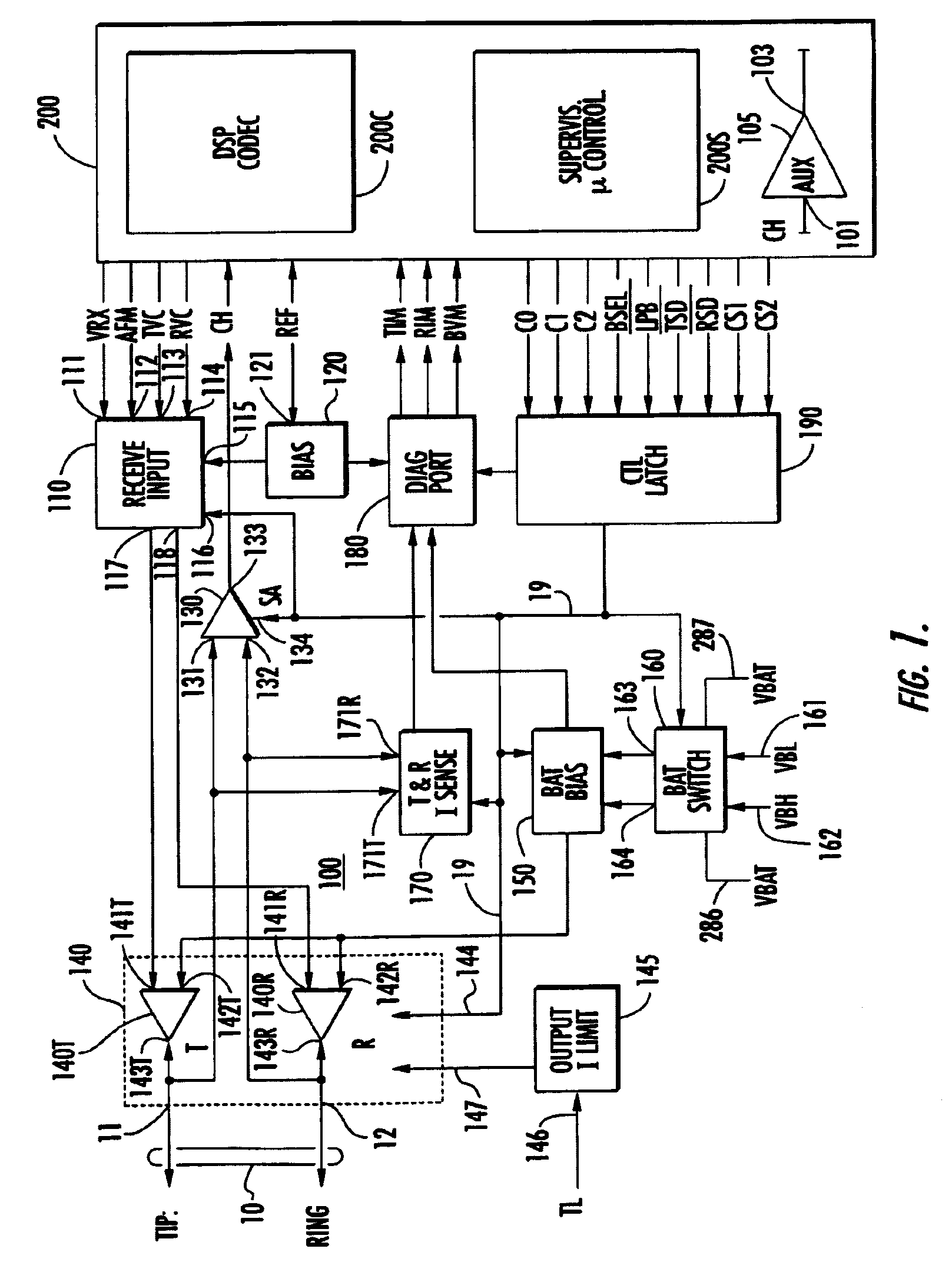

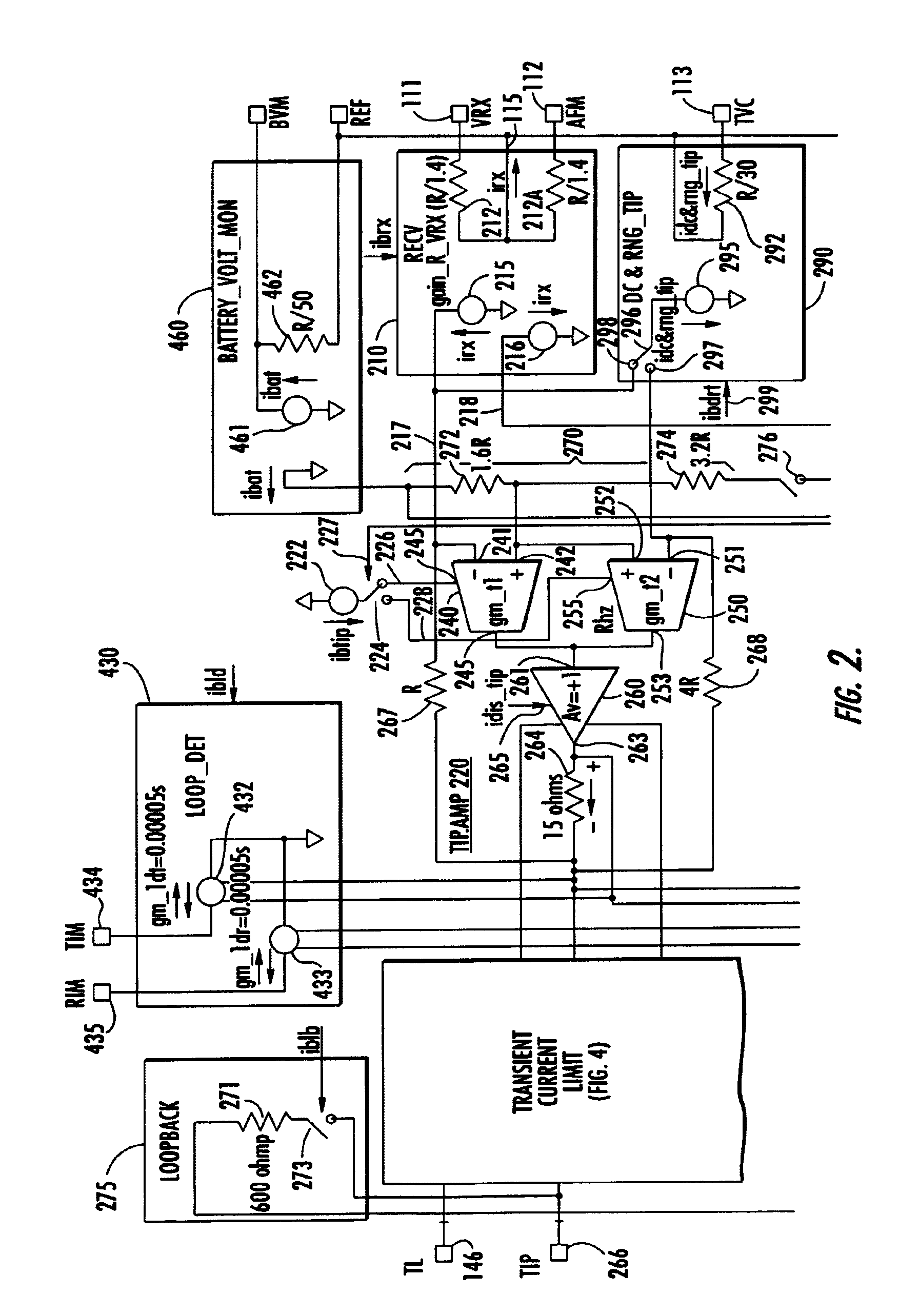

Programmable subscriber line circuit partitioned into high voltage interface and digital control subsections

InactiveUS20060115076A1Avoid flowSubstations coupling interface circuitsInterconnection arrangementsDigital signal processingLow voltage

A subscriber line interface circuit has a battery-powered, high voltage analog section, that drives tip and ring lines of a subscriber loop, and a mixed signal (low voltage and digital signal processing) section, that monitors and controls the high voltage analog section. An input signal receiving unit of the high voltage analog section conditions input voice and low voltage signaling and ringing signals from the mixed signal section, for application to a dual mode, programmable gain, tip / ring amplifier coupled to the loop. A sense amplifier at the output of the tip / ring amplifier is through an auxiliary amplifier to an analog feedback monitor port for closing a loop to synthesize the circuit's output impedance.

Owner:INTERSIL INC

Time borrowing between layers of a three dimensional chip stack

ActiveUS10607136B2Reduce loadExclusive-OR circuitsSemiconductor/solid-state device detailsComputer hardwareHemt circuits

Owner:XCELSIS CORP

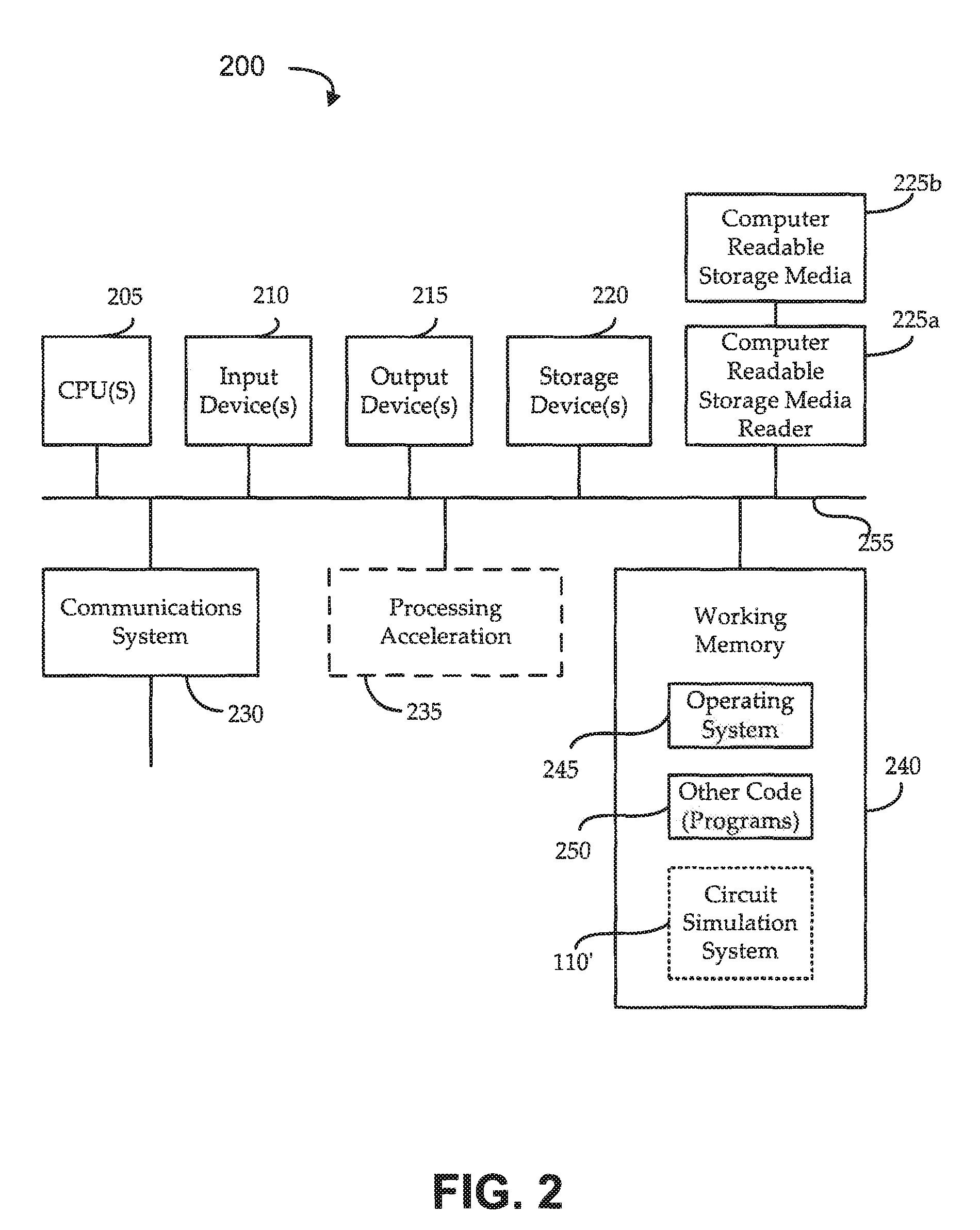

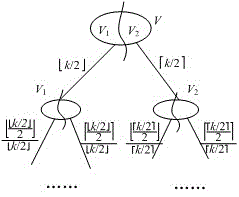

Circuit partitioning method for parallel circuit simulation

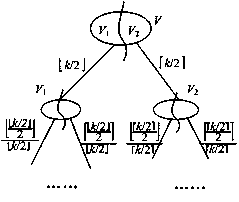

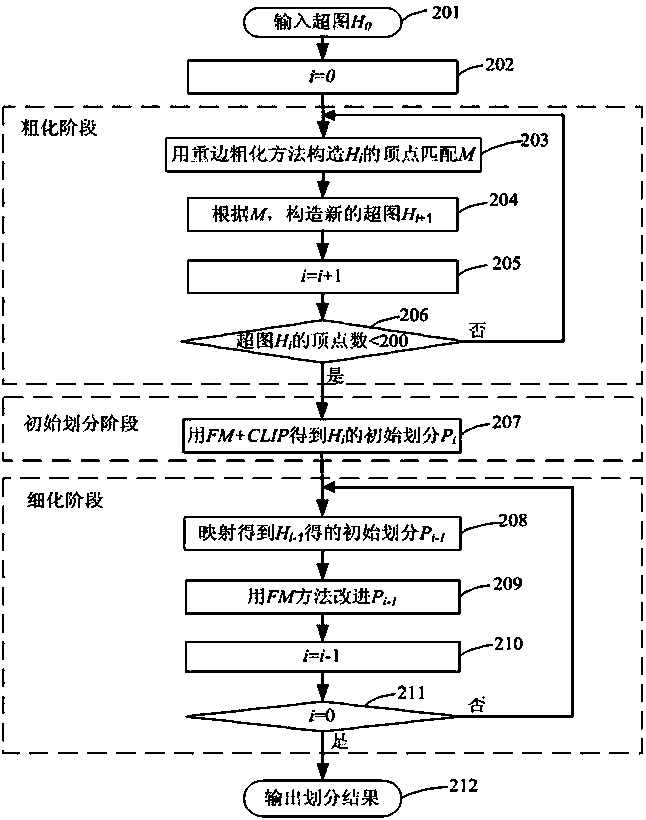

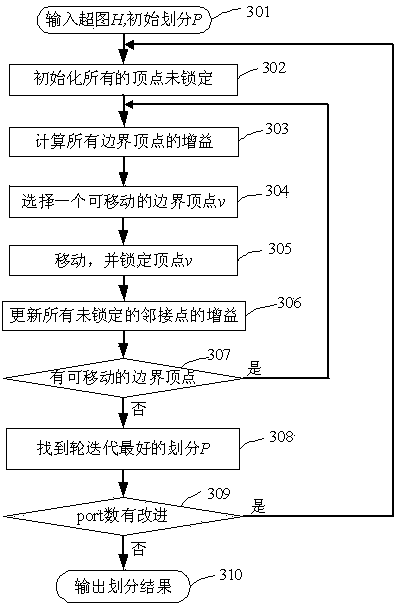

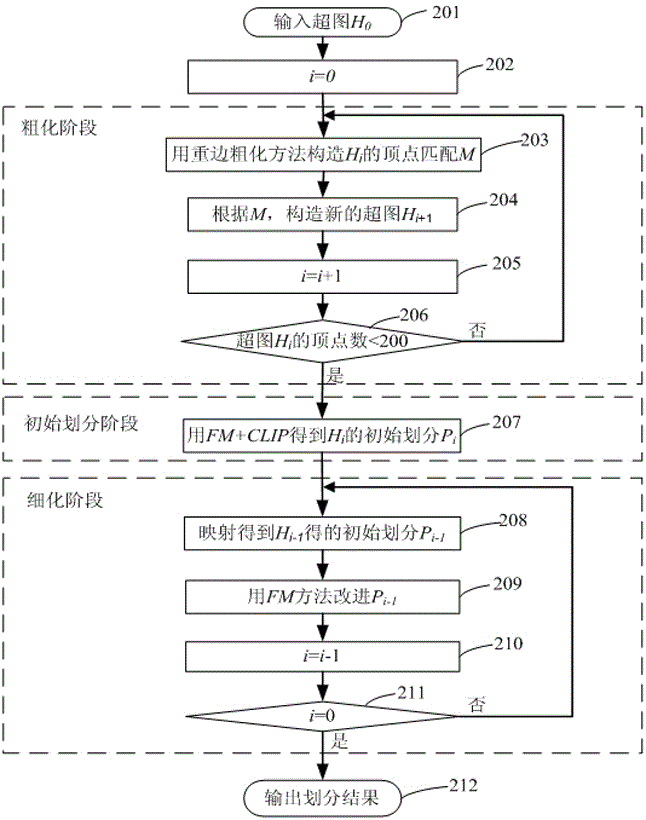

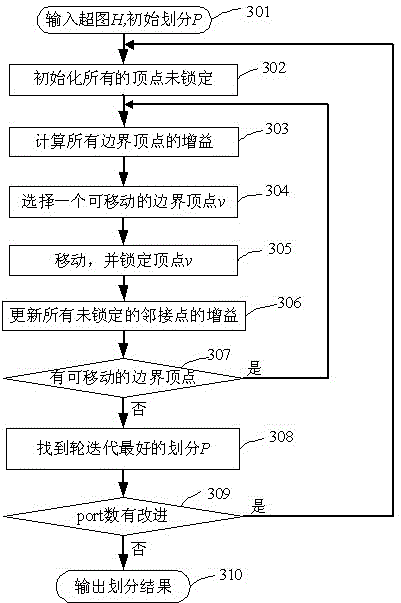

InactiveCN103353910AThe number of ports is goodGood for load balancingSpecial data processing applicationsVery large scale integrated circuitsComputer science

The invention provides a circuit partitioning method for parallel circuit simulation, and belongs to the technical field of very large scale integration (VLSI) circuit design automation. The method comprises the steps as follows: better initial partition is rapidly acquired with a recursive multistage two-way partition method taking minimum cut as a target; and then minimum communication traffic and load balancing are taken as targets, and the partition is continuously improved with an iteration improvement method. The technical scheme is as follows: 1), a k-route initial partition is acquired with the recursive two-way partition method; 2), the two-way partition is performed with a multistage partition method, wherein at a roughening stage, load balancing is combined, and at an elaboration stage, iterations are limited; and 3), in an iteration improvement process, a peak which can improve the load balancing is selected to be moved preferentially each time. According to the method, an obtained partition result meets the requirements of the load balancing and less communication traffic, and the method is applicable to a circuit partition stage of an VLSI parallel circuit simulation system.

Owner:FUZHOU UNIV

Pipeline-based reconfigurable mixed-radix FFT processor

ActiveUS7849123B2Low costShorten the timeDigital computer detailsComplex mathematical operationsSignal-to-noise ratio (imaging)Block floating-point

The present invention discloses a fast Fourier transform (FFT) processor based on multiple-path delay commutator architecture. A pipelined architecture is used and is divided into 4 stages with 8 parallel data path. Yet, only three physical computation stages are implemented. The process or uses the block floating point method to maintain the signal-to-noise ratio. Internal storage elements are required in the method to hold and switch intermediate data. With good circuit partition, the storage elements can adjust their capacity for different modes, from 16-point to 4096-point FFTs, by turning on or turning off the storage elements.

Owner:NAT CHIAO TUNG UNIV

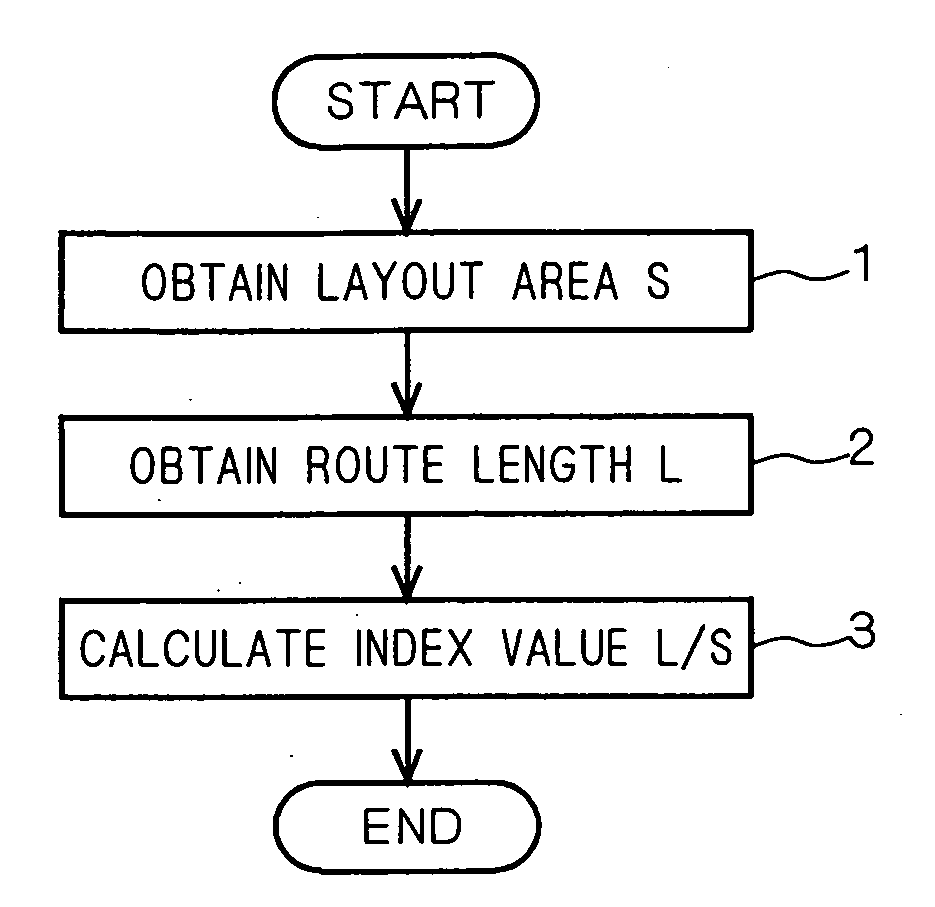

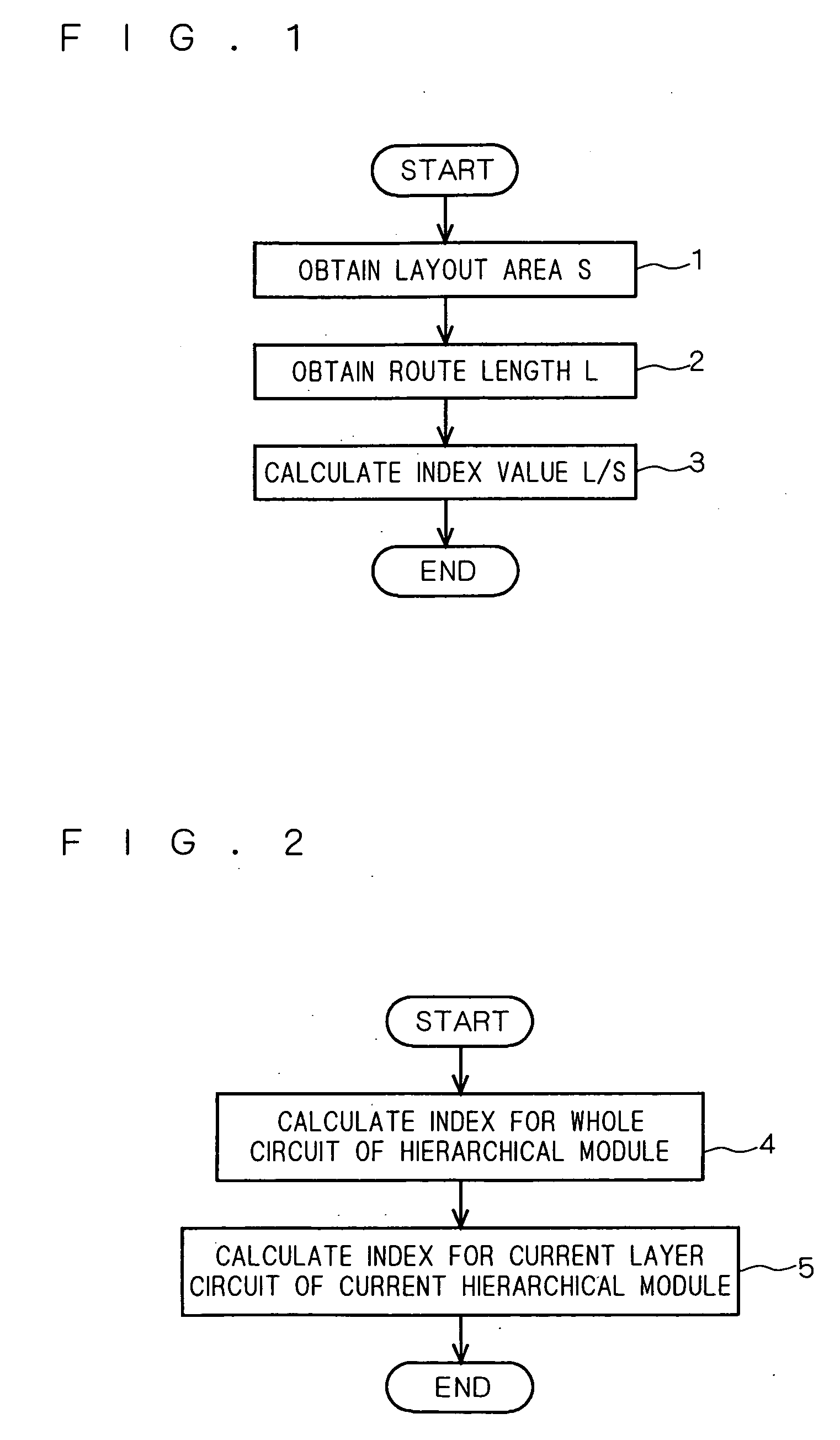

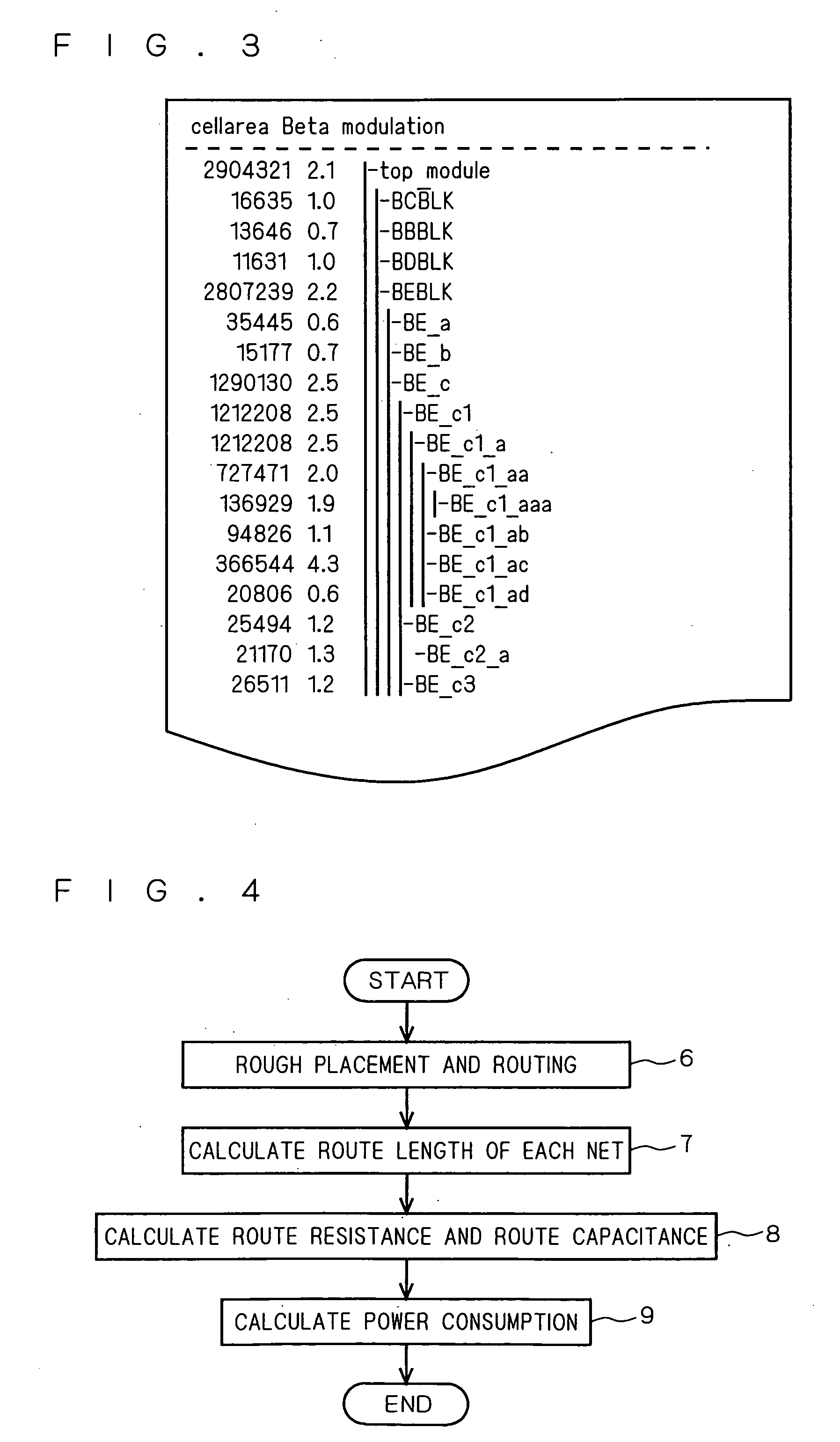

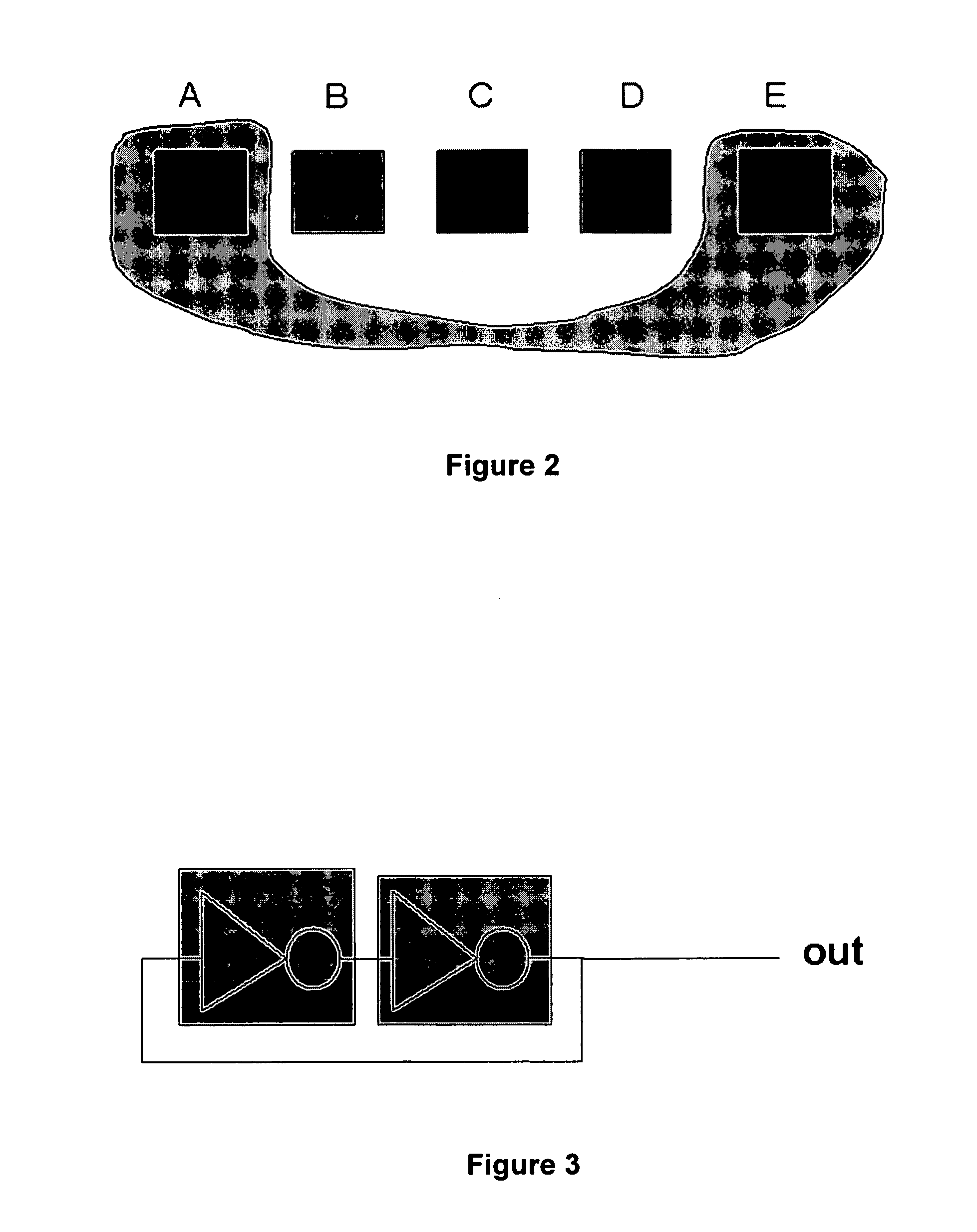

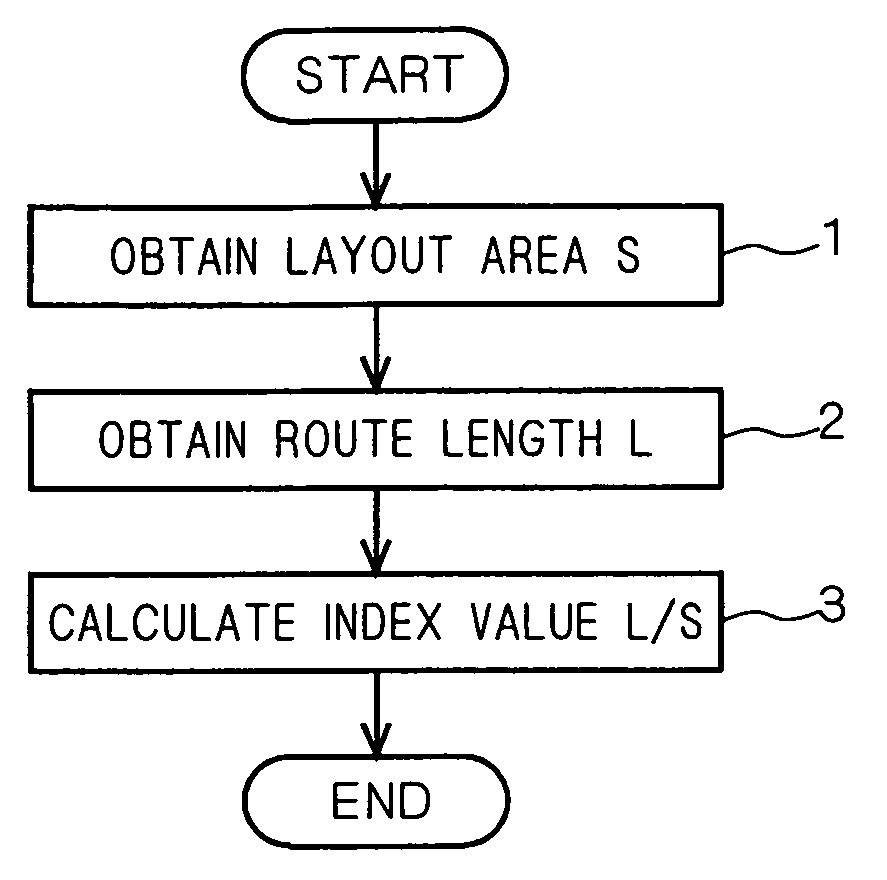

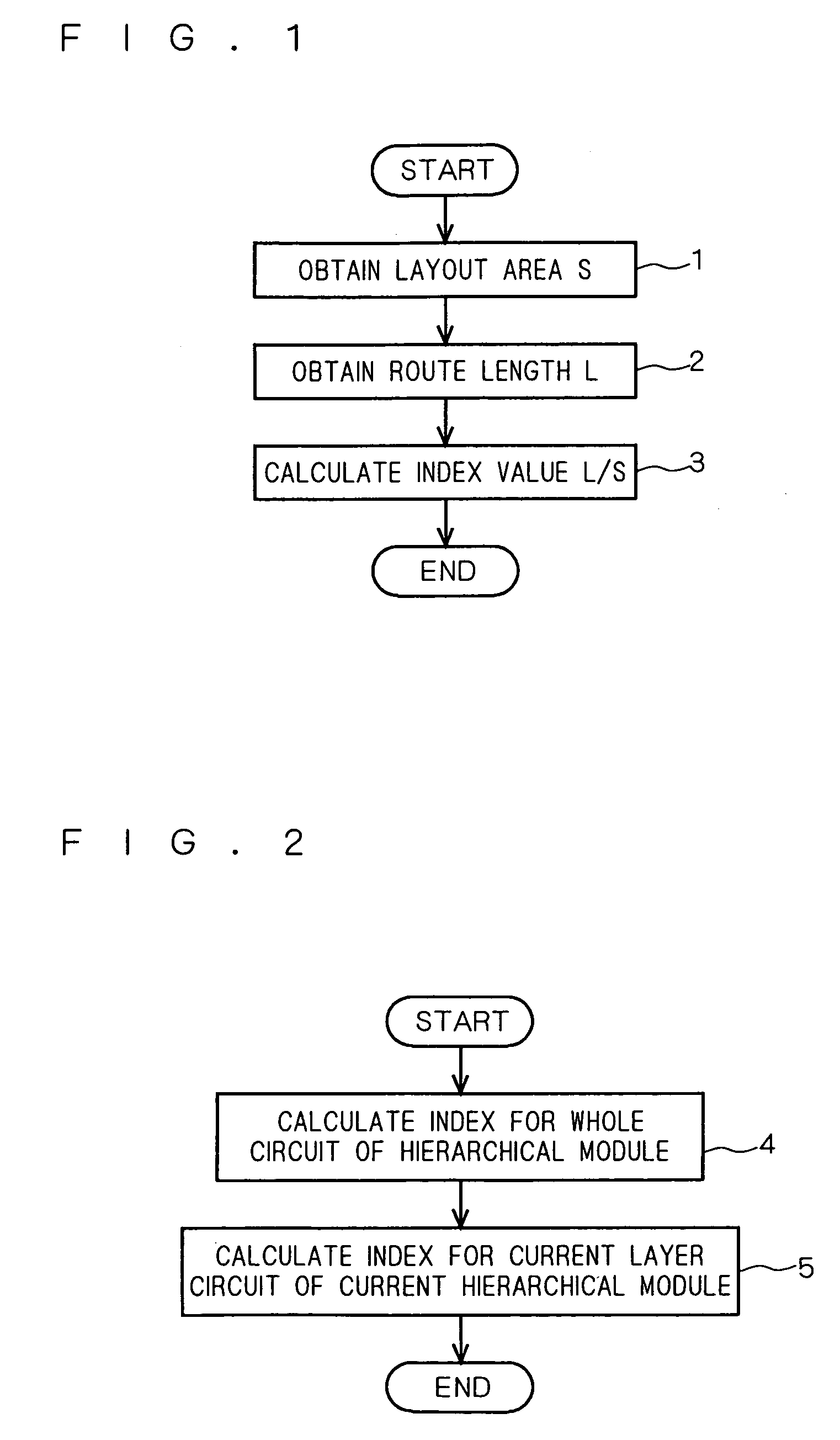

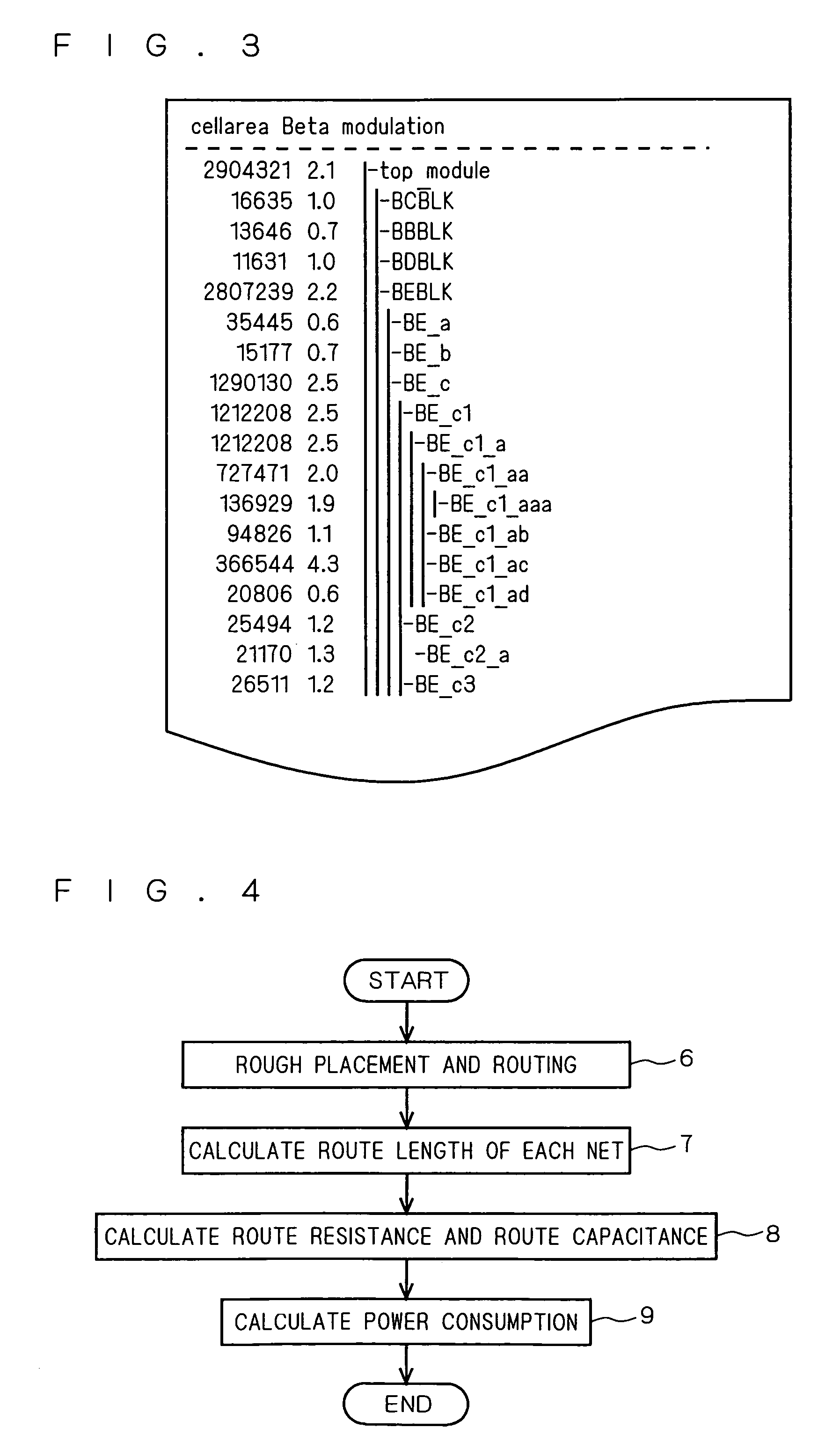

Routing analysis method, logic synthesis method and circuit partitioning method for integrated circuit

ActiveUS20050246676A1Improve forecast accuracyImprove accuracySemiconductor/solid-state device manufacturingComputer aided designAnalysis methodComputer science

The present invention relates to a routing analysis method for performing a routing analysis on an integrated circuit from a netlist which is information on a plurality of cells constituting the integrated circuit and routes connecting the cells, and the routing analysis method comprises a step (Step 1) of obtaining the sum of areas of a plurality of cells, the number of cells or the number of routes connecting the cells from the netlist, to be defined as a constant C, and calculating a layout area S which is an area of a square layout region, by dividing the constant C by a predetermined constant U, a step (Step 2) of calculating a total route length L by multiplying a half perimeter length H of the layout region having the layout area S obtained in Step 1 by a predetermined coefficient α, and a step (Step 3) of calculating a routing difficulty index by dividing the total route length L by the layout area S. Thus, the present invention provides a routing analysis method for an integrated circuit, which, allows calculation of routing difficulty index with high accuracy of prediction.

Owner:RENESAS ELECTRONICS CORP

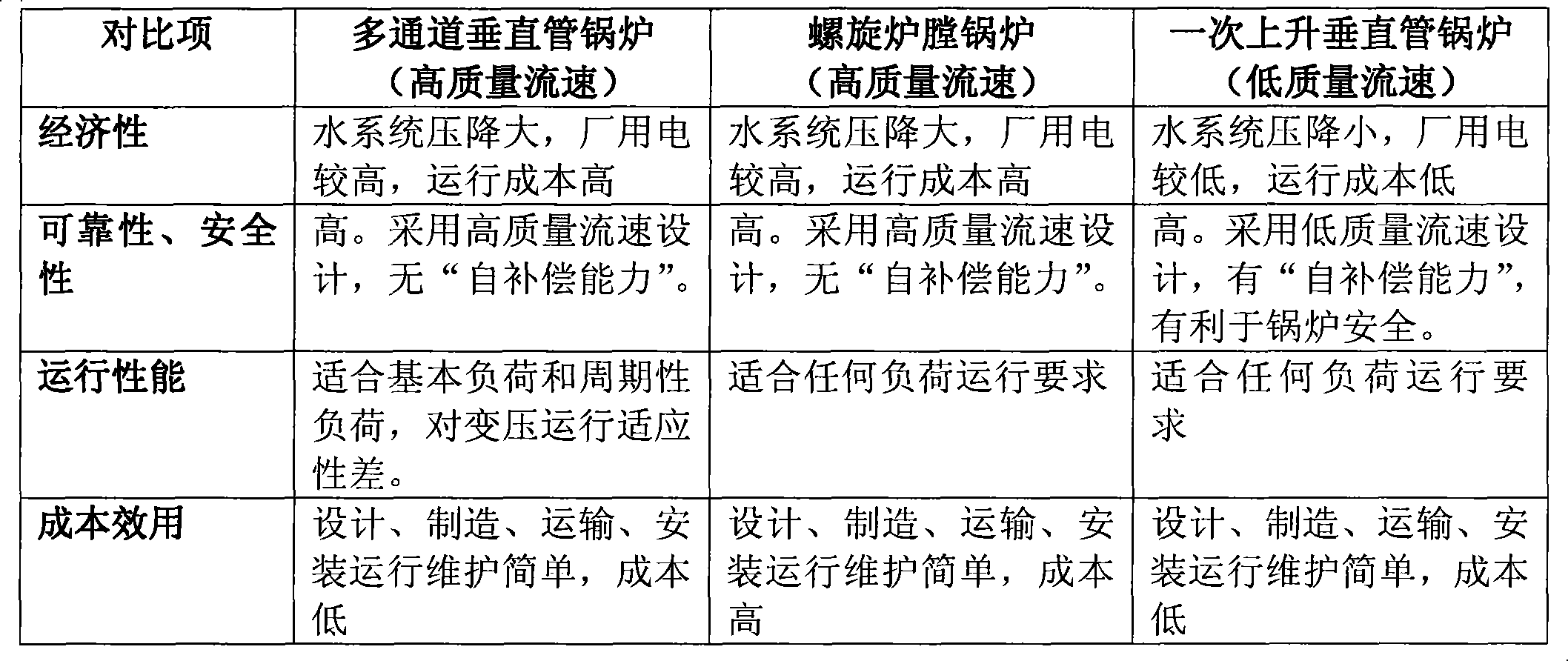

Design method of low mass flow velocity water circulation system for opposed firing boiler

InactiveCN103353104AOvercoming shortcomings in the designSafe and stable operationBoiler water tubesCombustion systemVertical tube

The invention relates to a design method of a low mass flow velocity water circulation system for an opposed firing boiler, which takes the following measures: a boiler adopts an n-shaped arrangement or a tower-shaped arrangement form; a boiler combustion system adopts an arrangement manner of multilayered combustors on front-back walls; a furnace chamber water wall process structure adopts a vertical tube water wall structure manner, the furnace chamber is divided into an upper part and a lower part, and a middle part is connected with a transition header; a furnace chamber water wall adopts an optimized internal thread pipe or a standard internal thread pipe; the boiler furnace hydrodynamic force is calculated under various load working conditions by a hydrodynamic force calculation model to determine the return circuit partition and a particular return circuit structural manner. The method adopts the low mass flow velocity designed similar to a subcritical boiler furnace chamber water circulation, and adopts the simple and feasible vertical tube water wall structure; the furnace chamber is divided into the upper part and the lower part, the middle part is connected with the transition header, and meanwhile the method ensures that the furnace chamber water wall can be sufficiently cooled under the low mass flow velocity condition to enable the boiler to carry out safe, stable, energy saving and efficient long-term running.

Owner:TRANSTEK IND HK LTD KOWLOON

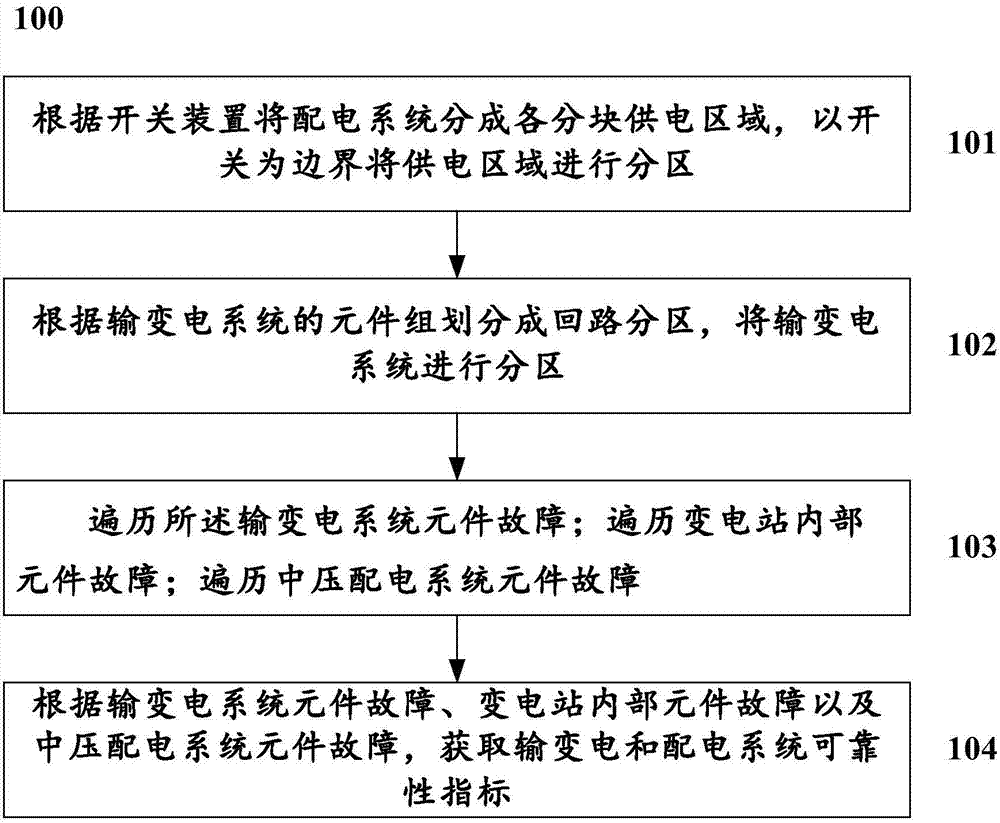

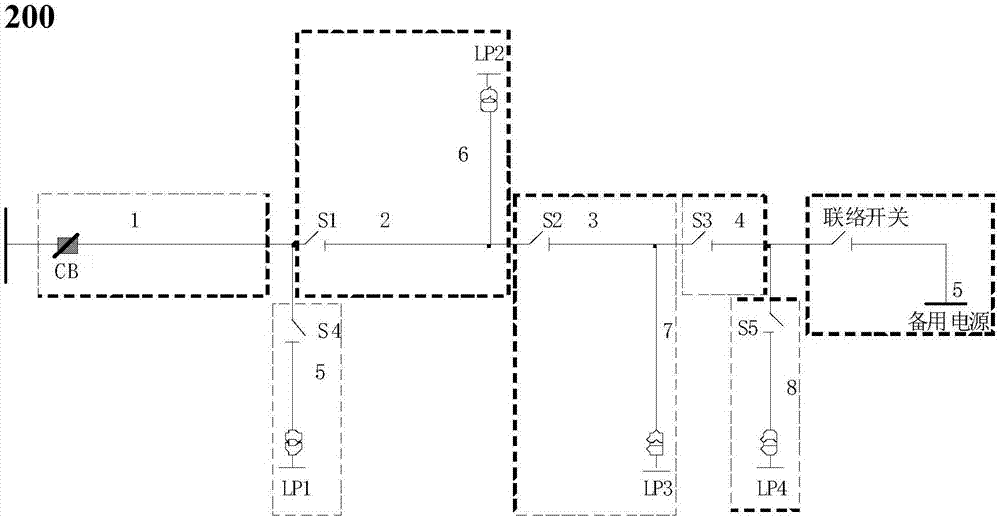

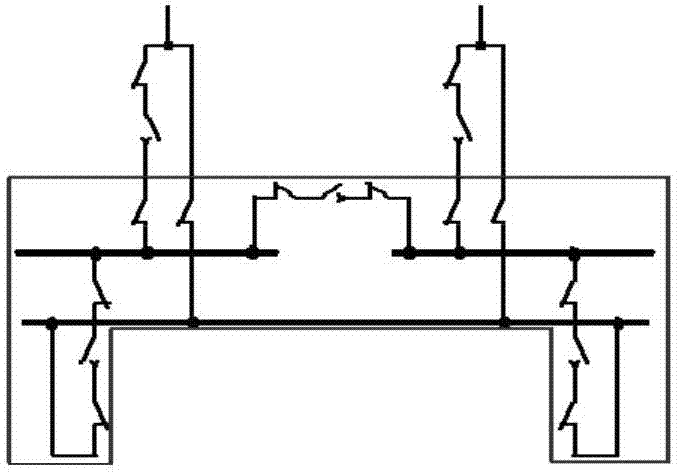

Method and system for cooperatively evaluating reliability of power transmission and transformation and power distribution system based on partition simplification

InactiveCN107196414AEmergency protective circuit arrangementsInformation technology support systemElectric power transmissionTransformer

The invention discloses a method and a system for cooperatively evaluating the reliability of a power transmission and transformation system and a power distribution system based on partition simplification. The method comprises the following steps: partitioning a power distribution system into partitioning power supply areas according to a switch device, and partitioning the power supply area by using the switch as a boundary; partitioning into circuit partitions according to a component group of the power transmission and transformation system, and partitioning the power transmission and transformation system; traversing component failures of the power transmission and transformation system; traversing failures of internal components of a transformer substation; traversing component failures of a middle-voltage power transmission system; and acquiring the reliability index of the power transmission and transformation system and the power distribution system according to the component failures of the power transmission and transformation system, the failures of the internal components of the transformer substation and the component failures of the middle-voltage power transmission system. Through the scheme, the whole power supply reliability level of the power transmission and transformation system is balanced, so that scientific and reasonable construction of the power transmission and transformation system and the power distribution system is guided, and the development of reliable operation and maintenance of the power transmission and transformation system and the power distribution system is guided.

Owner:STATE GRID HUBEI ELECTRIC POWER COMPANY

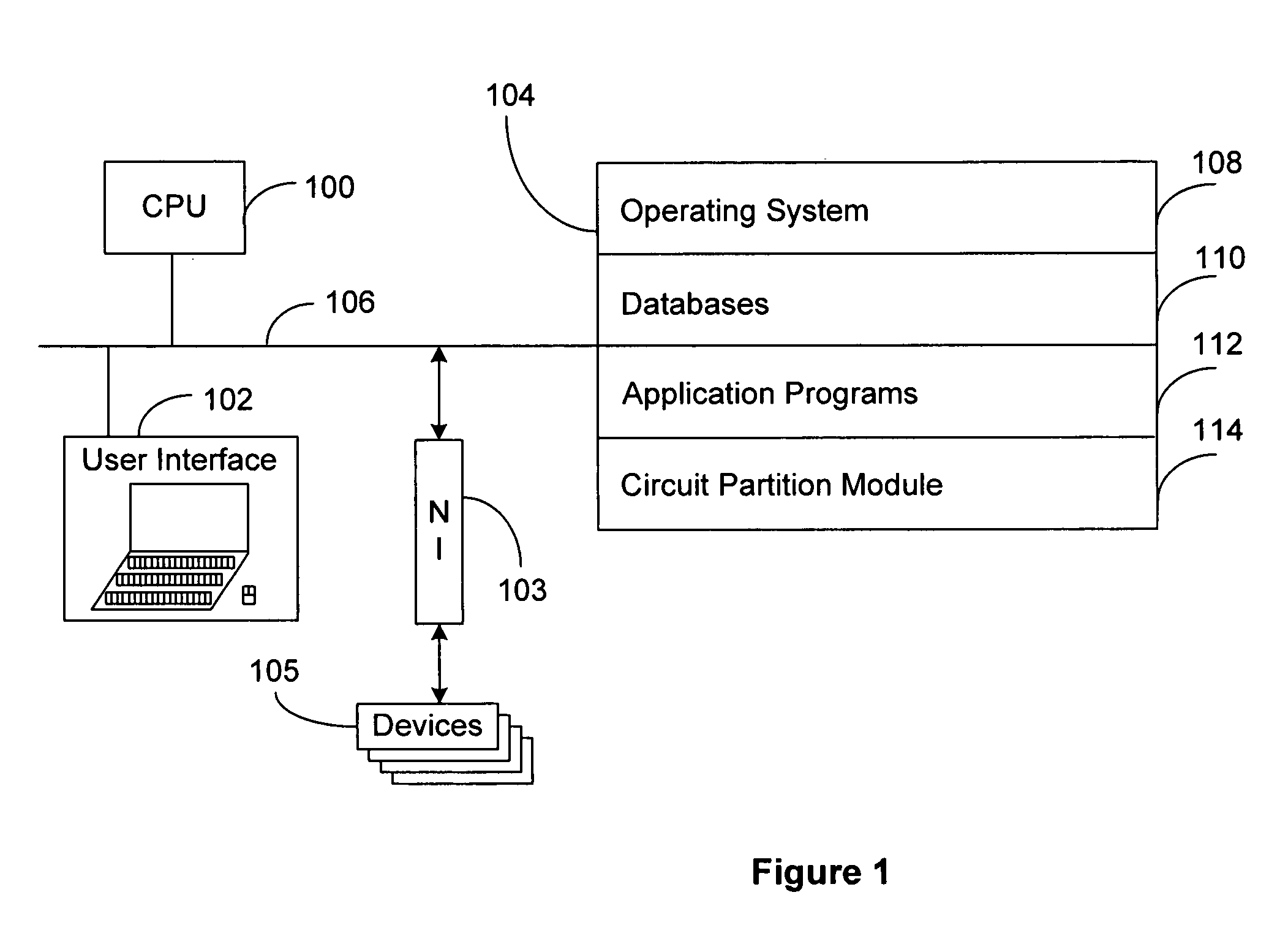

Method and system for partitioning integrated circuits

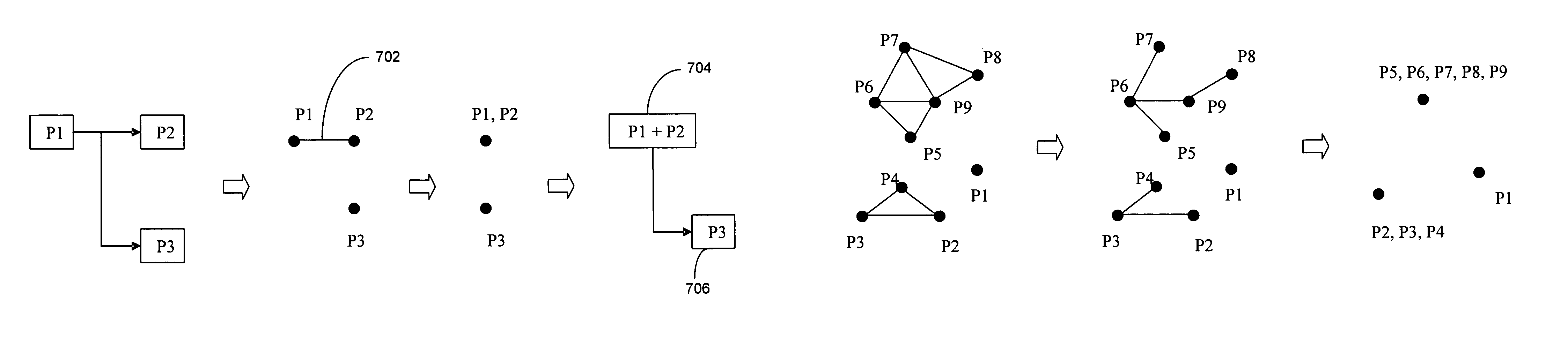

InactiveUS7836419B1Computer aided designSpecial data processing applicationsGraphicsComputer science

Method and system for partitioning integrated circuits are disclosed. The method includes receiving a netlist representation of the circuit comprising circuit components, partitioning the circuit to form one or more circuit partitions according to a predefined partitioning method, where each circuit partition includes one or more circuit components. The method further includes, for each circuit partition, identifying substantial correlations between the circuit partition and one or more other circuit partitions to form a spanning tree, where the spanning tree connects the circuit partition to the one or more other circuit partitions via a graph, and merging the circuit partition and the one or more other circuit partitions in the spanning tree to form a new circuit partition.

Owner:CADENCE DESIGN SYST INC

Routing analysis method, logic synthesis method and circuit partitioning method for integrated circuit

ActiveUS7418688B2Improve forecast accuracyImprove accuracySemiconductor/solid-state device manufacturingComputer aided designIntegrated circuit layoutAnalysis method

The present invention relates to a routing analysis method for performing a routing analysis on an integrated circuit from a netlist which is information on a plurality of cells constituting the integrated circuit and routes connecting the cells, and the routing analysis method comprises a step (Step 1) of obtaining the sum of areas of a plurality of cells, the number of cells or the number of routes connecting the cells from the netlist, to be defined as a constant C, and calculating a layout area S which is an area of a square layout region, by dividing the constant C by a predetermined constant U, a step (Step 2) of calculating a total route length L by multiplying a half perimeter length H of the layout region having the layout area S obtained in Step 1 by a predetermined coefficient α, and a step (Step 3) of calculating a routing difficulty index by dividing the total route length L by the layout area S. Thus, the present invention provides a routing analysis method for an integrated circuit, which, allows calculation of routing difficulty index with high accuracy of prediction.

Owner:RENESAS ELECTRONICS CORP

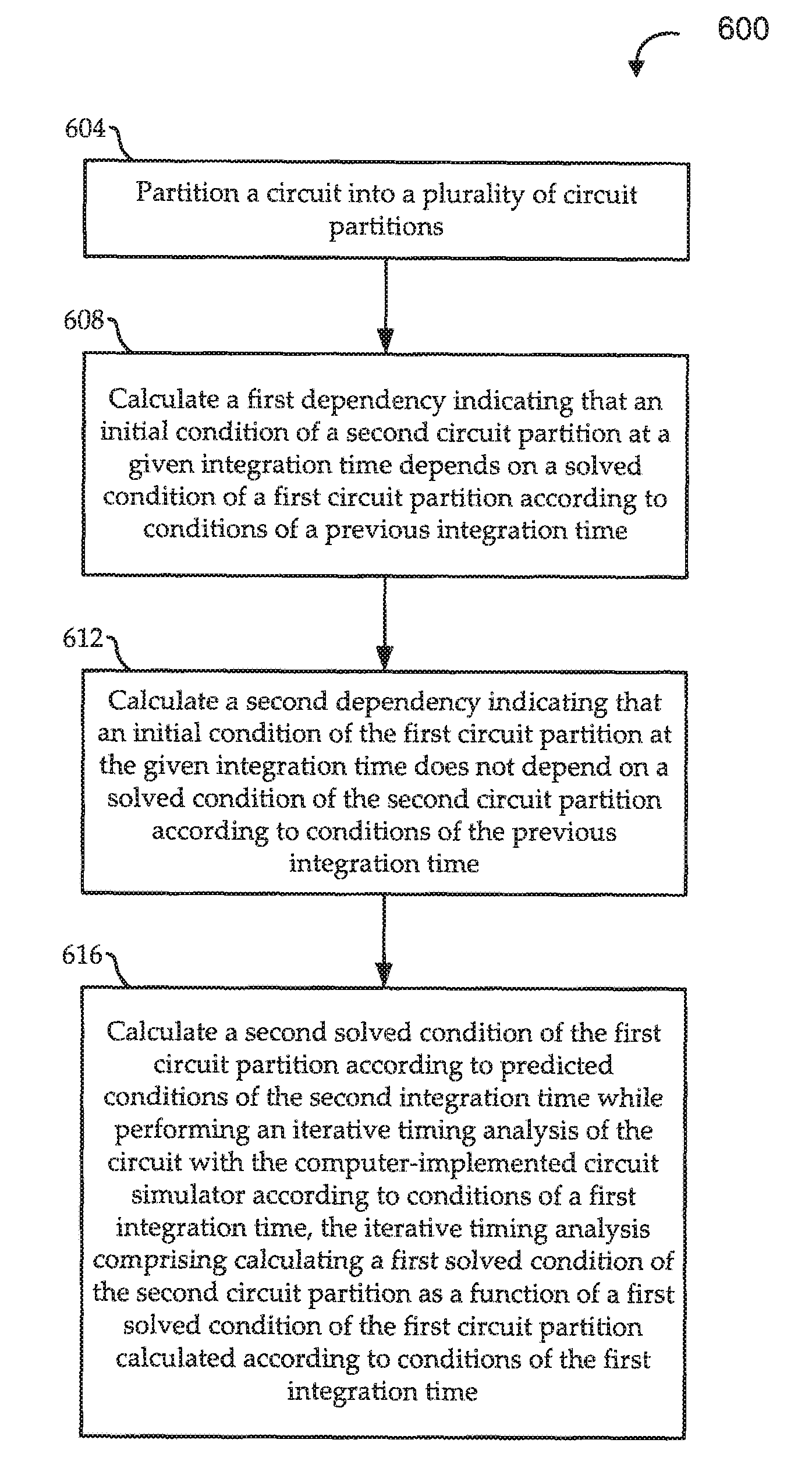

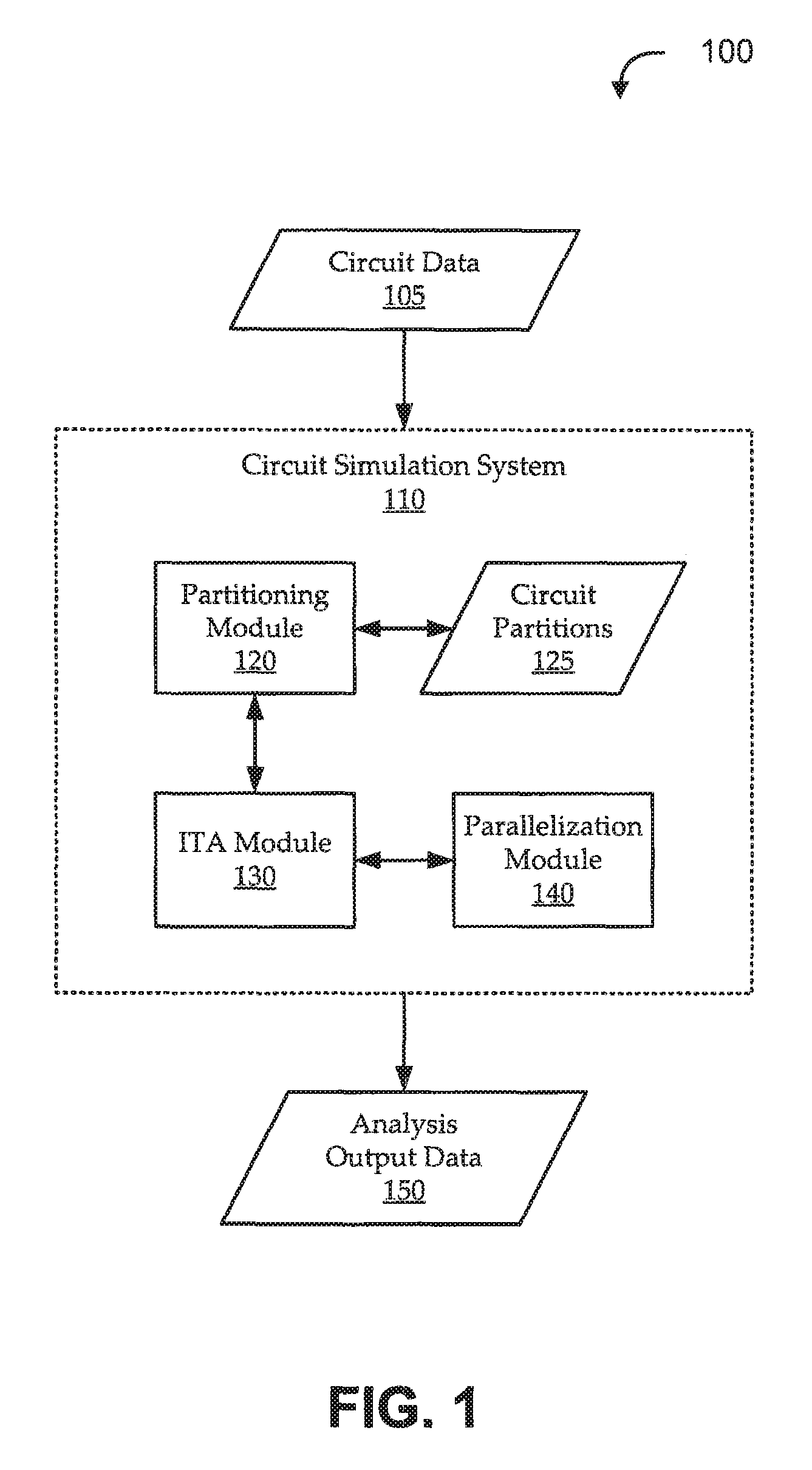

Parallel circuit simulation with partitions

ActiveUS8341577B1Computer aided designSoftware simulation/interpretation/emulationIterated timing analysisParallel simulation

Embodiments of the invention provide systems and methods for parallelizing simulation of circuit partitions. A circuit is divided into a number of partitions, for example, according to channel-connected regions. In some embodiments, the partitions are sequenced and assigned to multiple threads for parallel analysis. Iterative timing analysis (ITA), or some other form of analysis, is performed on the partitions over a series of integration time steps. Using the multiple threads, some partitions are solved at later integration time steps while the ITA continues toward relaxation convergence for a current integration time step.

Owner:ORACLE INT CORP

Programmable subscriber line circuit partitioned into high voltage interface and digital control subsections

InactiveUS7050577B2Avoid flowTwo-way loud-speaking telephone systemsSubstations coupling interface circuitsDigital signal processingLow voltage

Owner:INTERSIL INC

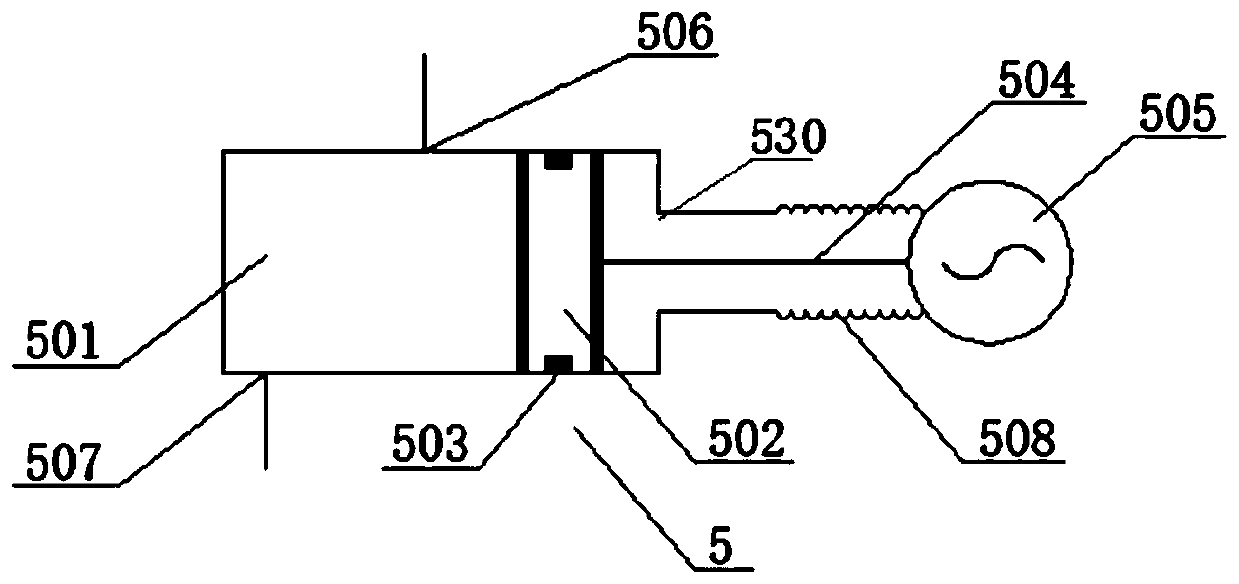

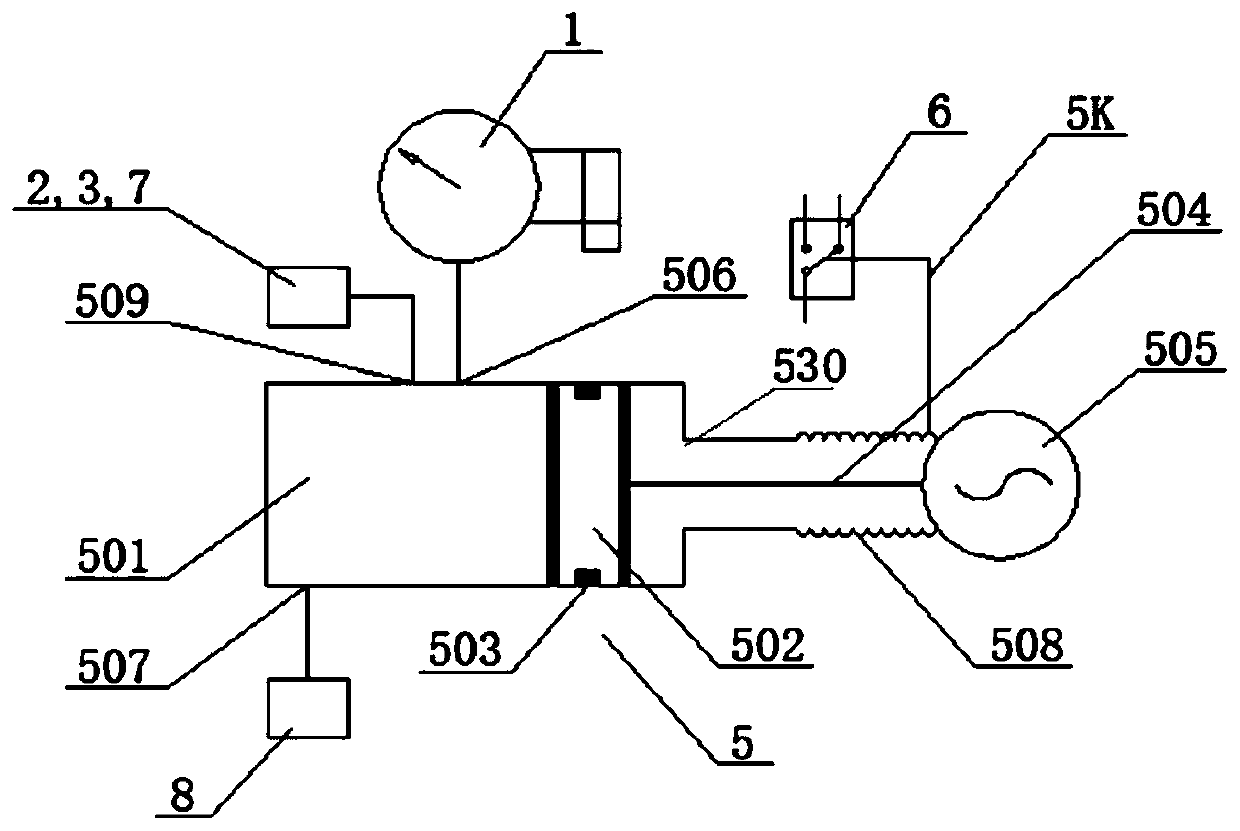

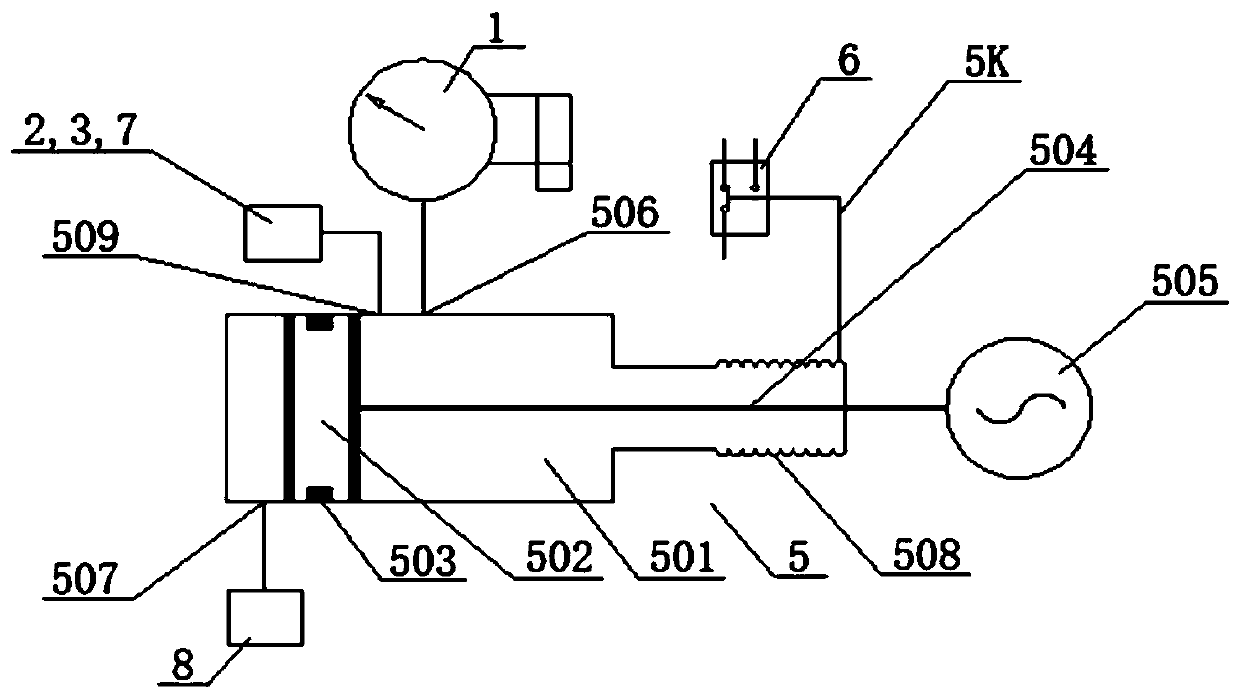

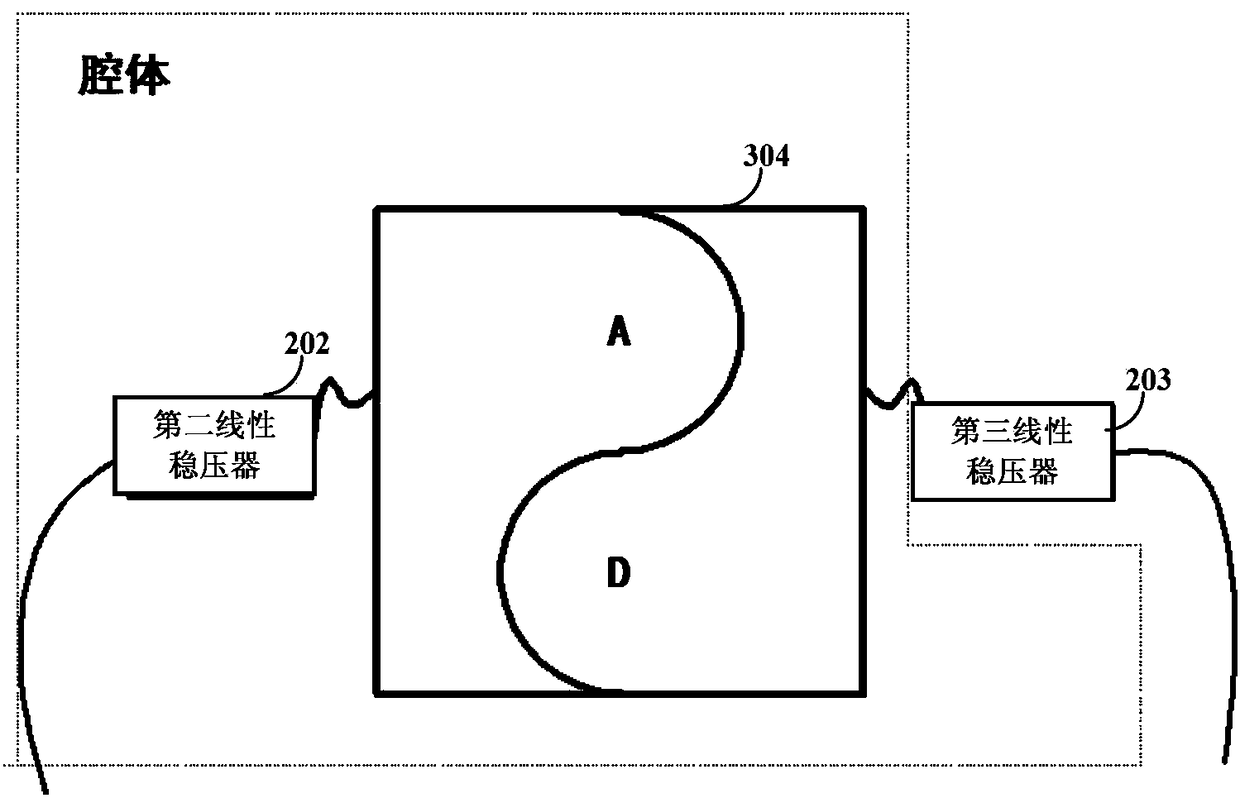

Gas circuit partition pressure adjusting mechanism for online verification of density relay

PendingCN110954816ARealize online verificationSpecific gravity by measuring pressure differencesFluid pressure control using electric meansPower gridEngineering

The invention provides a gas circuit partition pressure adjusting mechanism for online verification of a density relay, the gas circuit partition pressure adjusting mechanism comprises a gas circuit partition pressure adjusting mechanism body, the pressure adjusting mechanism body comprises a sealed cavity, a partition piece, a connecting rod and a driving part, and the sealed cavity is provided with a first interface and a second interface; a gas circuit of the gas circuit partition pressure regulating mechanism body is communicated with a gas circuit of the gas density relay through a firstinterface and is communicated with a gas circuit of electrical equipment through a second interface; the driving part drives the connecting rod so as to drive the partition piece to move in the sealedcavity; a gas path between the first interface and the second interface is isolated; the volume of the sealed cavity is changed according to the position change of the partition piece; therefore, thepressure of the gas density relay is adjusted to rise and fall, the gas density relay is enabled to generate contact signal action, online verification of the gas density relay is realized, verification can be completed without going to the site by maintainers, the reliability and efficiency of a power grid are greatly improved, and the cost is reduced.

Owner:SHANGHAI ROYE ELECTRICAL CO LTD

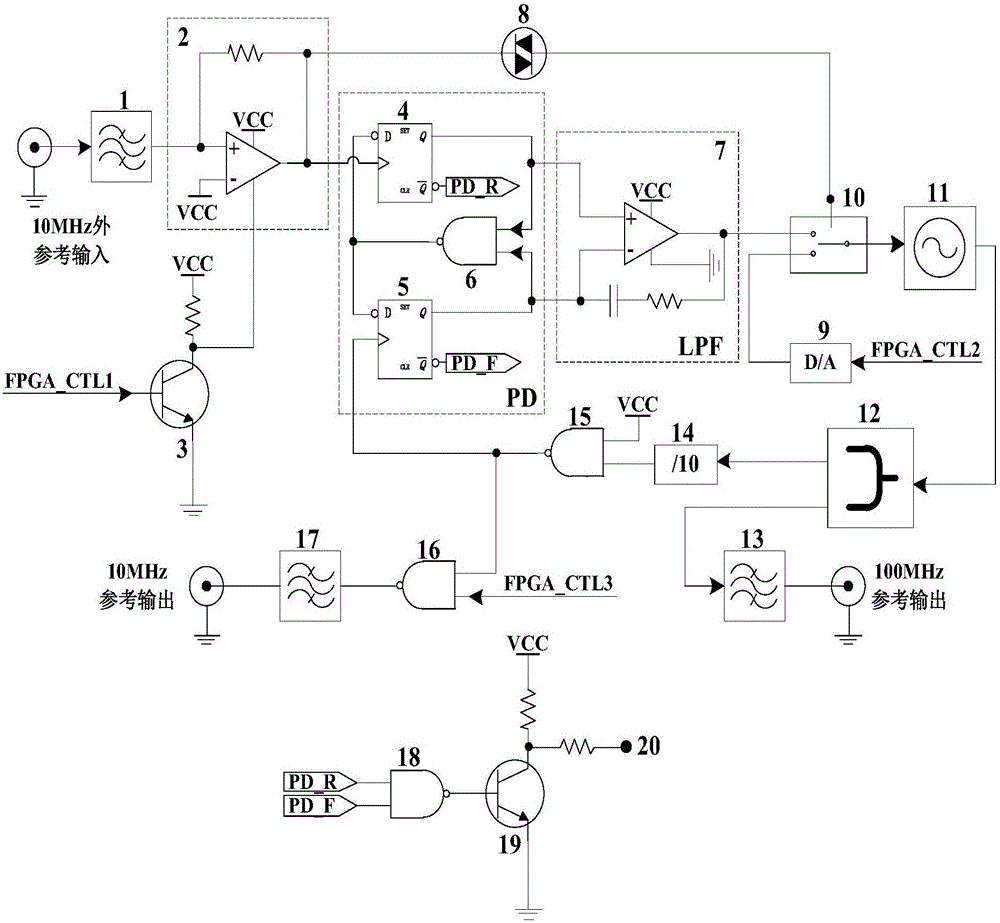

High-performance self-test external reference time-base circuit and implementation method thereof

ActiveCN106027041ADoes not affect reference signal indicatorsPulse automatic controlExternal referenceField-programmable gate array

The invention discloses a high-performance self-test external reference time-base circuit and an implementation method thereof. The high-performance self-test external reference time-base circuit comprises an external reference filtering and amplifying circuit, an external reference self-test circuit, an external reference phase discrimination filtering circuit, an one-out-of-two switch and a constant-temperature crystal oscillator, wherein an output end of the external reference self-test circuit is connected with a selection control end of the one-out-of-two switch; an output end of the external reference phase discrimination filtering circuit is connected with one input end of the one-out-of-two switch; when an external reference signal is input, the external reference filtering and amplifying circuit partitions the external reference signal into two paths after filtering and amplifying the external reference signal; one path of the external reference signal is connected with the external reference phase discrimination filtering circuit; the other path of the external reference signal is connected with the external reference self-test circuit; and the one-out-of-two switch is controlled to be switched to an output end of the external reference phase discrimination filtering circuit in order to perform loop phase locking on the external reference signal. The high-performance self-test external reference time-base circuit has the beneficial effects that a complete machine can decide whether to use the external reference signal not under the control of an FPGA (Field Programmable Gate Array) even when the external reference signal is input.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

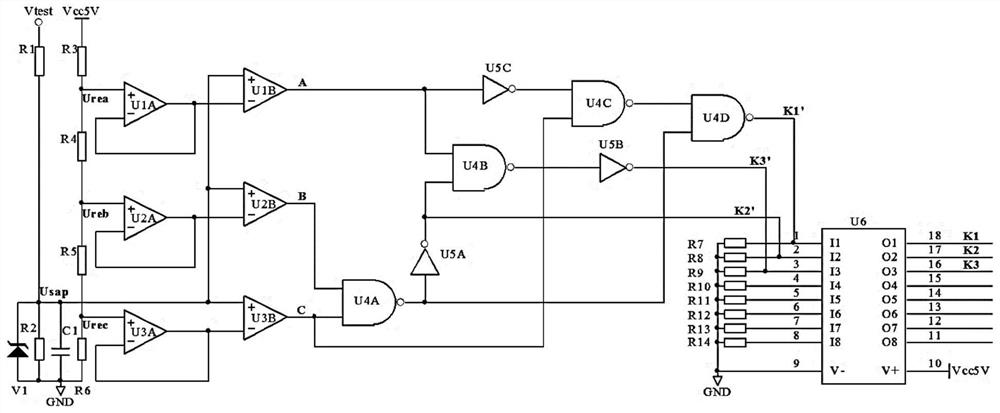

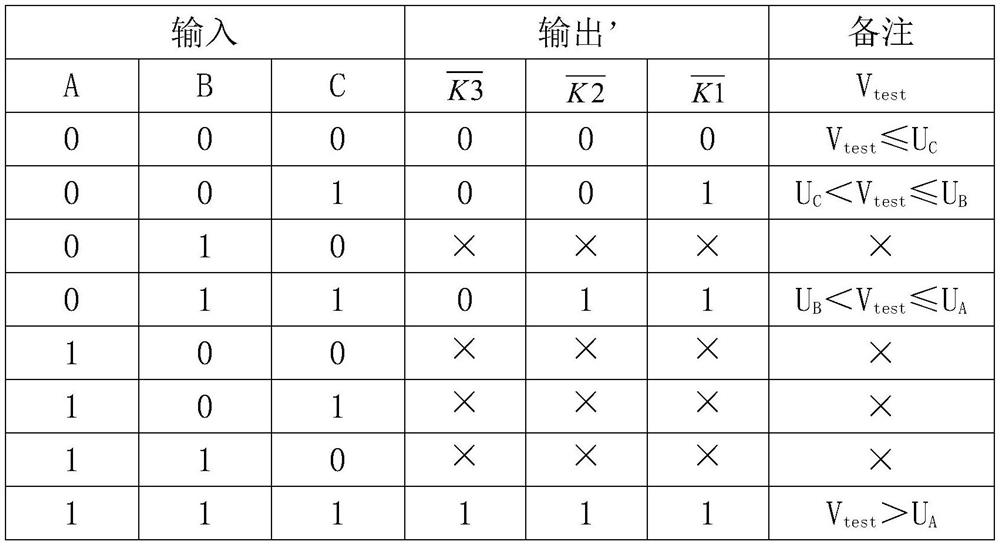

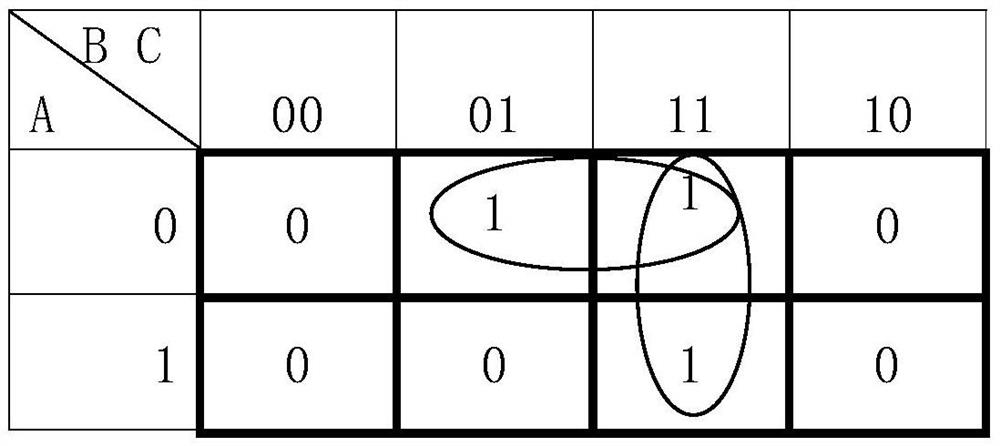

Simple and reliable power-on state detection circuit

ActiveCN113009257AImprove compatibilityFirmly connectedElectric connection testingVoltage measurements onlyHemt circuitsEngineering

The invention provides a simple and reliable power-on state detection circuit. A signal acquisition circuit acquires a power-on voltage signal and generates an acquisition signal, the acquisition signal is compared with a reference voltage formed in a reference circuit, and then signal conversion is performed through a logic state conversion circuit; the acquisition signal is converted into an OC interface signal through the driver, so that a state indication circuit can be conveniently connected; the power-on state detection circuit detects state discrimination in a segmented manner through multi-point characteristic voltage, and is simple in structure and convenient to debug; meanwhile, the power-on state detection circuit is continuous in partition voltage output logic state, high in output interface compatibility and easy to adjust.

Owner:XIAN MICROELECTRONICS TECH INST

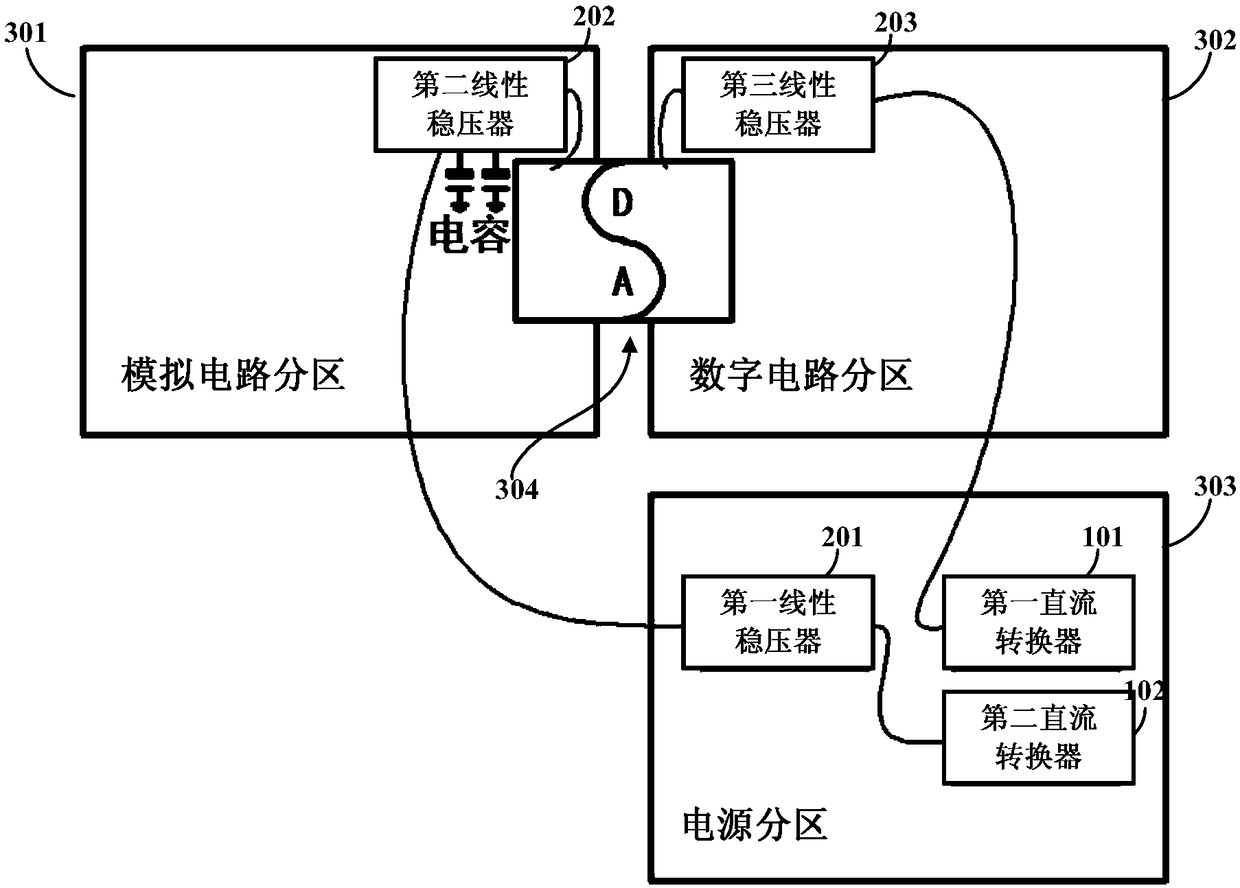

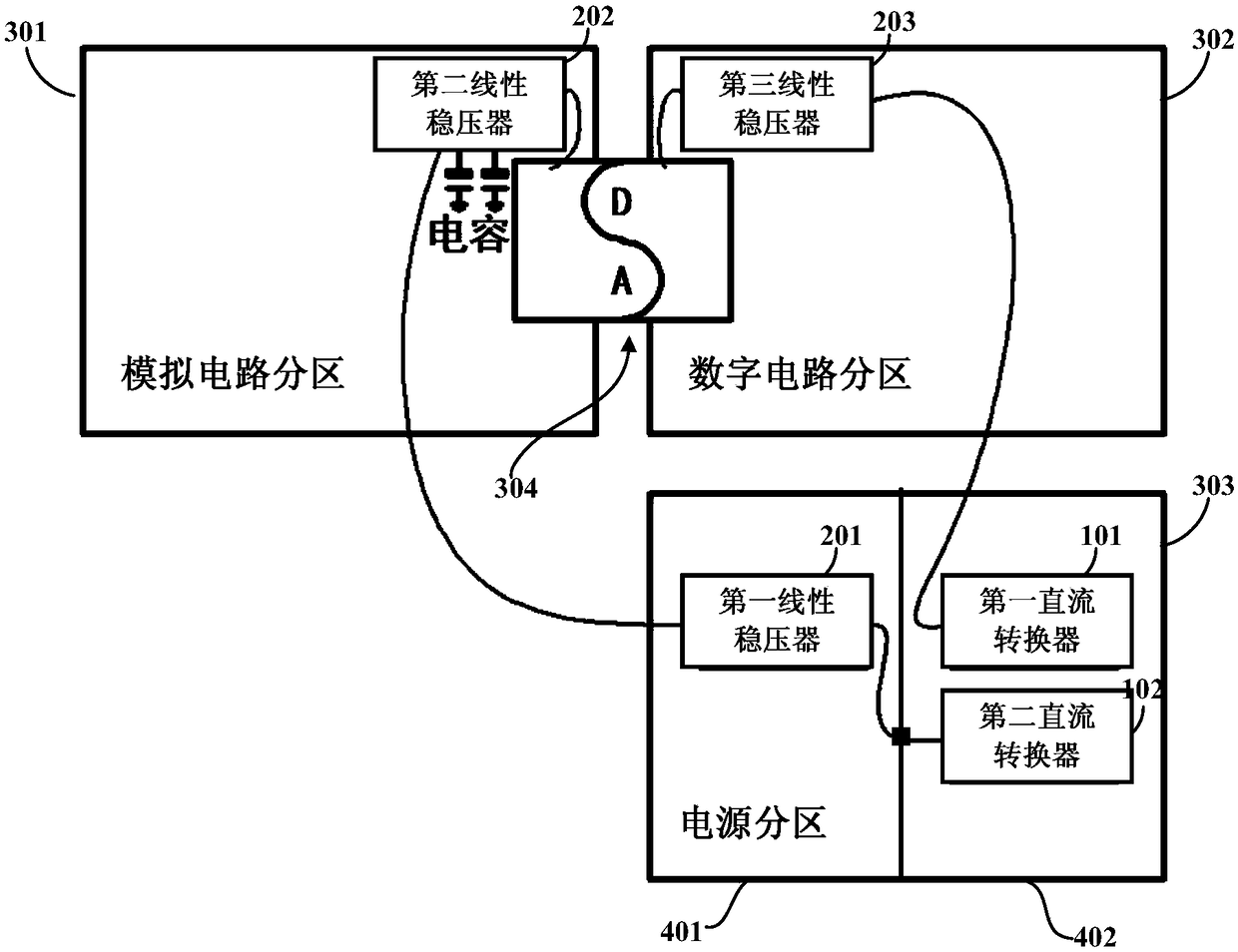

Power supply circuit of ADC (Analog to Digital Converter) and spectrum analyzer

ActiveCN108242928AWill not be strungAvoid introducingDc-dc conversionPhysical parameters compensation/preventionFrequency spectrumSpectrum analyzer

The application provides a power supply circuit of an ADC (Analog to Digital Converter) and a spectrum analyzer. The power supply circuit of the ADC (Analog to Digital Converter) is suitable for a digital-analog hybrid circuit board and at least comprises a first direct current converter, a second direct current converter, a first linear voltage stabilizer, a second linear voltage stabilizer and athird linear voltage stabilizer; the first direct current converter, the second direct current converter and the first linear voltage stabilizer are arranged in a power source partition; the second linear voltage stabilizer is arranged in an analog circuit partition; the third linear voltage stabilizer is disposed in a digital circuit partition; a voltage supplied by a power source is subjected to two-stage voltage reduction of the first direct current converter and the third direct current converter so as to be decreased to a power supply voltage of the digital power source end of the ADC; and the voltage supplied by the power source is subjected to three-stage voltage reduction of the second direct current converter, the first linear voltage stabilizer and the second direct current converter so as to be decreased to a power supply voltage of the analog power source end of the ADC. With the power supply circuit of the ADC (Analog to Digital Converter) and the spectrum analyzer of theinvention adopted, low-frequency noises from the power source or coupled along a line can be reduced.

Owner:RIGOL

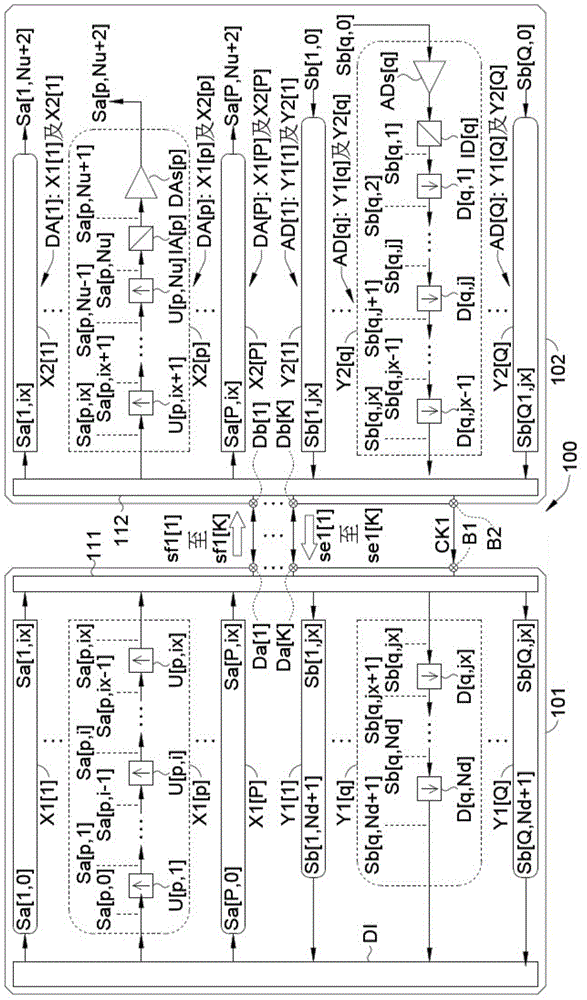

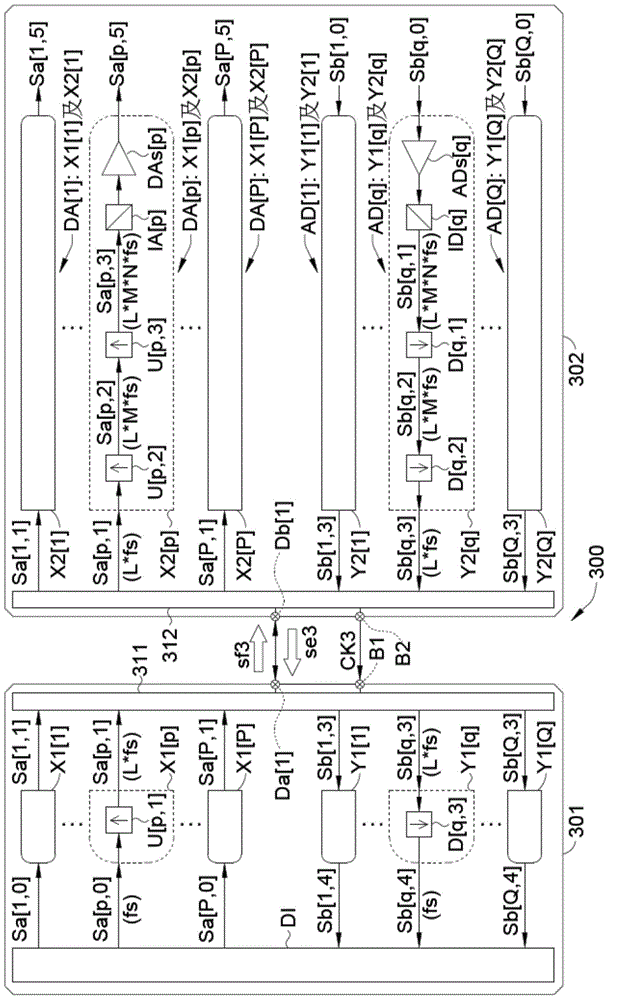

Signal processing system and associated method

ActiveCN104035908AIncrease flexibilityElectric digital data processingMultiple frequencySignal processing

Owner:MEDIATEK INC

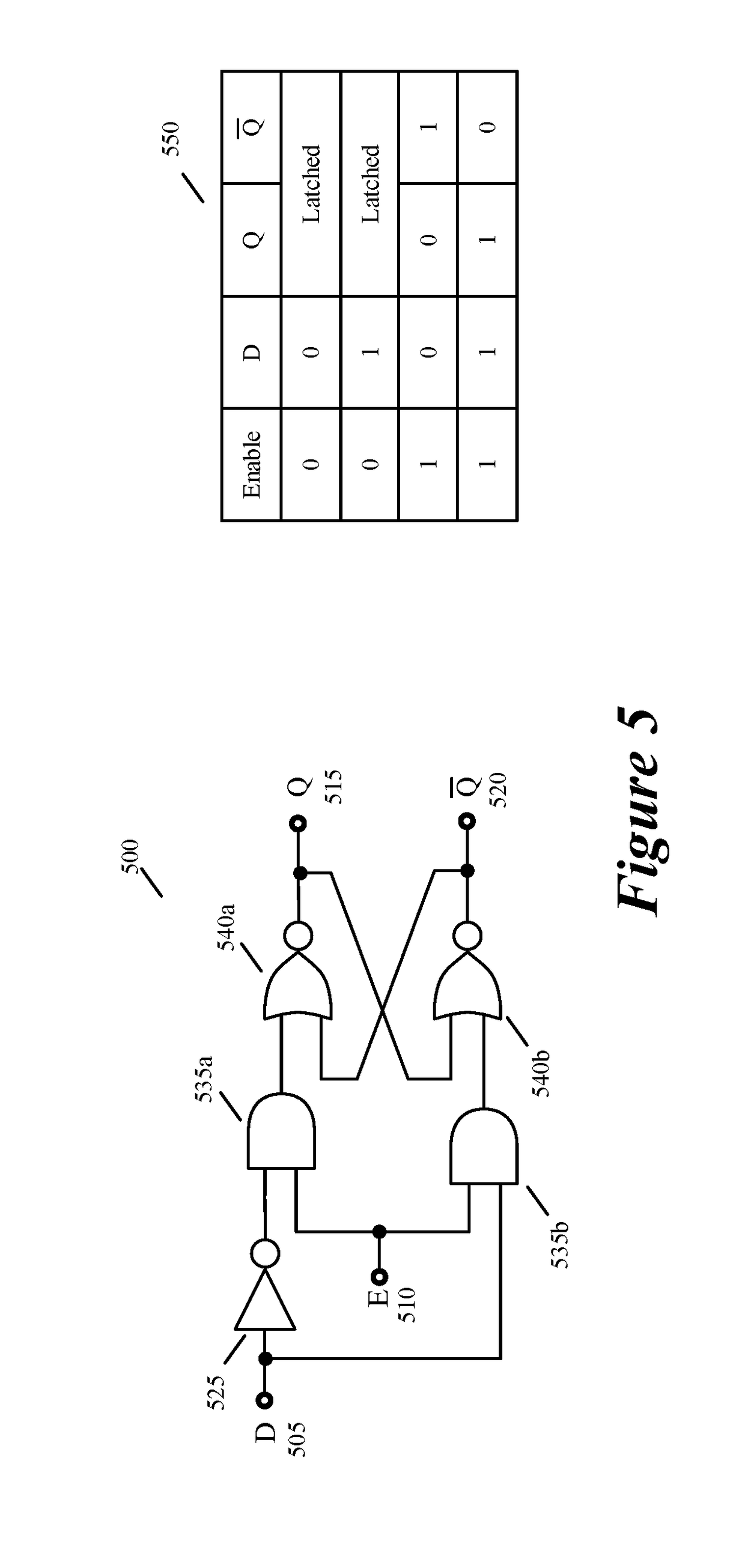

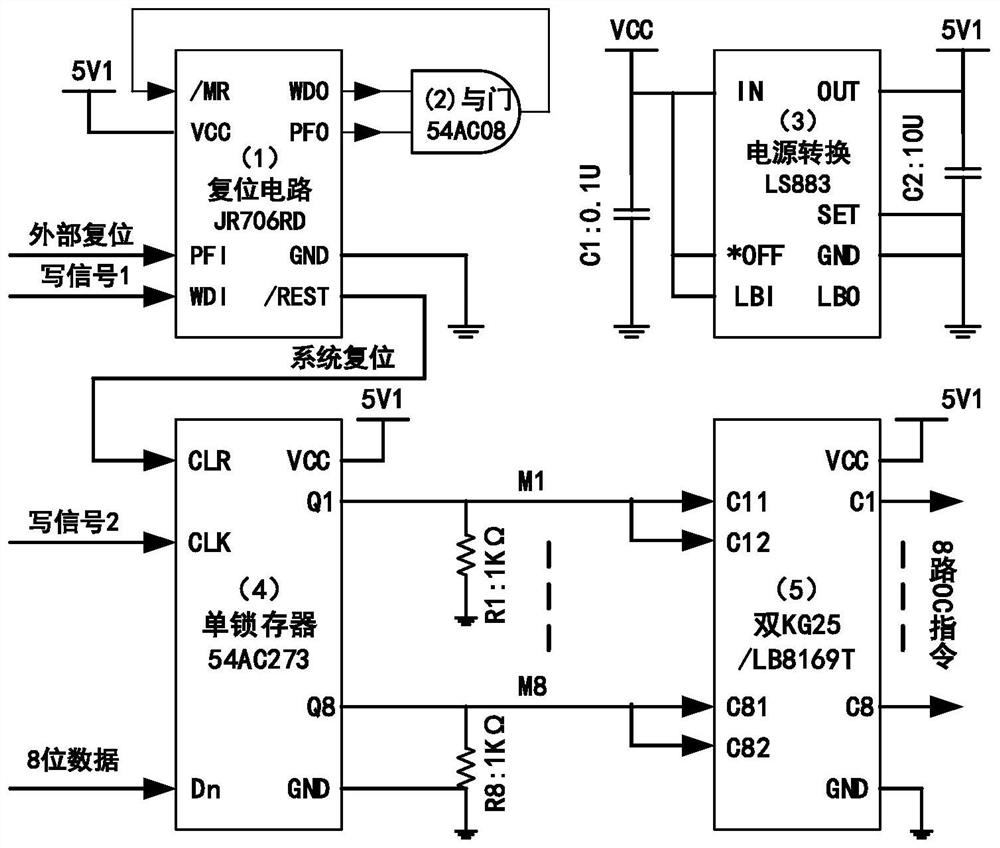

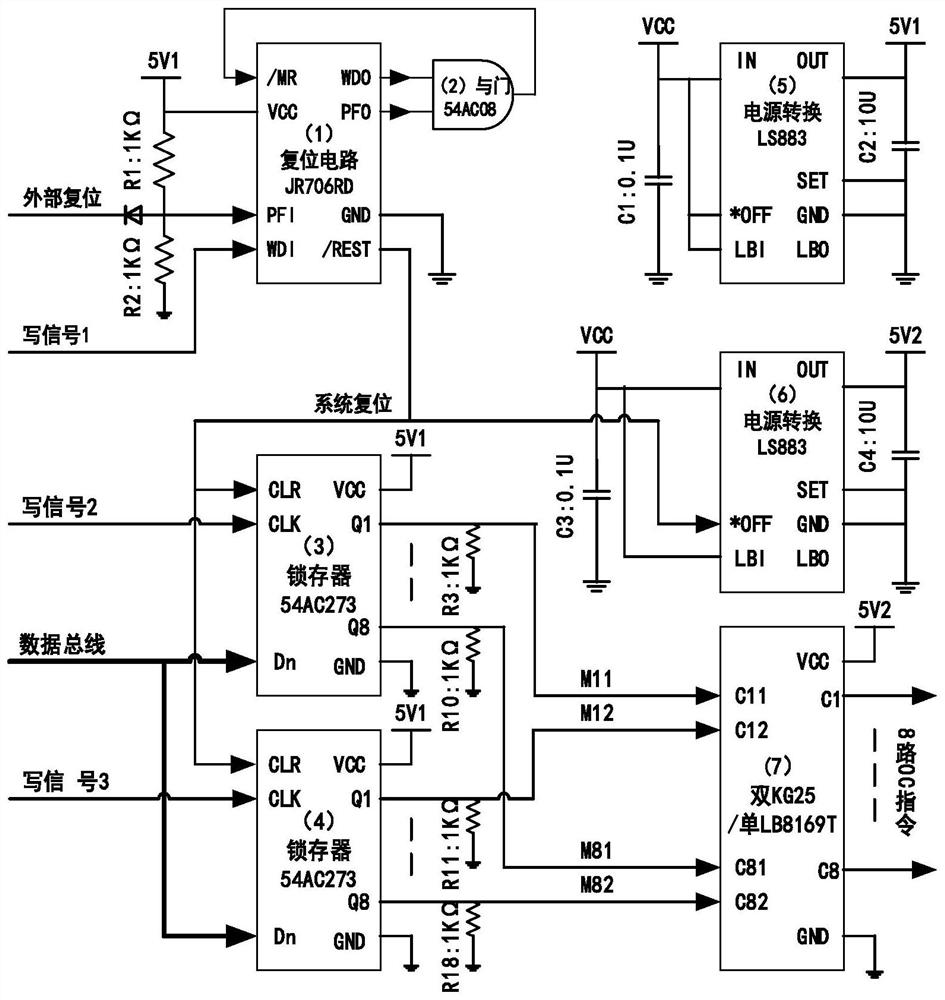

Method and circuit structure for controlling abnormal instruction output

ActiveCN111736453AAchieve outputInhibit outputSafety arrangmentsEnergy efficient computingPulse controlControl engineering

The invention discloses a method and a circuit structure for controlling abnormal instruction output. The circuit structure comprises a reset circuit, a partition time sequence power supply circuit, an instruction generation latch circuit and a redundant signal control instruction driving circuit. A redundant latch circuit is adopted as an instruction generation circuit, a plurality of latches respectively generate pulse control signals to form multi-pulse control signals, and instructions can be output only when the corresponding multi-pulse control signals are valid; an independent power supply unit supplies power to an instruction generation circuit and an instruction driving circuit separately, the power supply of the instruction driving circuit is controlled by a reset signal, the instruction driving circuit is powered on after the instruction generation circuit is powered on, and abnormal instruction output in the power-on process is forbidden; the voltage of the subarea power supply is monitored in real time, when the voltage is lower than a normal power supply range, a reset signal is generated to power off the instruction driving circuit, the instruction driving circuit ispowered off in the process that voltage abnormal fluctuation is lower than a normal value or power is off, and abnormal instruction output is avoided. The reliability of instruction output can be effectively improved.

Owner:XIAN MICROELECTRONICS TECH INST

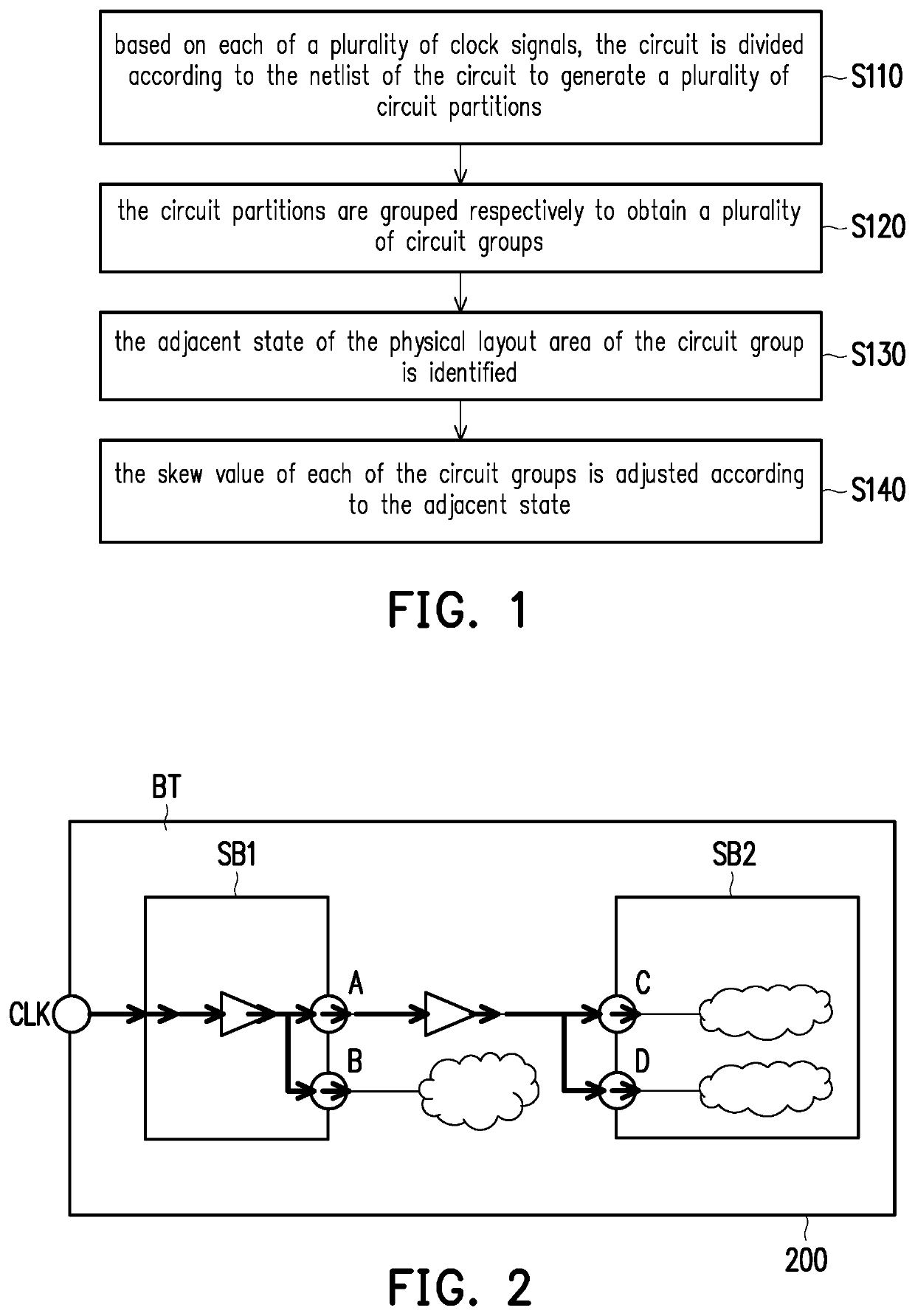

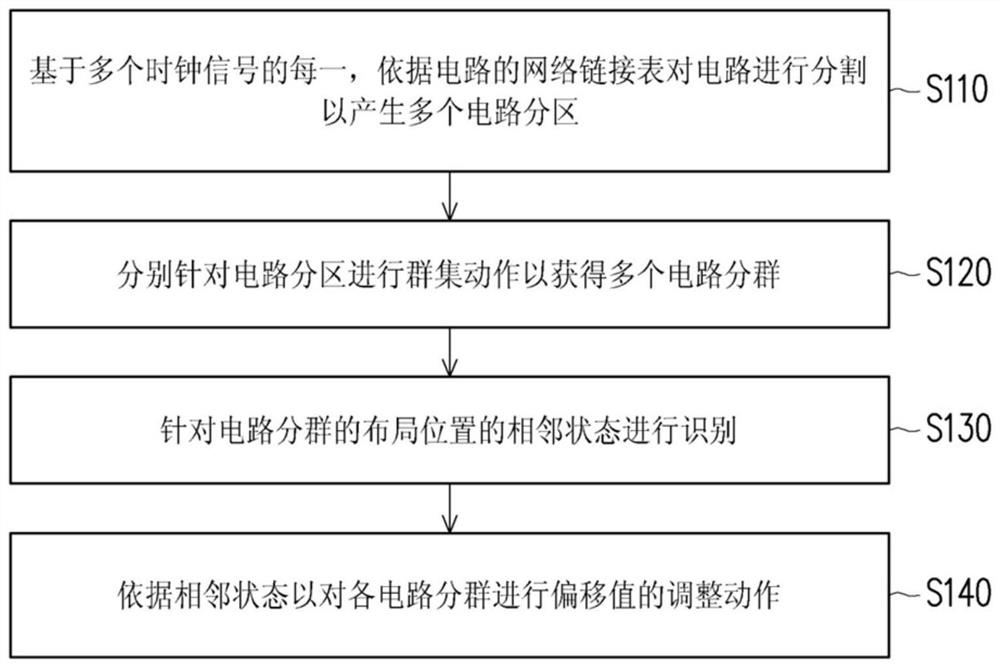

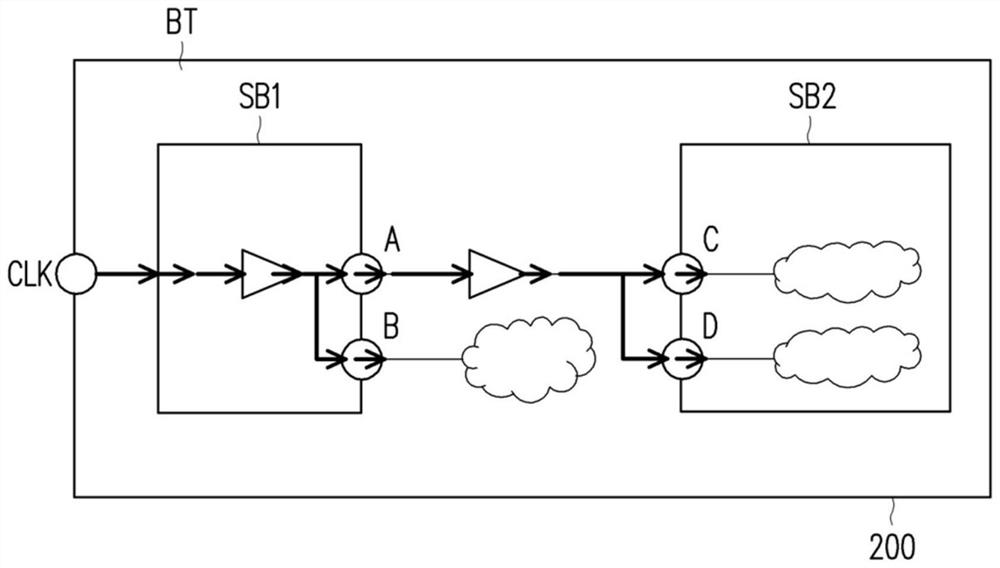

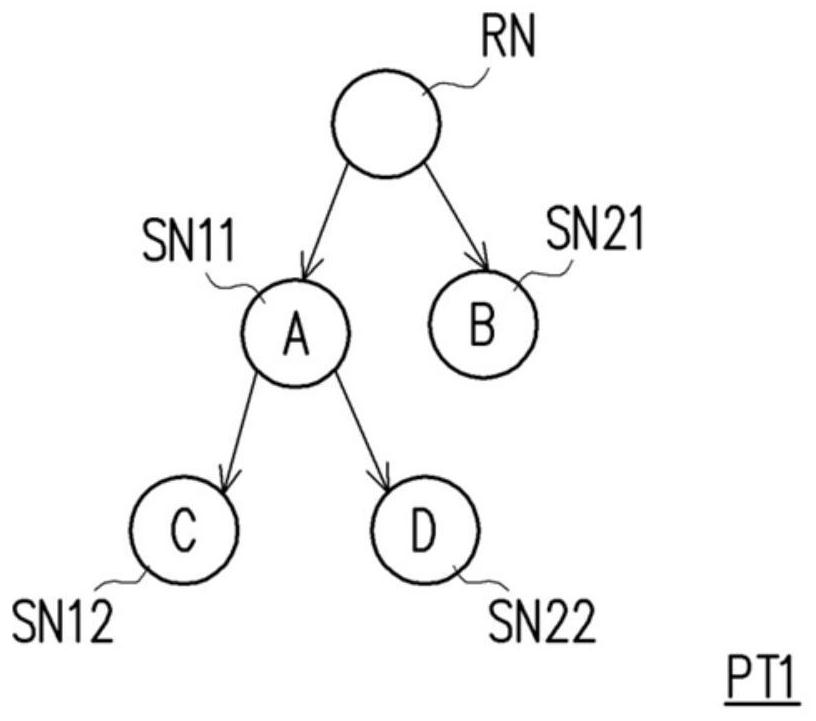

Apparatus for adjusting skew of circuit signal and adjusting method thereof

ActiveUS20210341962A1Easy to adjustImprove performance qualityGenerating/distributing signalsHemt circuitsSkew

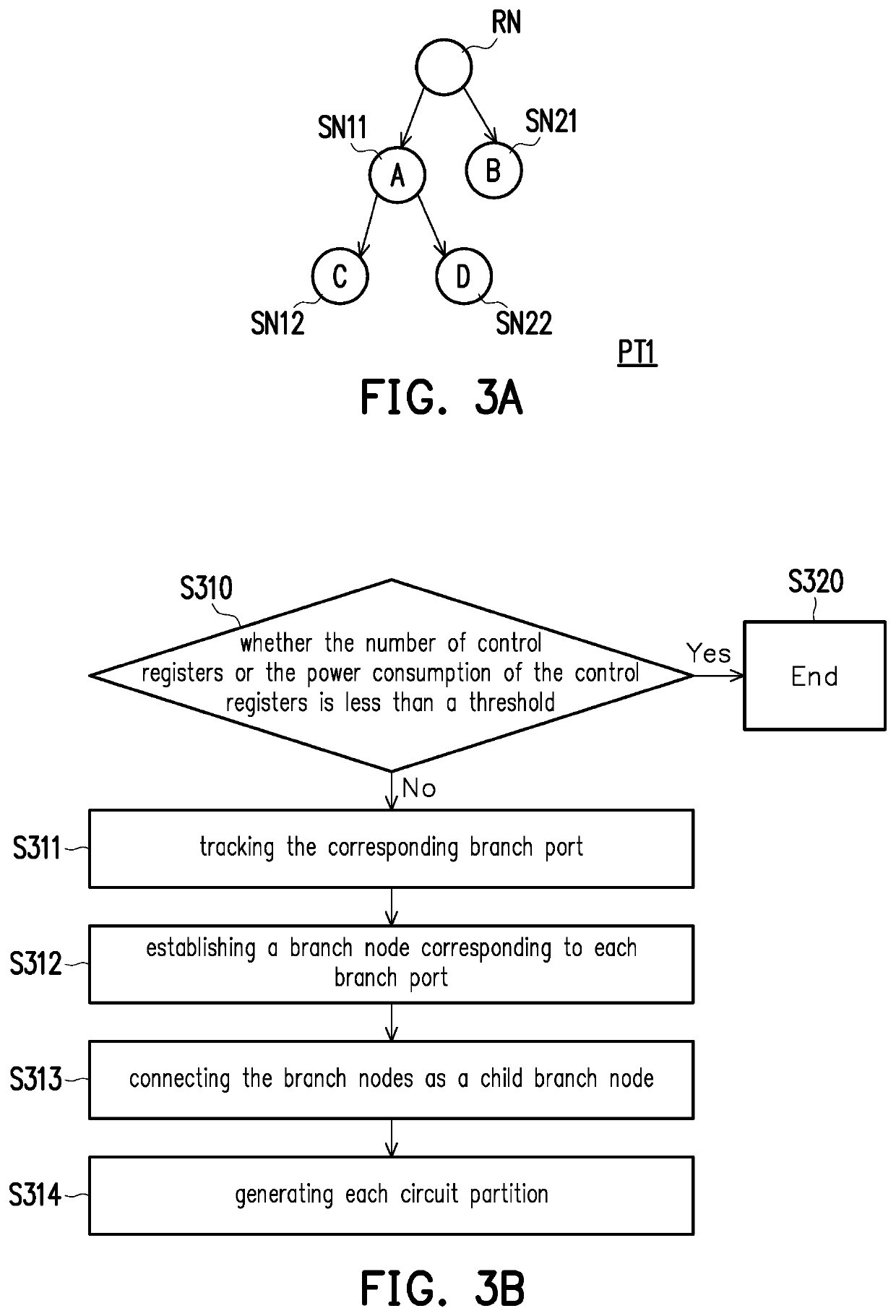

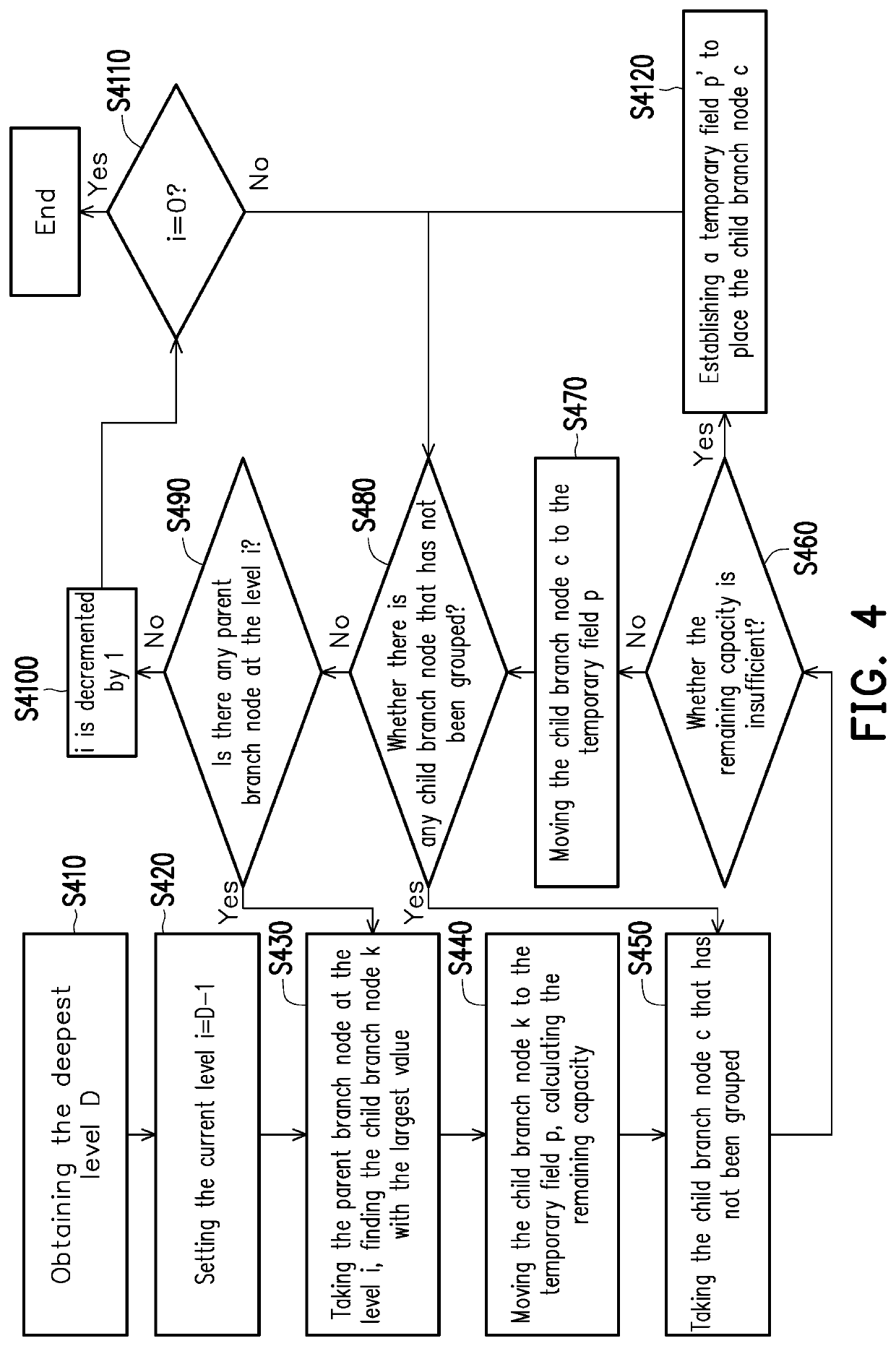

An apparatus for adjusting skew of circuit signal and an adjusting method thereof are provided. The adjusting method includes: providing a controller for executing: based on each of a plurality of clock signals, dividing a circuit to generate a plurality of circuit partitions according to a netlist of the circuit; grouping the circuit partitions to respectively generate a plurality of circuit groups; identifying adjacent states of layout areas of the circuit groups; and, adjusting a skew value of each of the circuit groups according to the adjacent states.

Owner:GLOBAL UNICHIP CORPORATION +1

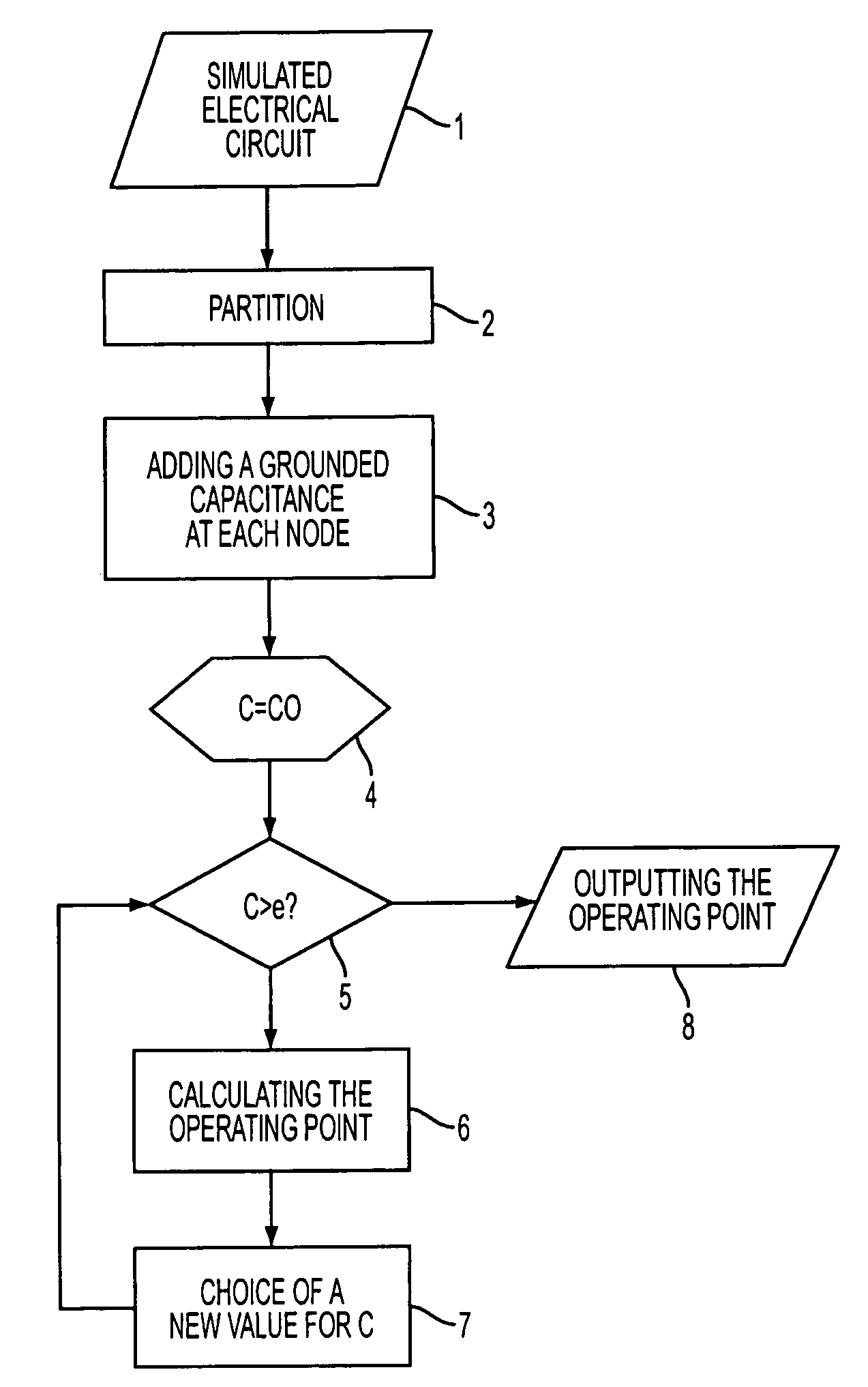

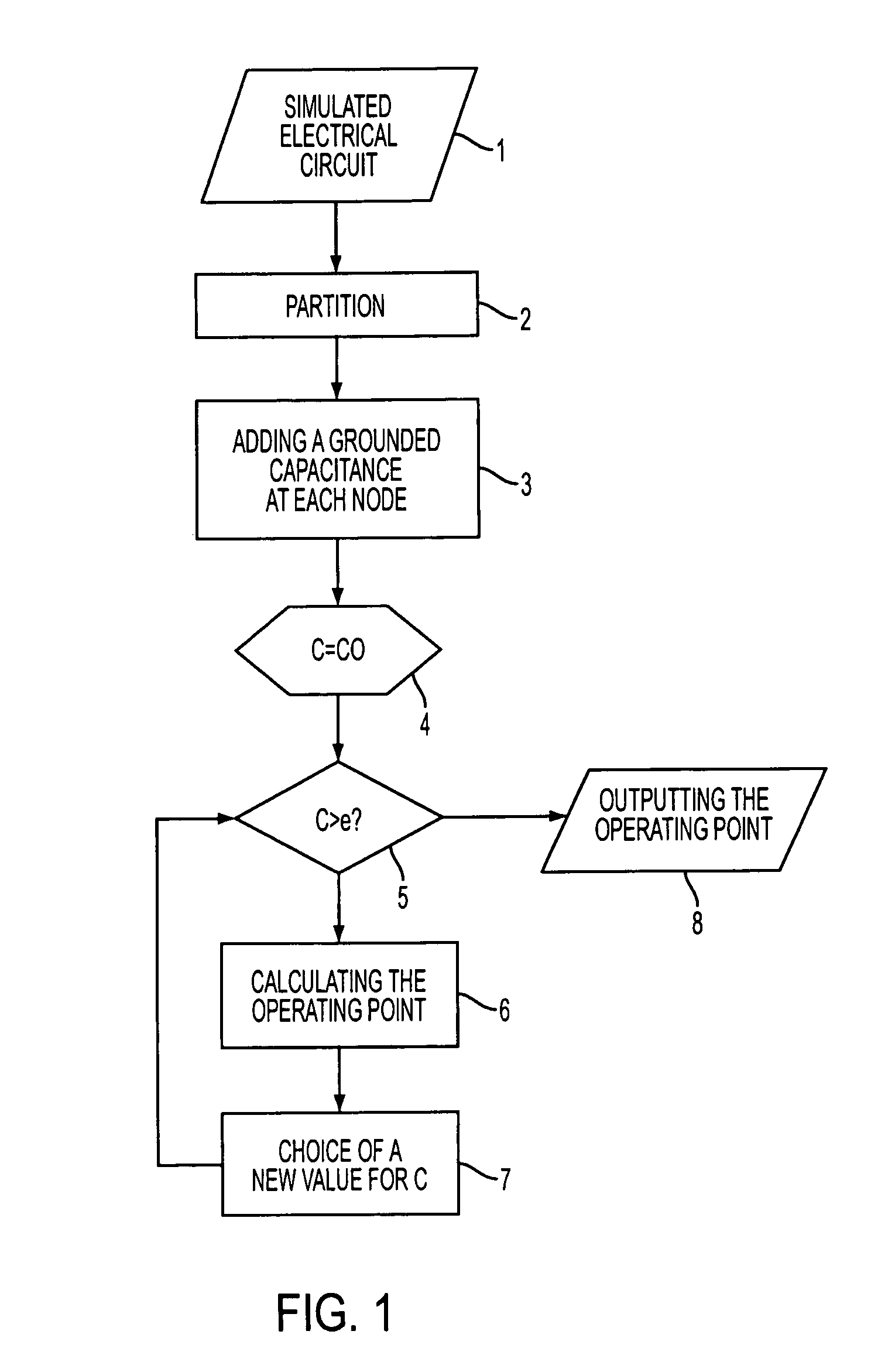

Computer-assisted method for the parallel calculation of the operating point of electric circuits

InactiveUS7024648B1Simple and reliable and fast calculationAvoid problem in calculationDetecting faulty computer hardwareComputer aided designOperating pointComputer-aided

A computer-aided method for parallel calculation of the operating point of electrical circuits has the circuit partitioned into a number of partitions in a first step, in which the charging method is used for the parallel calculation of the individual partitions.

Owner:POLARIS INNOVATIONS

A pixel circuit, its driving method, and a display device

ActiveCN111243496BReduce the number of tracesReduce drive power consumptionStatic indicating devicesComputer hardwareScan line

A pixel circuit, its driving method, and a display device. The pixel circuit includes a first switch subcircuit, a partition driver chip, and a plurality of light-emitting elements, wherein: the first switch subcircuit is connected to a scanning line, a data line, and a first node connection, used to write the data voltage signal of the data line into the first node under the control of the scan line; The corresponding driving time of each light-emitting element is determined according to the data voltage signal, and the light-emitting element is driven to emit light by using the data voltage signal within the corresponding driving time. This application realizes the active site selection drive through the first switch sub-circuit and the partition driver chip, which effectively reduces the number of glass-based wiring, greatly reduces the difficulty of the side wiring process, and reduces the driving power of the overall display module. Consumption and driving costs, greatly improving the competitive advantage of the product.

Owner:BOE TECH GRP CO LTD +1

A Circuit Division Method for Parallel Circuit Simulation

InactiveCN103353910BThe number of ports is goodGood for load balancingSpecial data processing applicationsVery large scale integrated circuitsImproved method

The invention provides a circuit partitioning method for parallel circuit simulation, and belongs to the technical field of very large scale integration (VLSI) circuit design automation. The method comprises the steps as follows: better initial partition is rapidly acquired with a recursive multistage two-way partition method taking minimum cut as a target; and then minimum communication traffic and load balancing are taken as targets, and the partition is continuously improved with an iteration improvement method. The technical scheme is as follows: 1), a k-route initial partition is acquired with the recursive two-way partition method; 2), the two-way partition is performed with a multistage partition method, wherein at a roughening stage, load balancing is combined, and at an elaboration stage, iterations are limited; and 3), in an iteration improvement process, a peak which can improve the load balancing is selected to be moved preferentially each time. According to the method, an obtained partition result meets the requirements of the load balancing and less communication traffic, and the method is applicable to a circuit partition stage of an VLSI parallel circuit simulation system.

Owner:FUZHOU UNIV

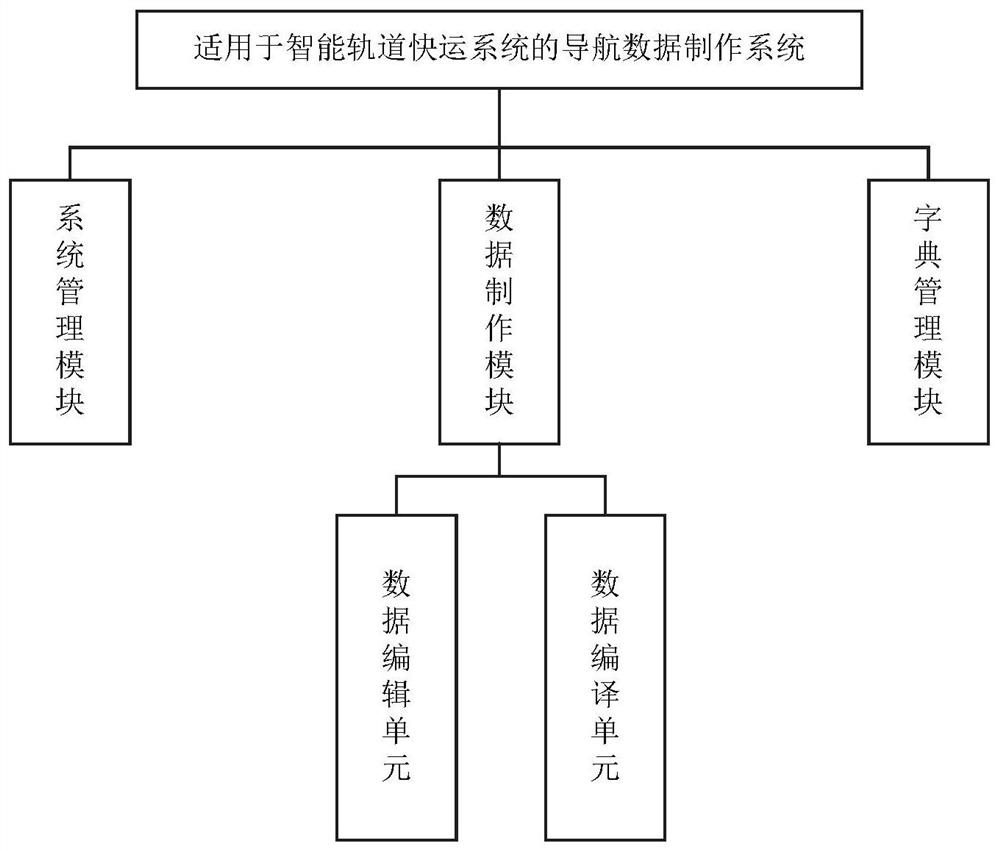

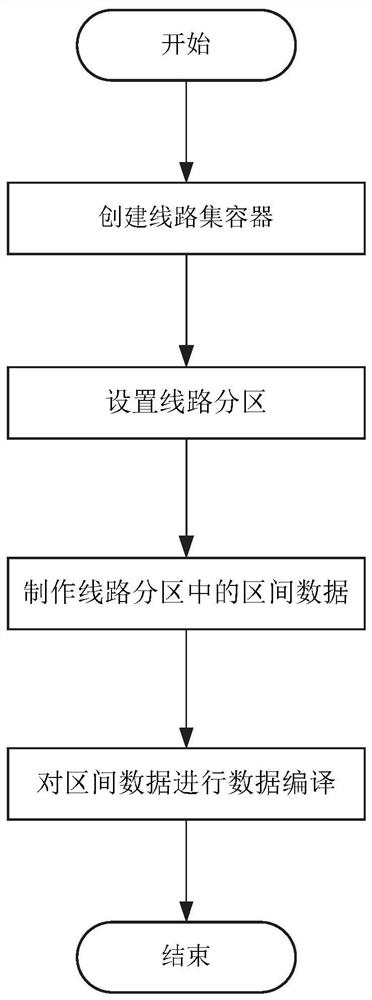

Navigation data making method and system suitable for intelligent track express system

PendingCN113483768AMeet application needsEfficient data productionInstruments for road network navigationTrackwayInterval data

The invention discloses a navigation data making method and system suitable for an intelligent rail express system, which can make and maintain the navigation data according to a proprietary format, visually display the information, such as stations and speed limits of the operation of an intelligent rail train, etc., and meet the requirements of ART trains for the navigation data. According to the technical scheme, the method comprises the steps of 1, creating a line set container; 2, setting circuit partitions; 3, making the interval data in the circuit partitions; and 4, performing data compiling on the interval data.

Owner:HUNAN CRRC TIMES SIGNAL & COMM CO LTD

Device and method for adjusting circuit signal offset

PendingCN113591424AComputer aided designSpecial data processing applicationsNetwork linkHemt circuits

The invention provides an adjusting device and an adjusting method for circuit signal offset. The circuit signal offset adjusting method comprises the following steps: providing a controller to execute the following steps: based on each of a plurality of clock signals, segmenting the circuit according to a network link table of the circuit to generate a plurality of circuit partitions; respectively performing clustering action on the circuit partitions to obtain a plurality of circuit clusters; recognizing adjacent states of the layout positions of the circuit groups; and adjusting the offset value of each circuit group according to the adjacent state.

Owner:GLOBAL UNICHIP CORPORATION +1

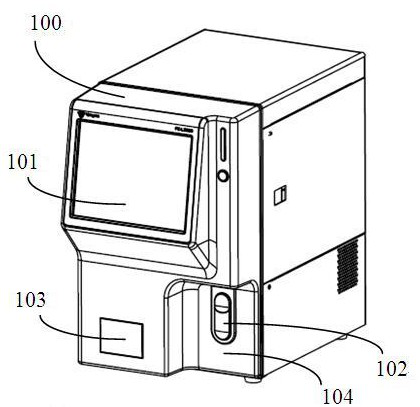

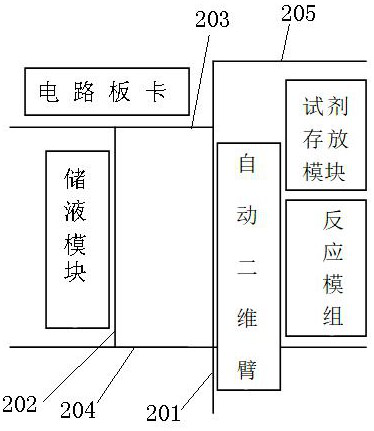

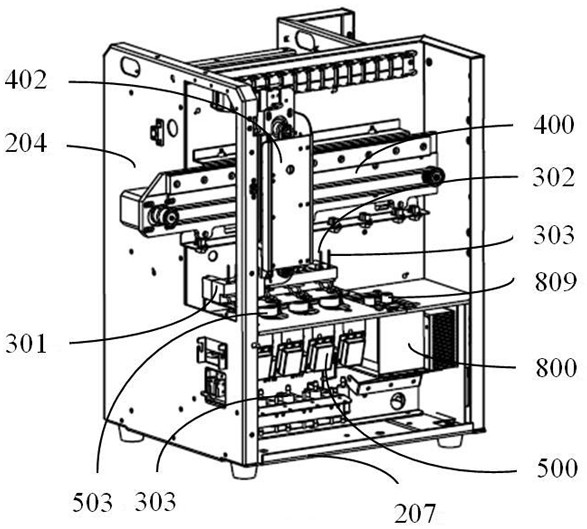

A specific protein analyzer and testing method thereof

ActiveCN110244070BWon't hurtMaximize utilizationScattering properties measurementsEngineeringStructural engineering

The invention discloses a specific protein analyzer and a testing method thereof. The specific protein analyzer includes a casing and a frame, and the frame includes a front support plate spaced from the front operating panel of the casing and a rear support spaced from the back plate of the casing Two-dimensional arm fixing plate perpendicular to the bottom plate is installed between the front and rear support plates. The X-axis component of the automatic two-dimensional arm is installed on the two-dimensional arm fixing plate. One side of the two-dimensional arm fixing plate is provided with a The circuit partitions are set at intervals on the back of the shell, the control board is installed between the circuit partition, the two-dimensional arm fixing plate and the casing, and the liquid circuit partition perpendicular to the bottom plate is arranged between the circuit partition and the front support plate. A horizontal support plate parallel to the bottom plate is provided between the front support plate and the rear support plate. The horizontal support plate is located below the side of the two-dimensional arm fixing plate where the automatic two-dimensional arm is installed. The reagent storage module and the reaction module are fixed On the horizontal support plate, the reagent storage module includes at least two reagent storage positions, and the reaction module is an even number of more than two.

Owner:NANJING VAZYME MEDICAL TECH CO LTD