Patents

Literature

159results about How to "Reduce drive power consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

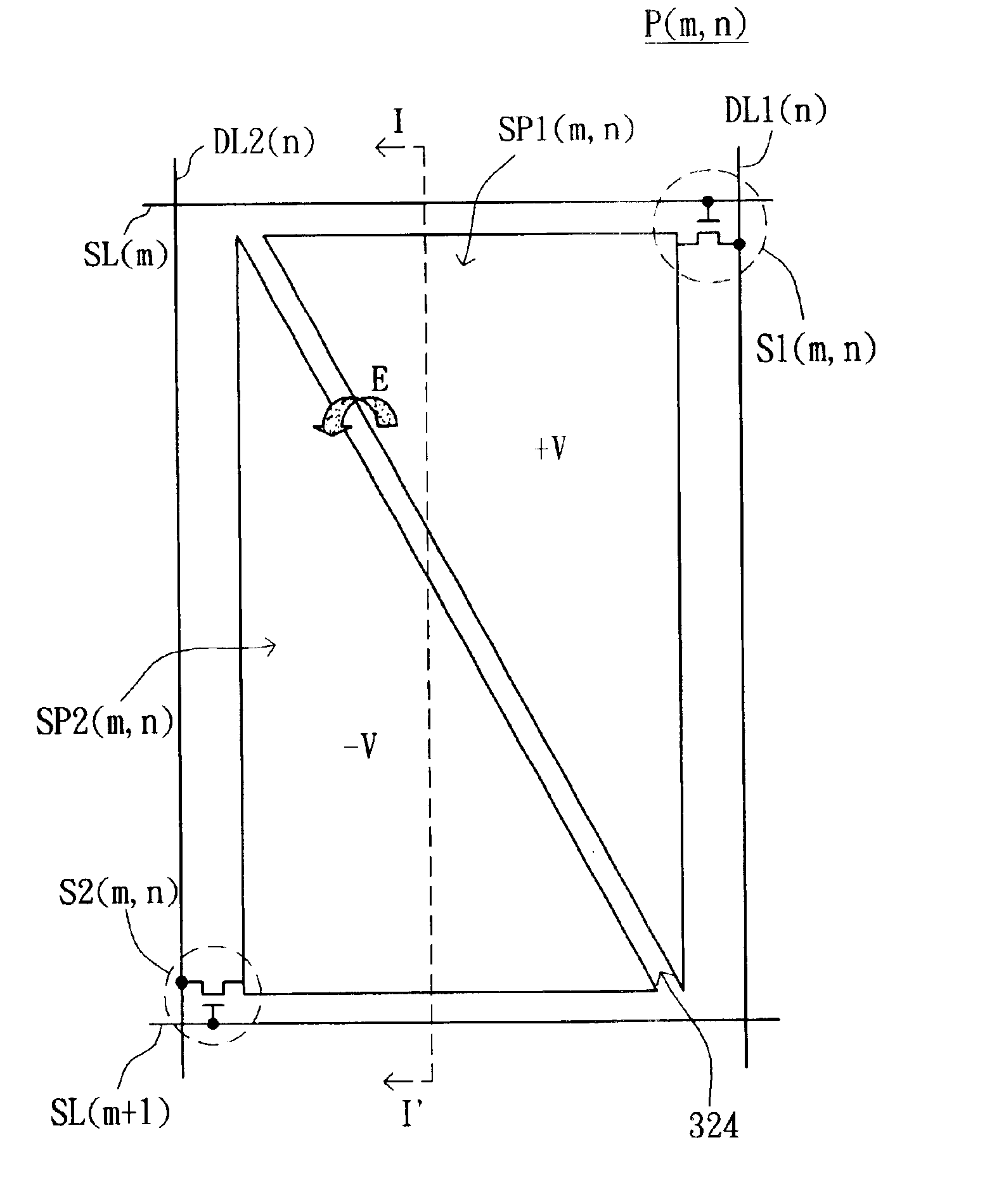

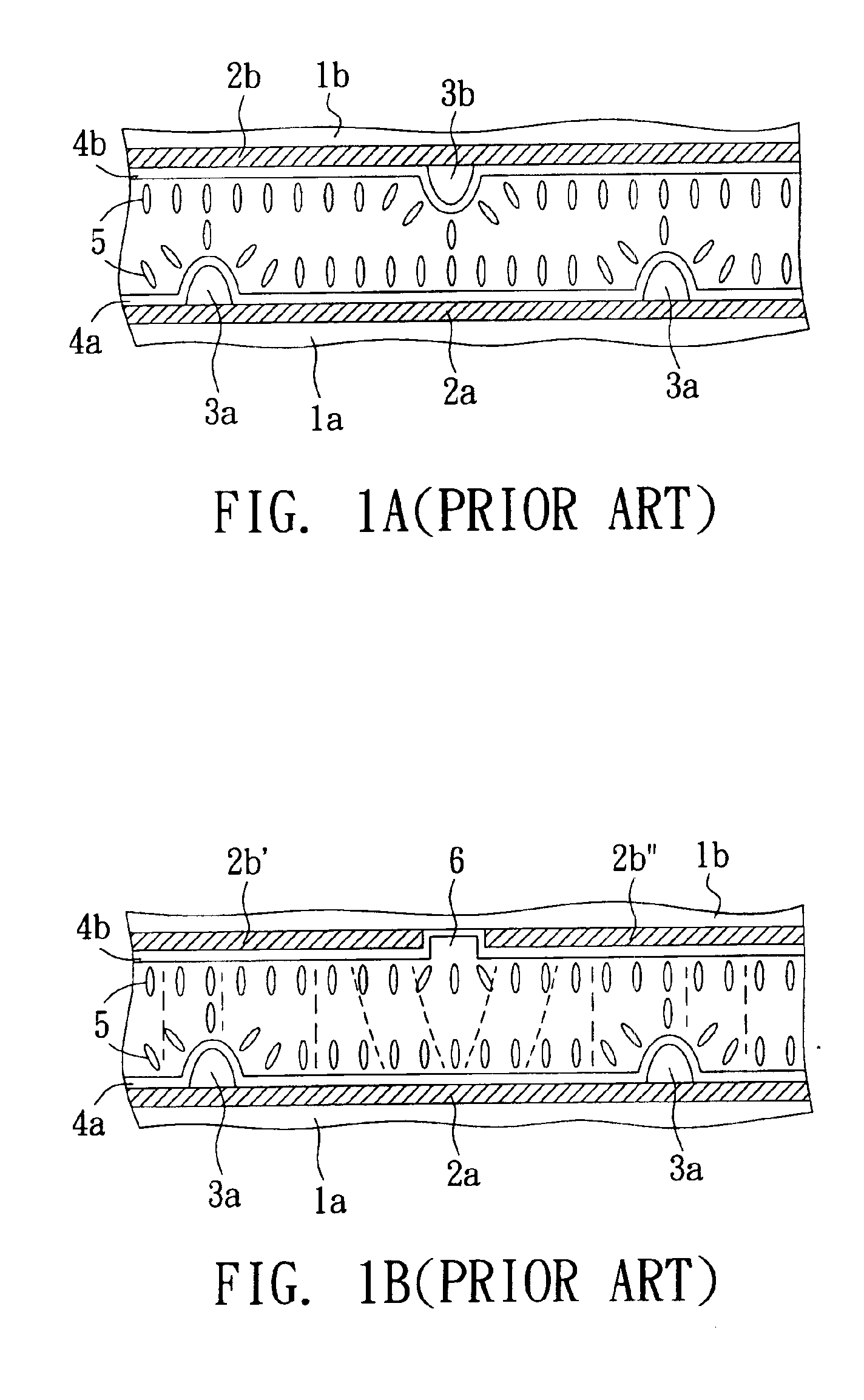

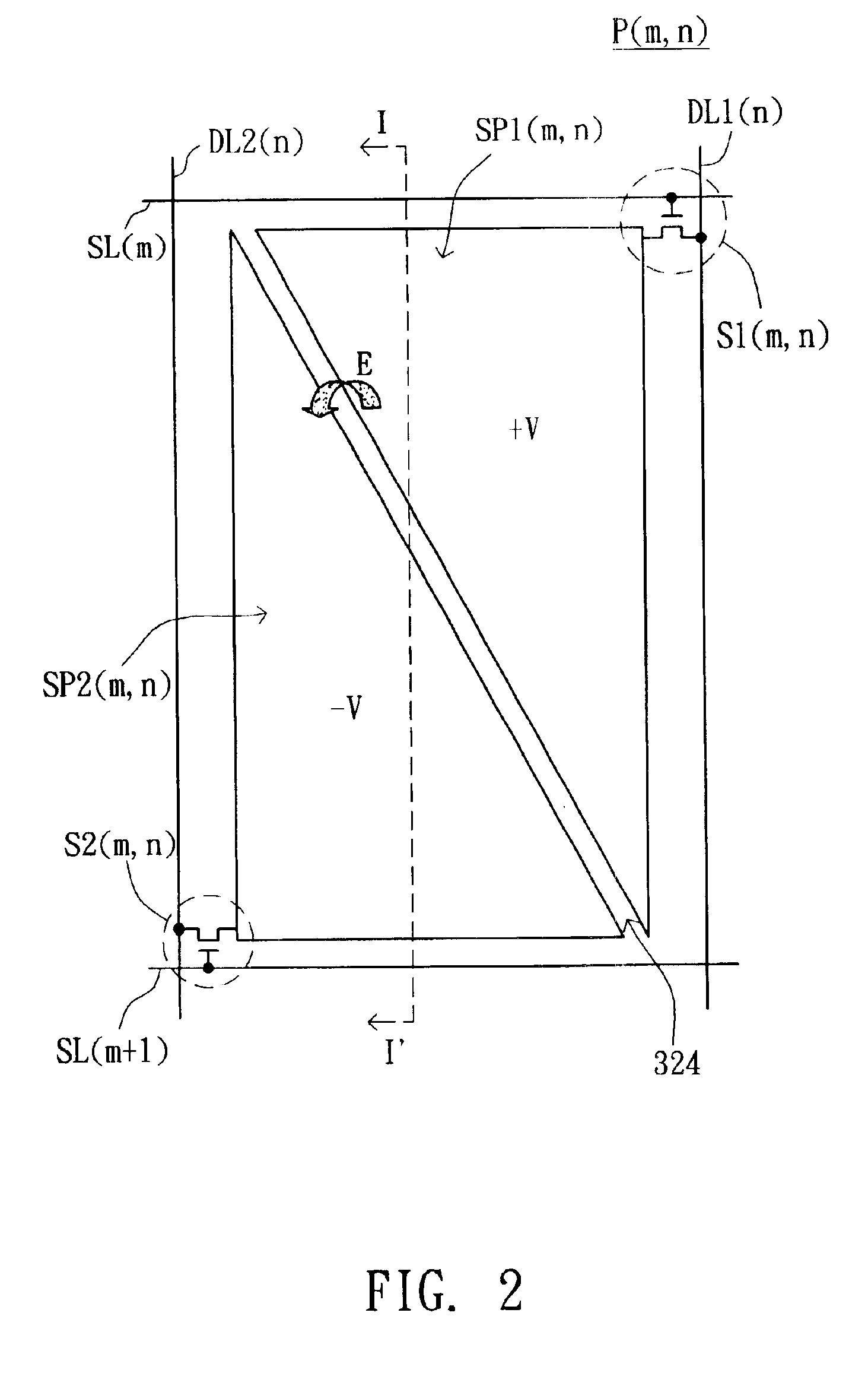

Multi-domain vertical alignment liquid crystal display and driving method thereof

InactiveUS6922183B2Short response timeFlicker phenomenon of the MVA LCD is improvedStatic indicating devicesNon-linear opticsVertical alignmentElectrical polarity

A multi-domain vertical alignment (MVA) liquid crystal display (LCD), including a first substrate and a second substrate, a common electrode, a number of pixel electrodes, a number of first switches and second switches, and liquid crystals (LCs). The common electrode is formed on one surface of the first substrate. The pixel electrodes are formed on a surface of the second substrate and are opposite to the common electrode. Each of the pixel electrodes includes a slit and a first sub-pixel electrode and a second sub-pixel electrode which are electrically isolated to each other by the slit. Each of the first switches is used for controlling corresponding first sub-pixel electrode, and each of the second switches is used for controlling corresponding second sub-pixel electrode. The liquid crystals (LCs) are sealed between the first substrate and the second substrate. The first and second sub-pixel electrodes of one of the pixel electrodes incline the liquid crystals in the proximity of the slit when the corresponding first and the second switches are enabled and data signals of opposite polarities are respectively applied to the first sub-pixel electrode and the second sub-pixel of the one of the pixel electrode.

Owner:INNOLUX CORP

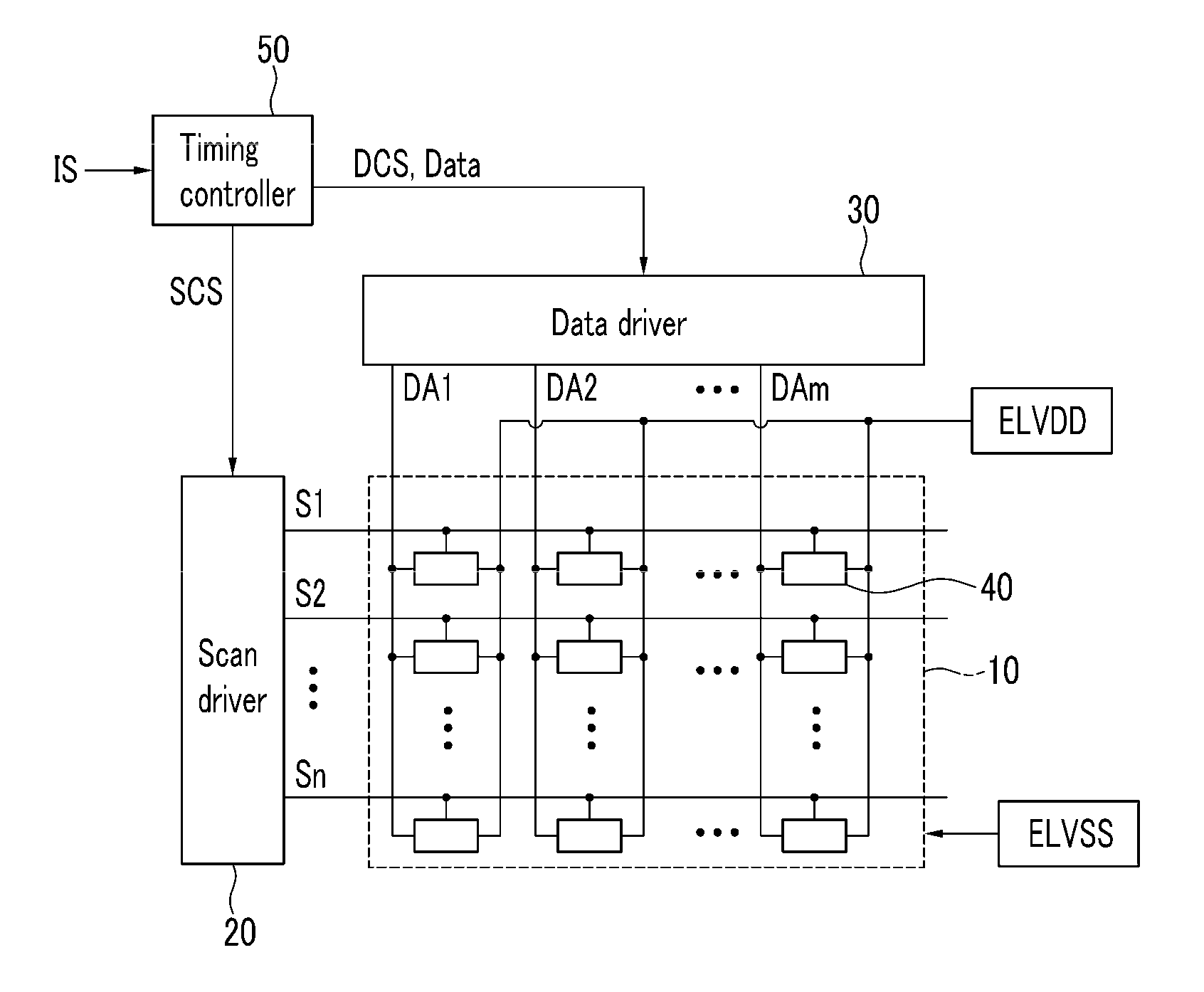

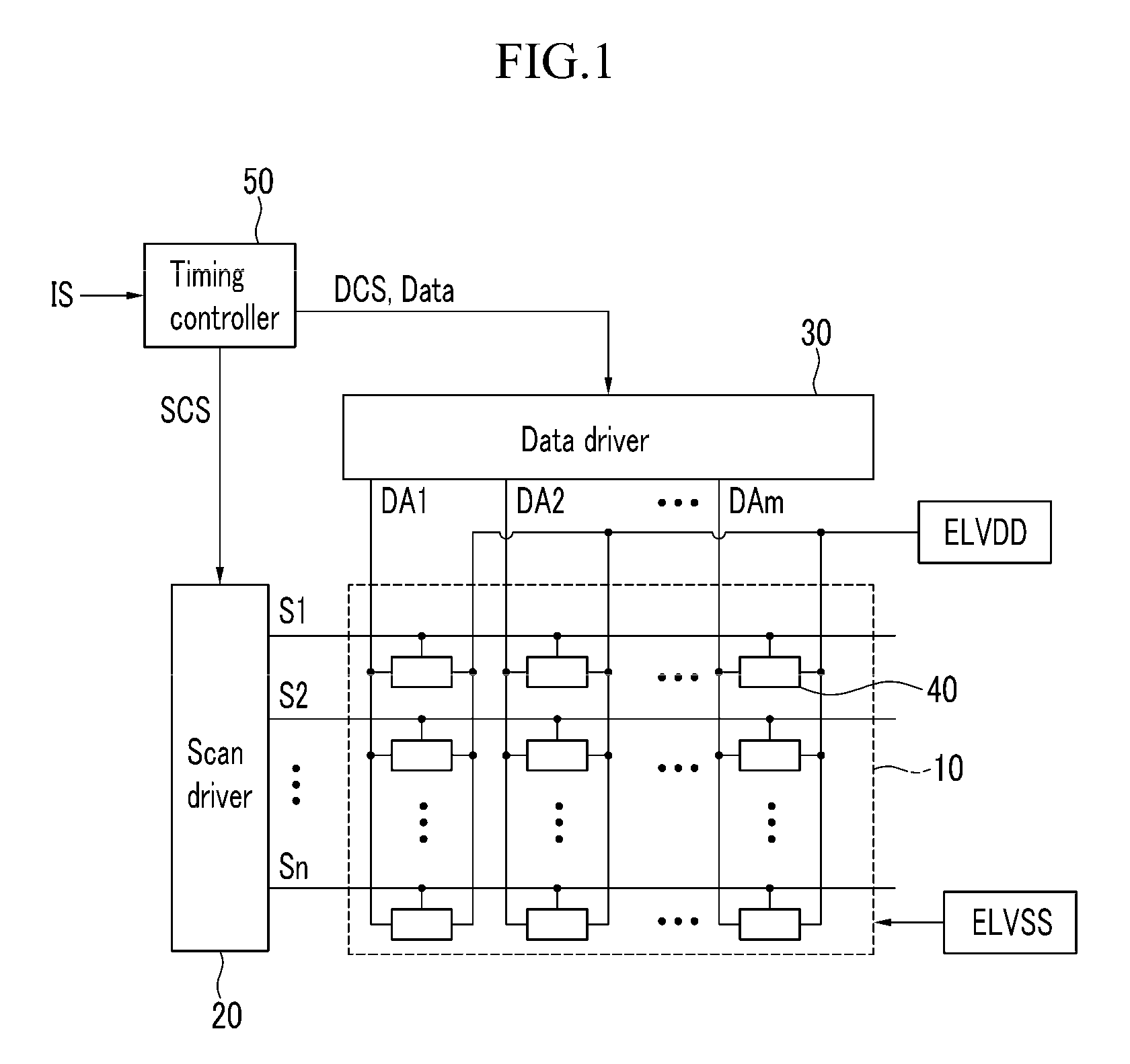

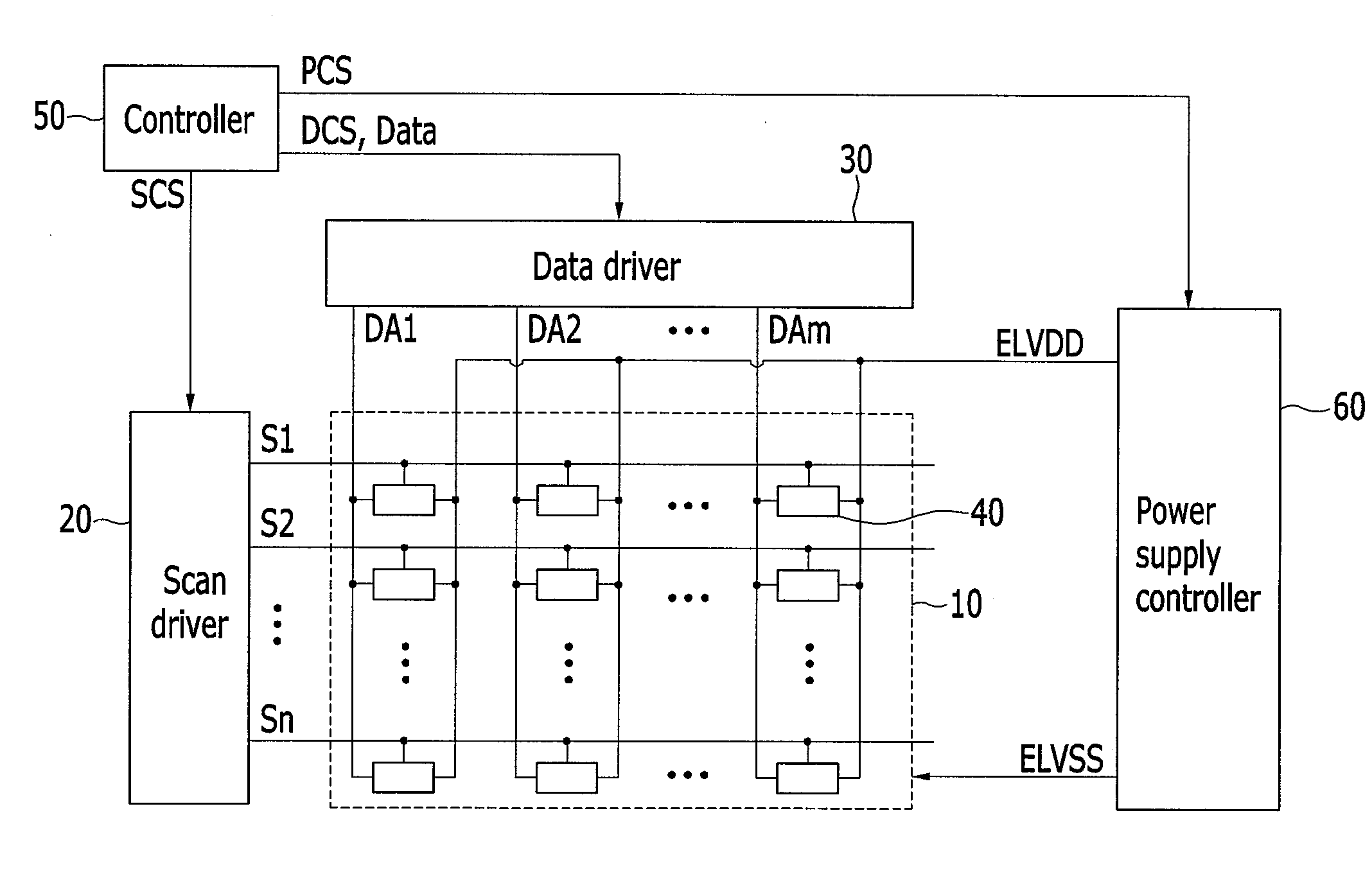

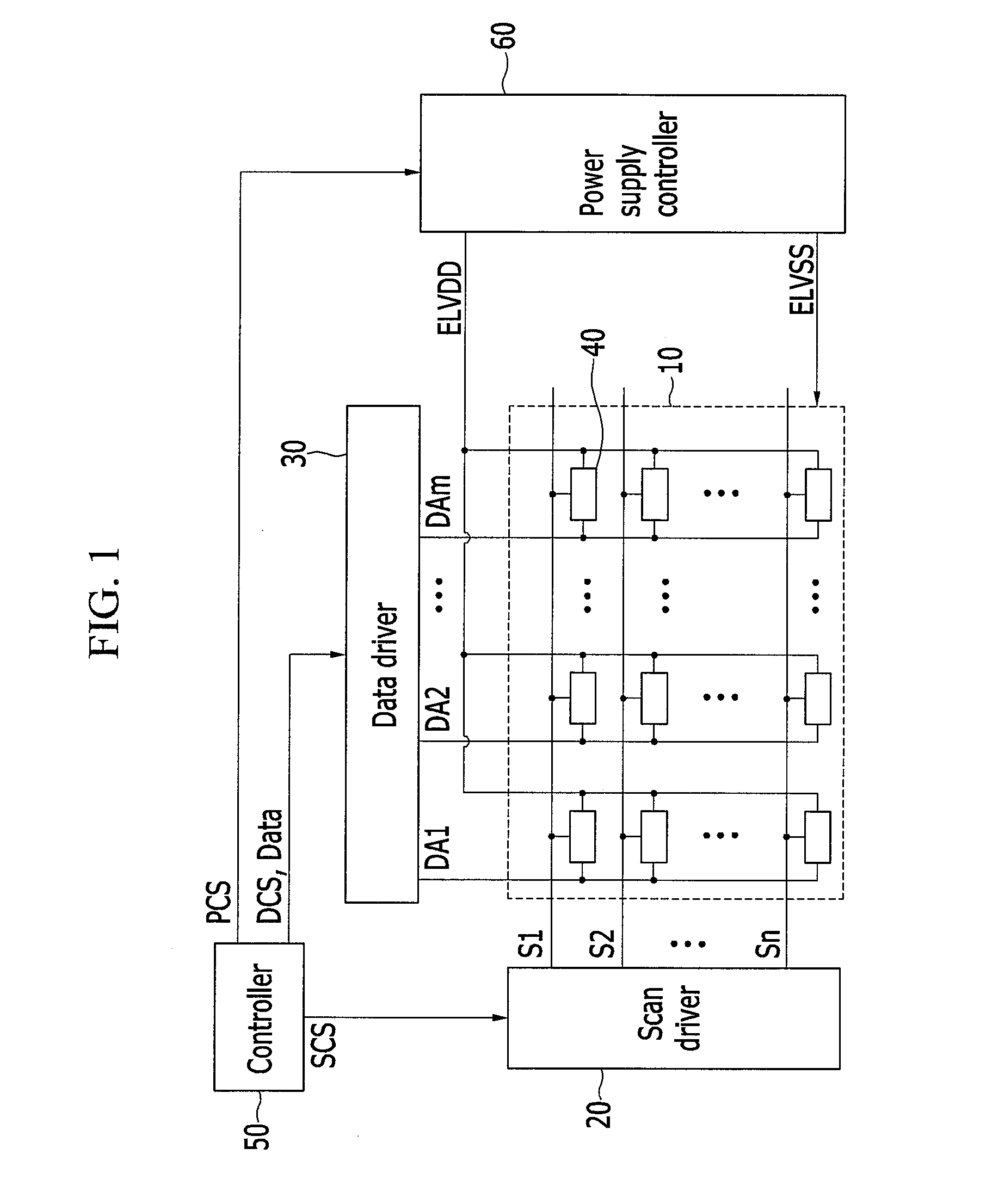

Display device and driving method thereof

ActiveUS20110292006A1Economical module production costReduce drive power consumptionCathode-ray tube indicatorsSteroscopic systemsScan lineComputer graphics (images)

A display device includes a scan driver transmitting a plurality of scan signals to a plurality of scan lines, a data driver transmitting a plurality of data signals to a plurality of data lines, a display unit including a plurality of pixels connected to corresponding scan lines and corresponding data lines, and respectively receiving the corresponding data signal when the plurality of pixels are selected with the corresponding scan signal, and a timing controller controlling the scan driver and the data driver, dividing one frame period into a first viewpoint image display period, a second viewpoint image display period, and a black image display period, and generating image data signals corresponding to the first viewpoint image display period, the second viewpoint image display period, and the black image display period, and supplying the respective image data signals to the data driver, wherein the black image display period is shorter than the first viewpoint image display period and the second viewpoint image display period, and the image data signal corresponding to the black image display period is a black image data signal controlling the plurality of pixels not to emit light.

Owner:SAMSUNG DISPLAY CO LTD

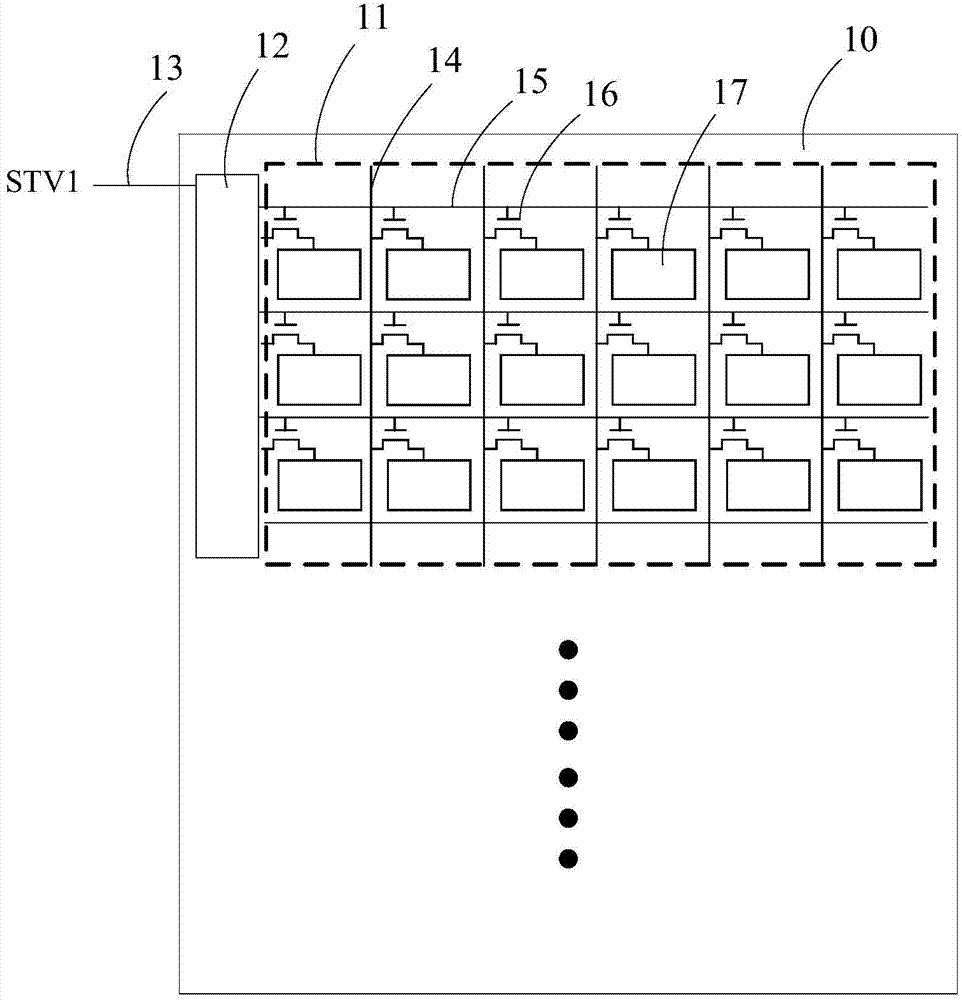

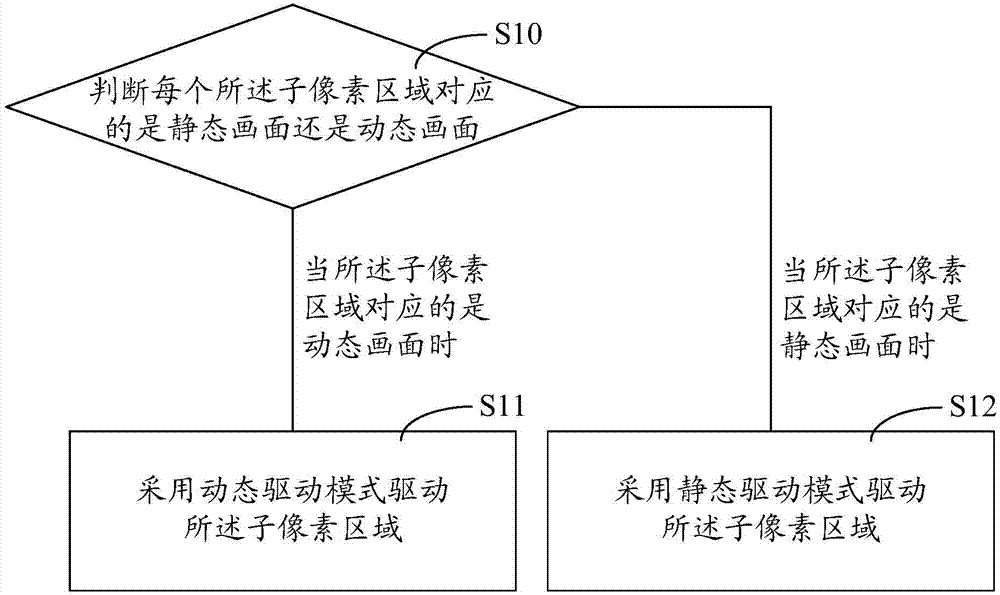

Display panel and driving method thereof

InactiveCN104123906AImprove driving efficiencyReduce drive power consumptionStatic indicating devicesEngineeringDriving mode

Disclosed are a display panel and a driving method thereof. The display panel comprises a plurality of sub-pixel areas and a plurality of sub-grid driving circuits. Every sub-pixel area is driven by the corresponding sub-grid driving circuit; every sub-grid driving circuit comprises at least one initial scanning signal end. The driving method comprises dividing the display panel into the plurality of sub-pixel areas, and determining whether every sub-pixel area corresponds to a static image or a dynamic image; when the sub-pixel area corresponds to the dynamic image, driving the sub-pixel area in a dynamic driving mode; when the sub-pixel area corresponds to the static image, driving the sub-pixel area in a static driving mode. The display panel and the driving method thereof can reduce driving power consumption.

Owner:XIAMEN TIANMA MICRO ELECTRONICS +1

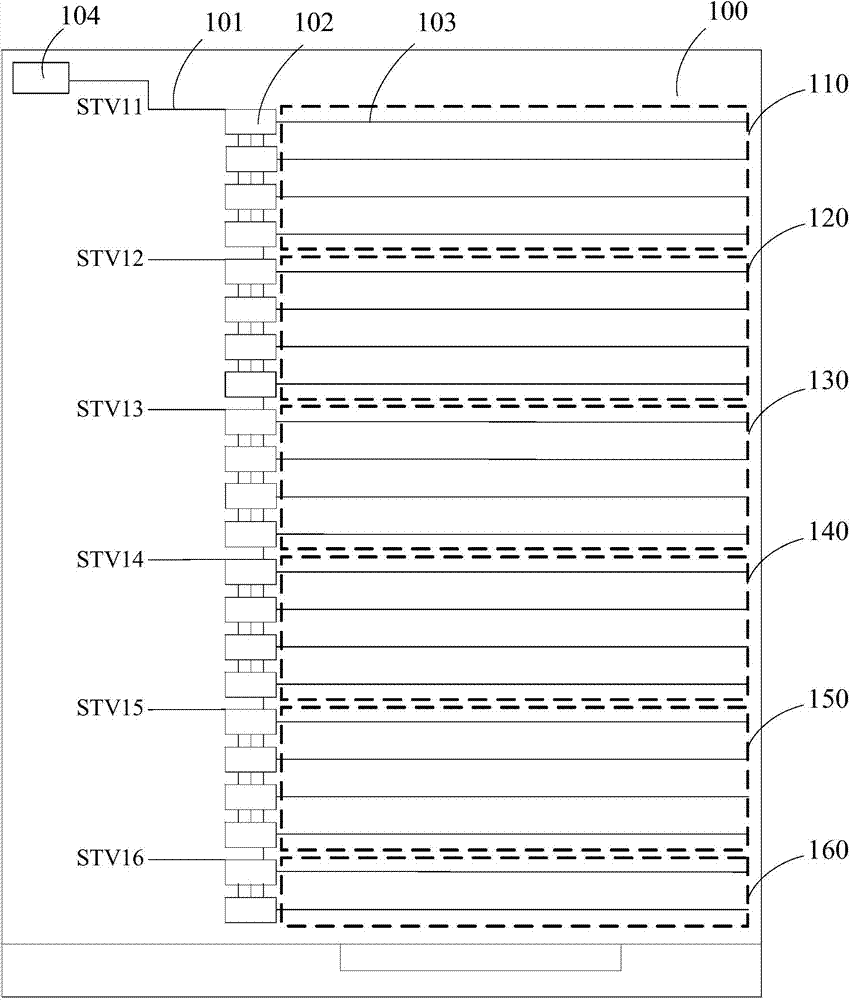

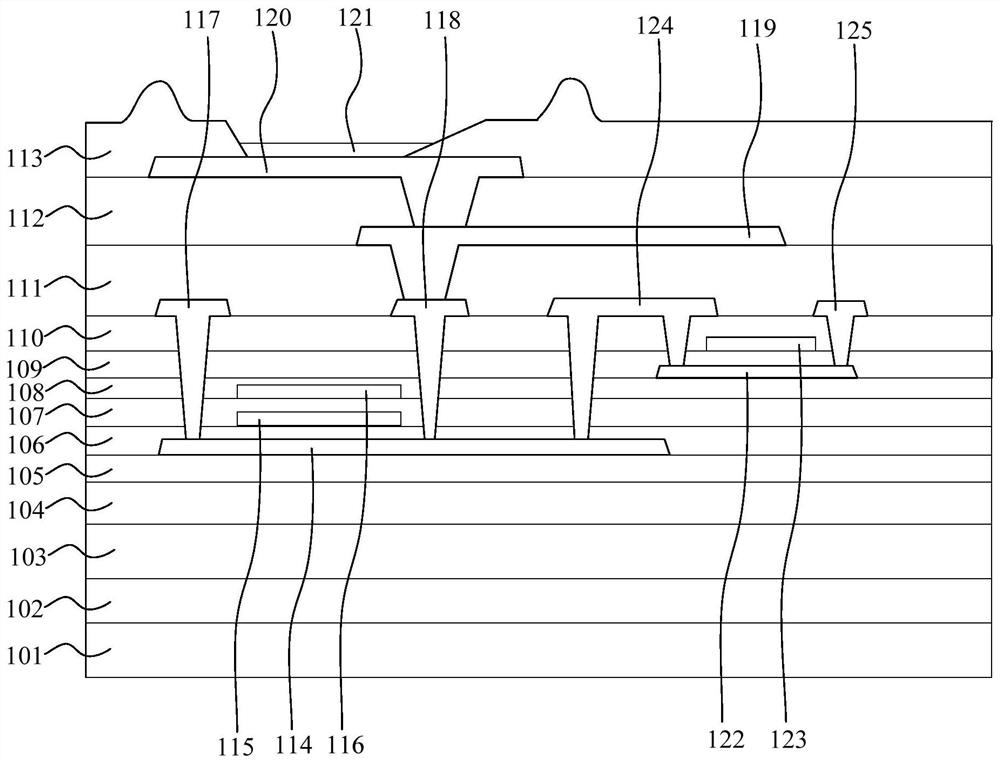

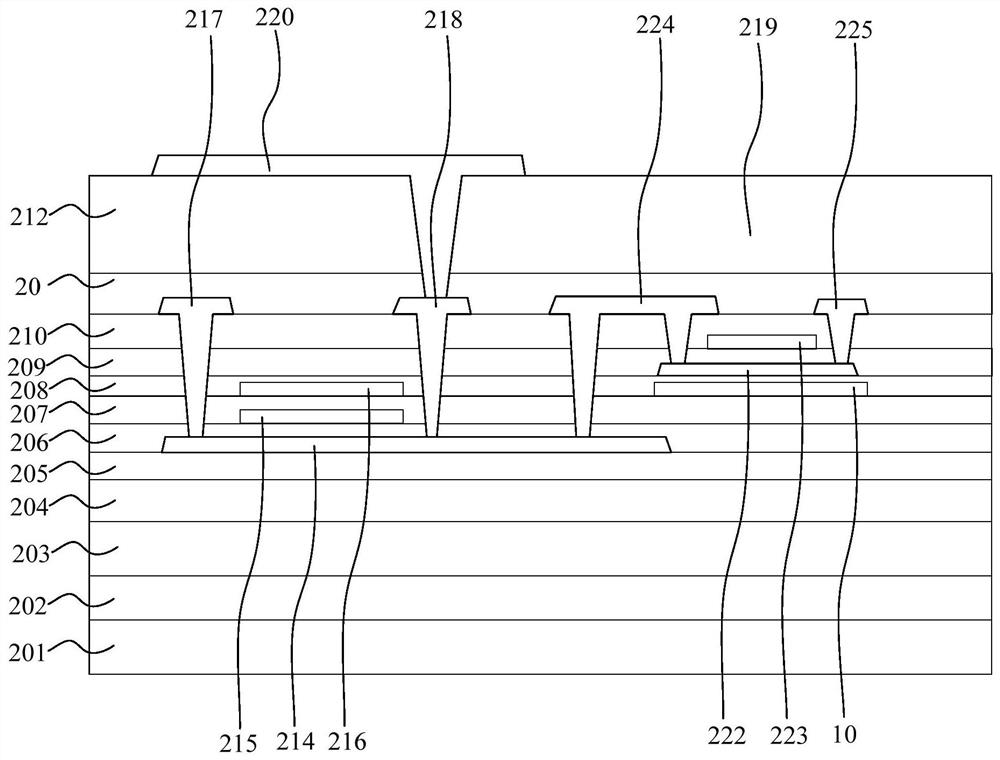

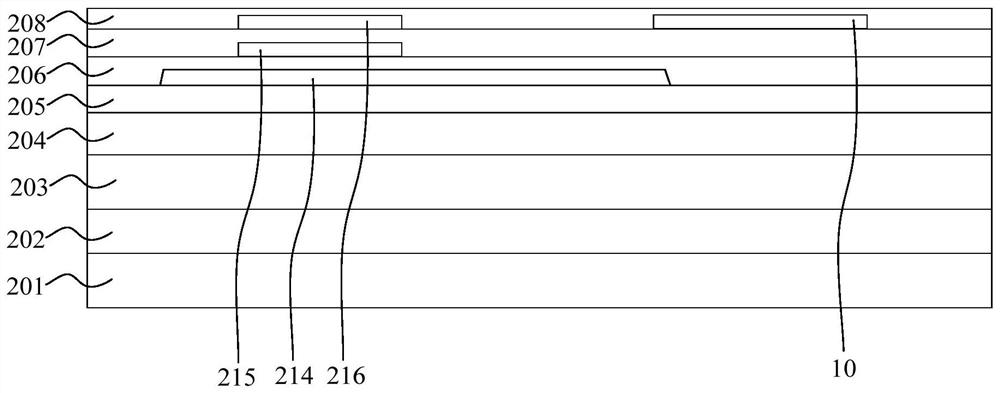

Array substrate and display panel

ActiveCN111863837APrevent feature driftImprove stabilitySolid-state devicesSemiconductor devicesOxide thin-film transistorHemt circuits

The invention provides an array substrate and a display panel. A driving circuit layer in the array substrate is formed on one side of a substrate, and the driving circuit layer comprises a low-temperature polycrystalline silicon thin film transistor and a low-temperature polycrystalline oxide thin film transistor which are electrically connected. The low-temperature polycrystalline silicon thin film transistor sequentially comprises a polycrystalline silicon active layer, a first grid electrode, a first source electrode and a first drain electrode in the direction away from the low-temperature polycrystalline silicon thin film transistor, and the low-temperature polycrystalline oxide thin film transistor sequentially comprises an oxide active layer, a second grid electrode, a second source electrode and a second drain electrode; a hydrogen barrier layer is formed on at least one side of the upper side or the lower side of the oxide active layer; a pixel electrode layer is formed on the side, away from the substrate, of the drive circuit layer, a pixel electrode is formed through patterning, and the pixel electrode is connected with the first source electrode or the first drain electrode. The hydrogen barrier layer can prevent hydrogen ions in other film layers from invading the oxide active layer to cause device characteristic drift, so that the performance of the transistorsis improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

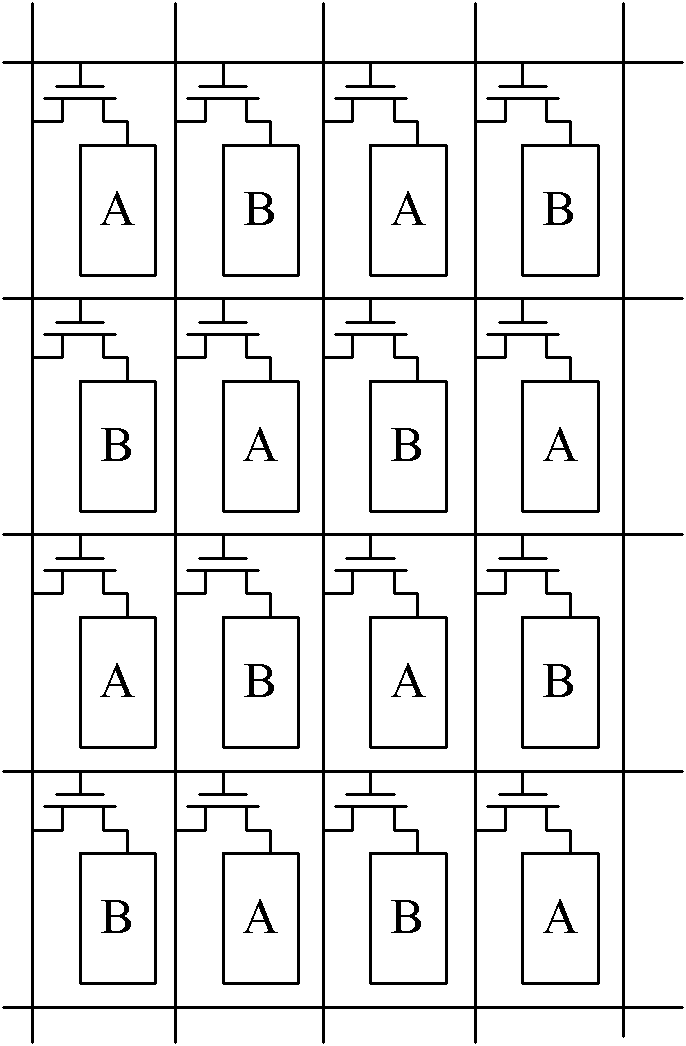

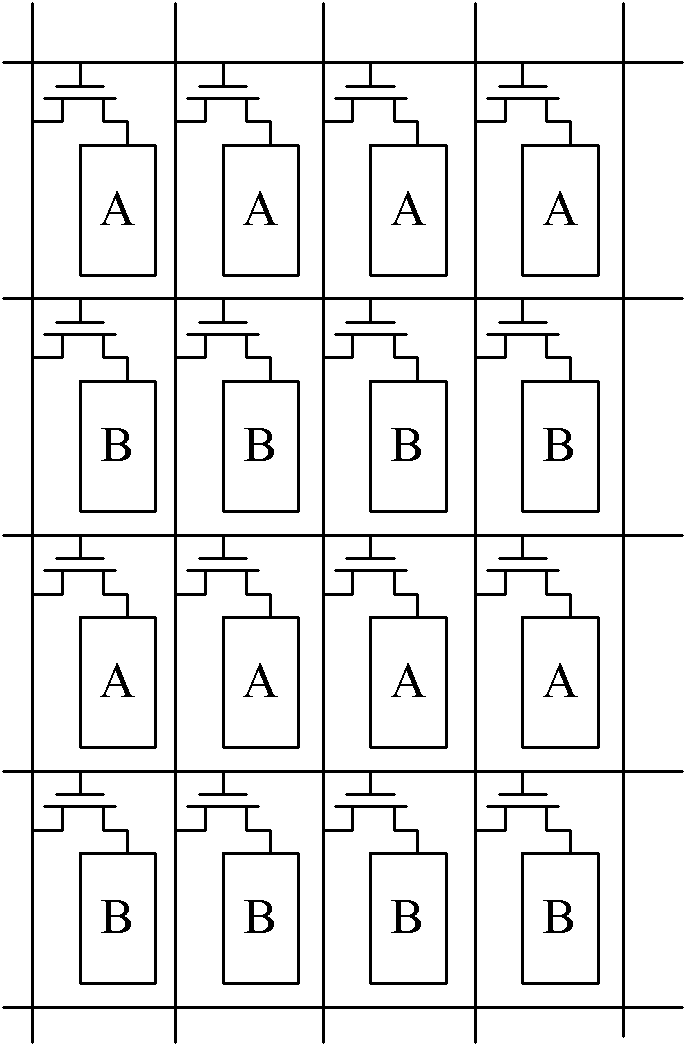

Array substrate, display device and drive method thereof

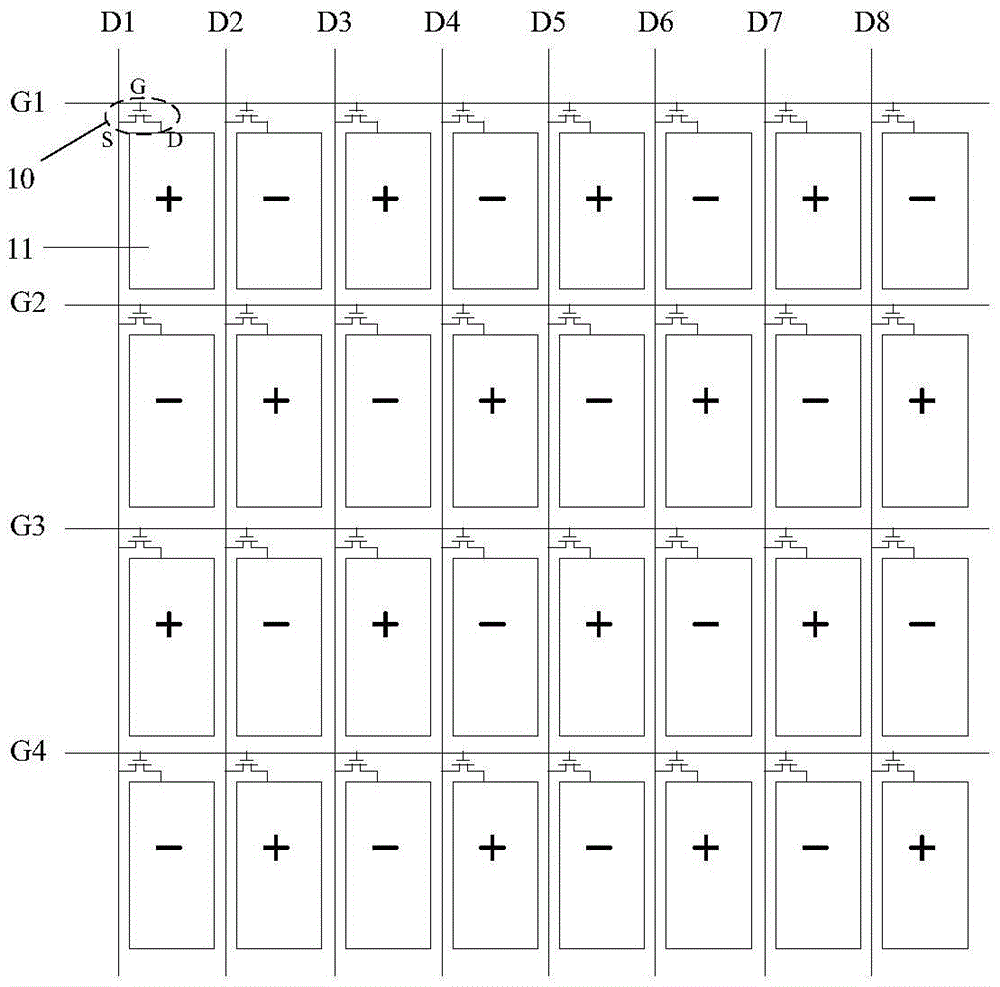

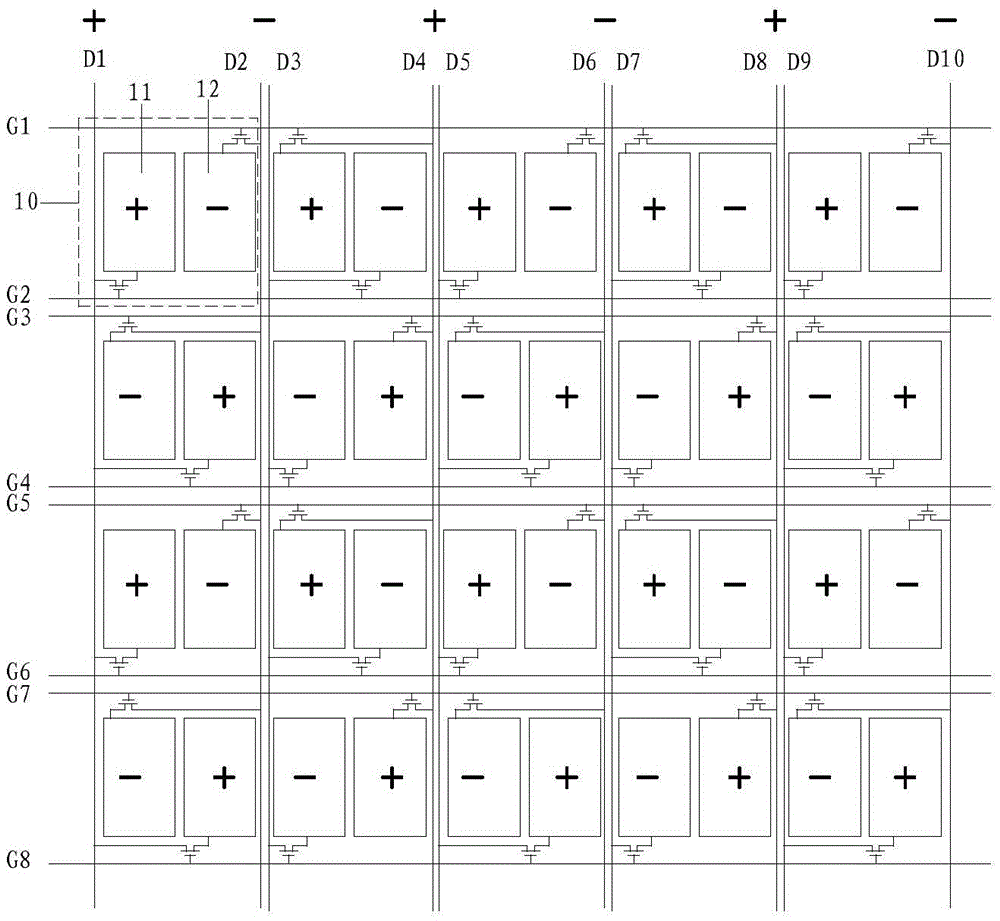

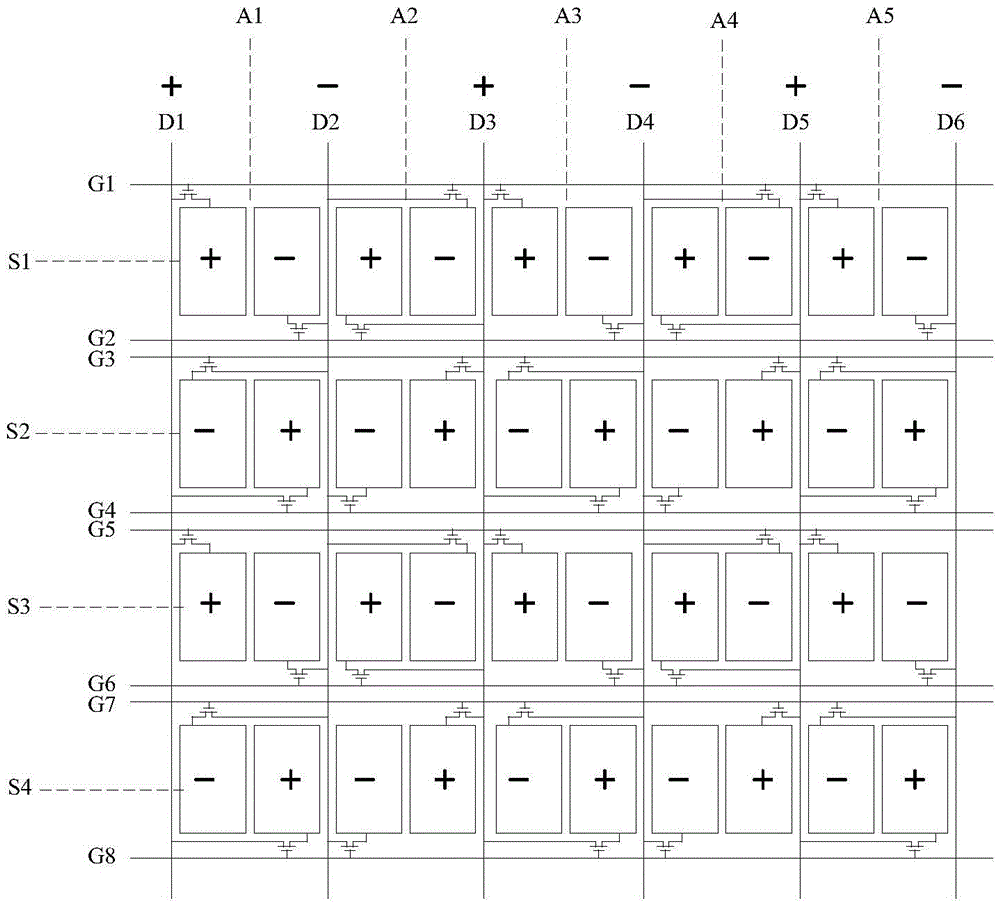

InactiveCN105629611AReduce drive power consumptionAchieve reversalStatic indicating devicesNon-linear opticsDisplay deviceEngineering

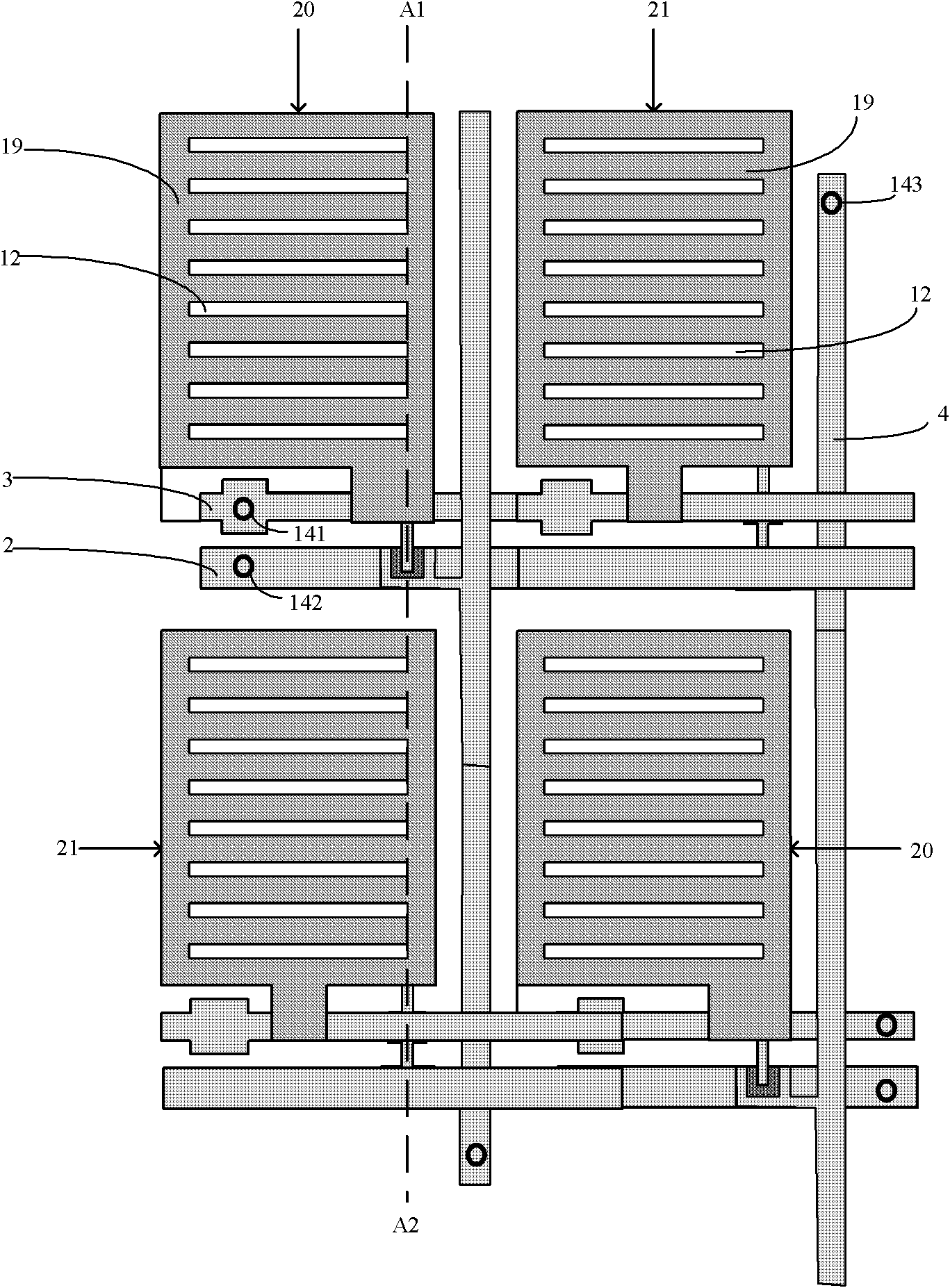

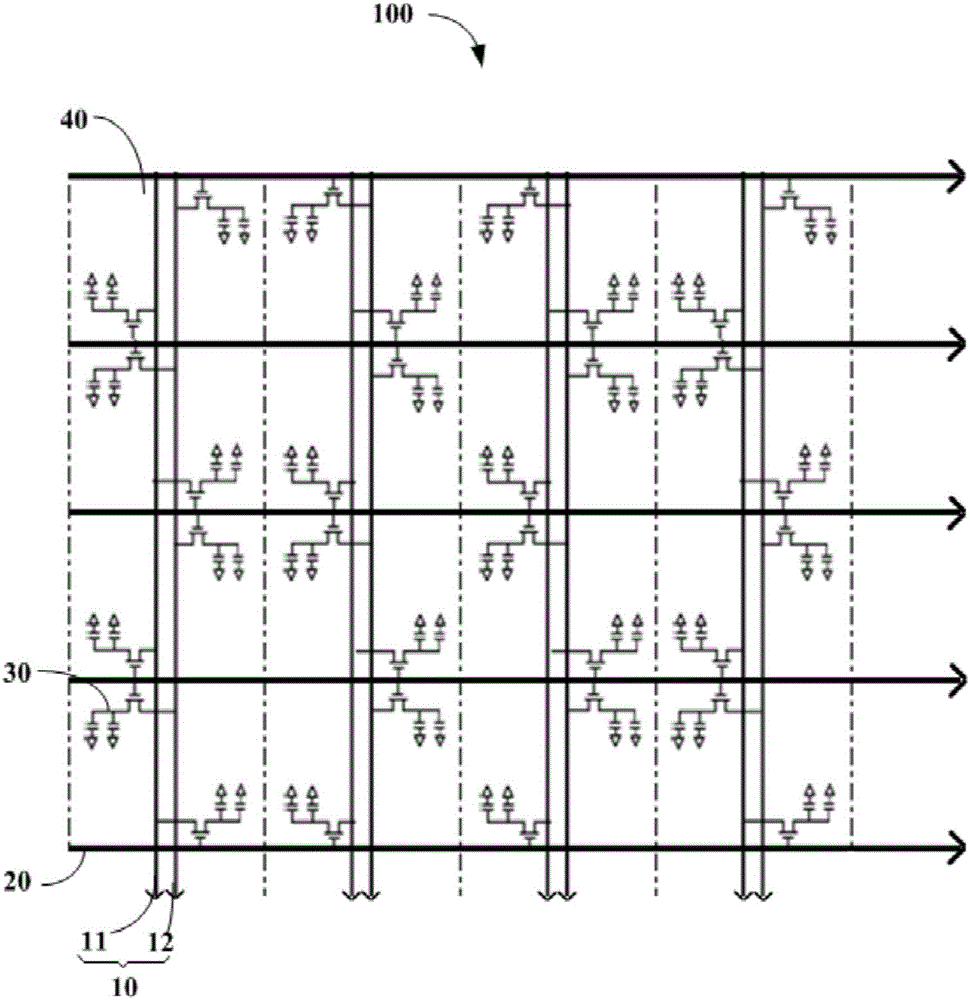

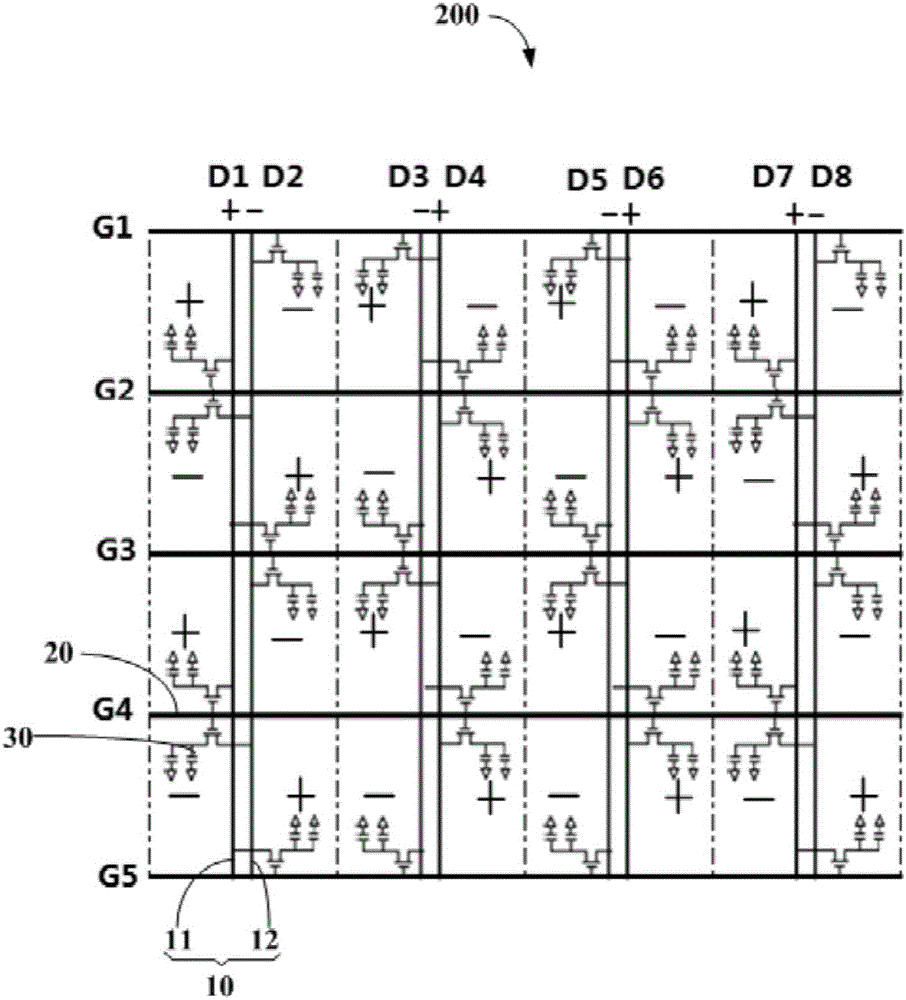

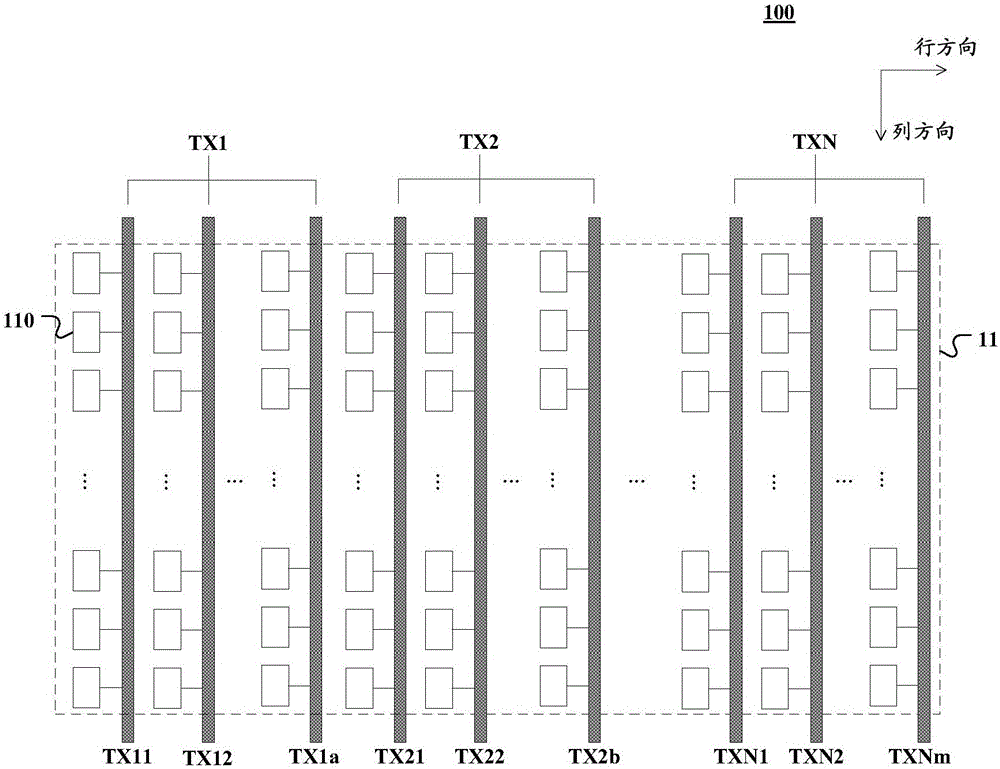

The invention provides an array substrate, a display device and a drive method thereof and relates to the technical field of display.The array substrate is used for achieving point reverse in the line direction when data lines have low drive power consumption.The array substrate comprises multiple parallel grid lines, multiple parallel data lines and multiple sub-pixel units, wherein the data lines and the grid lines are arranged in an intersecting mode, each sub-pixel unit is composed of a first sub-pixel and a second sub-pixel which are arrayed according to the same sequence in the grid line direction, each line of pixel units in the grid line direction are driven by the two grid lines, and the different sub-pixel units are driven by the different grid lines.Each row of sub-pixel units in the data line direction are driven by the two data lines.The first sub-pixel and the second sub-pixel in each sub-pixel unit are driven by the different grid lines and the different data lines.All the sub-pixels in the odd number line in any row of sub-pixels are driven by the same data lines, and all the sub-pixels in the even number lines are driven by the same data lines.The array substrate is used for manufacturing the display device.

Owner:BOE TECH GRP CO LTD +1

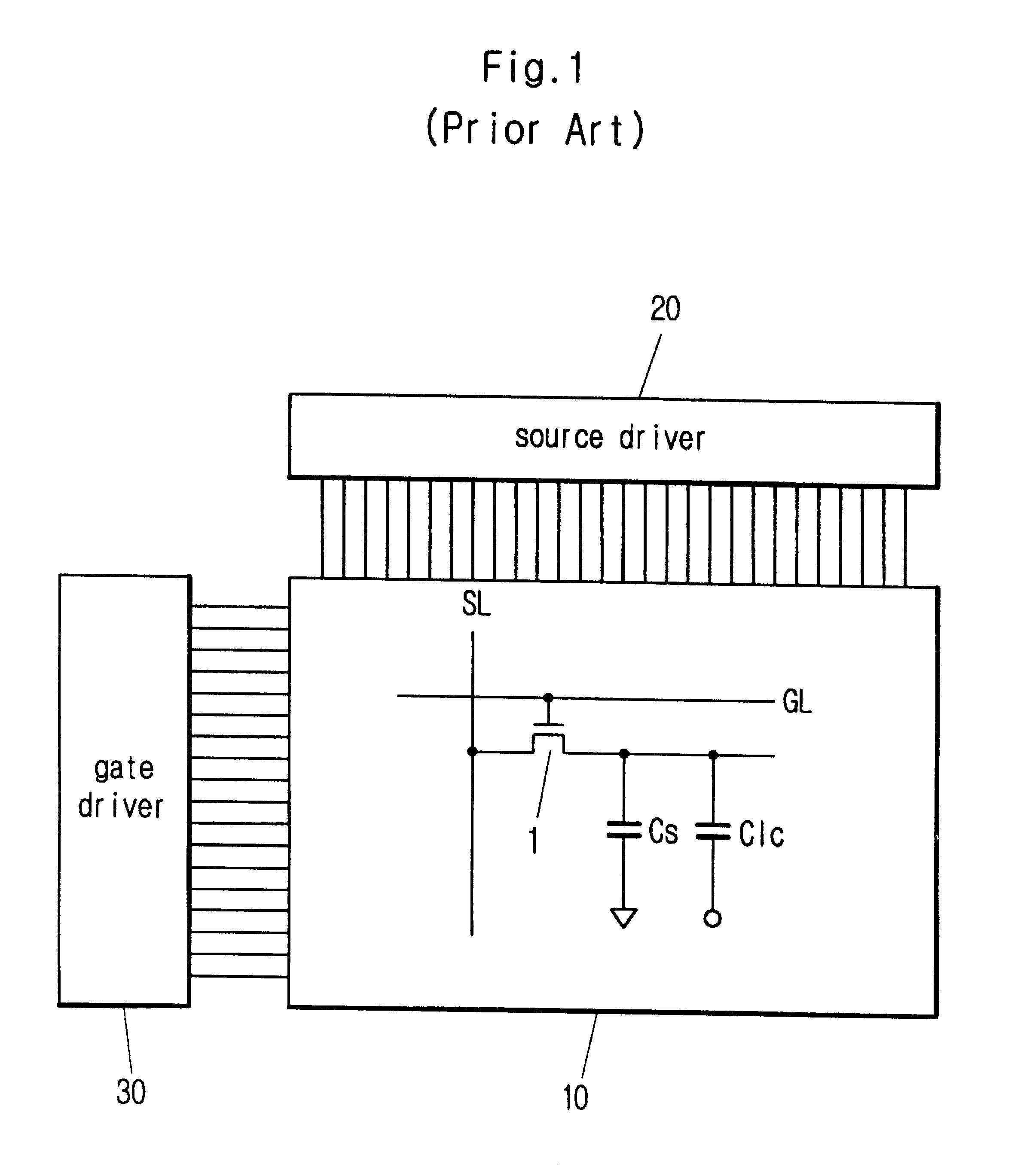

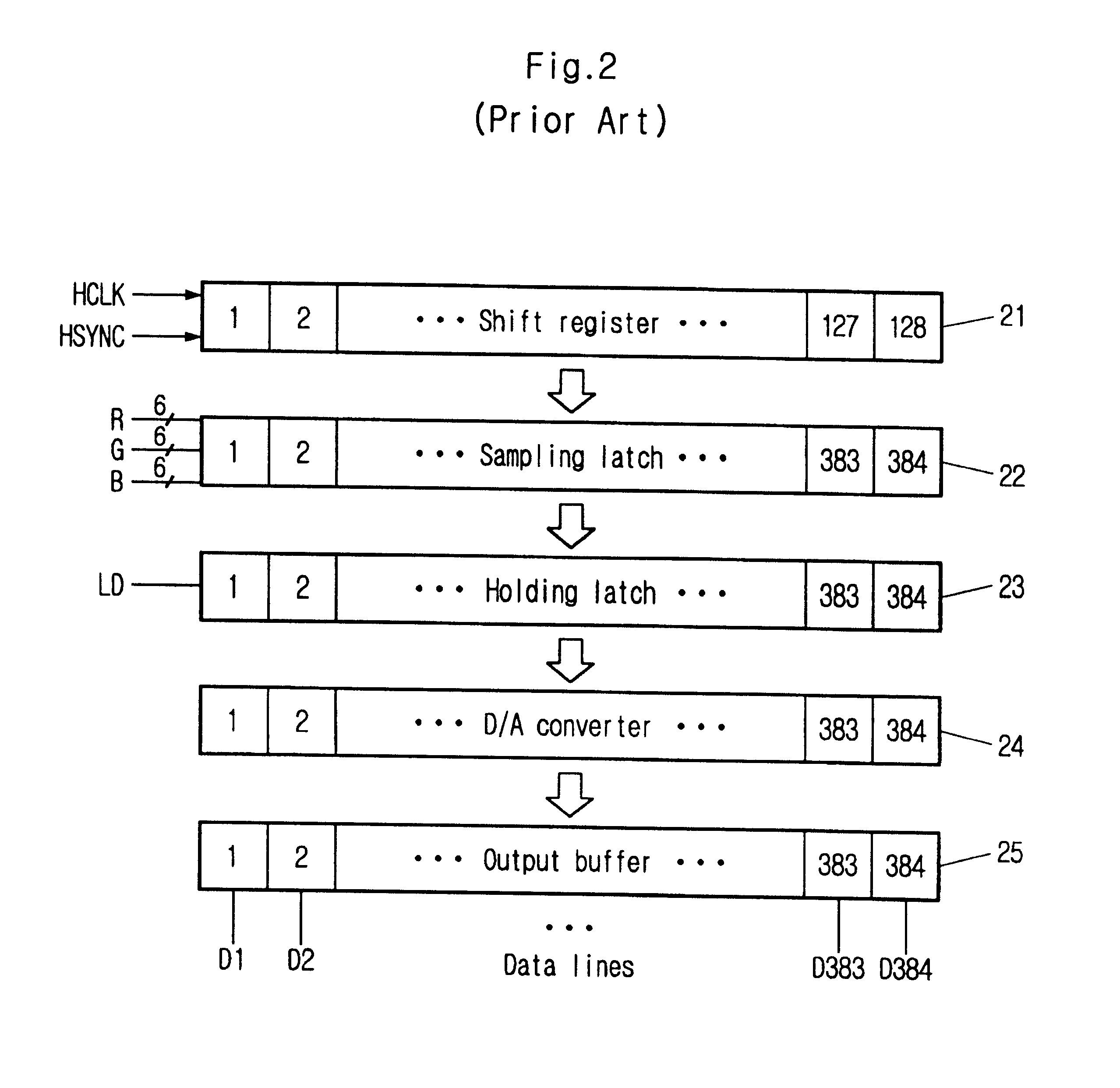

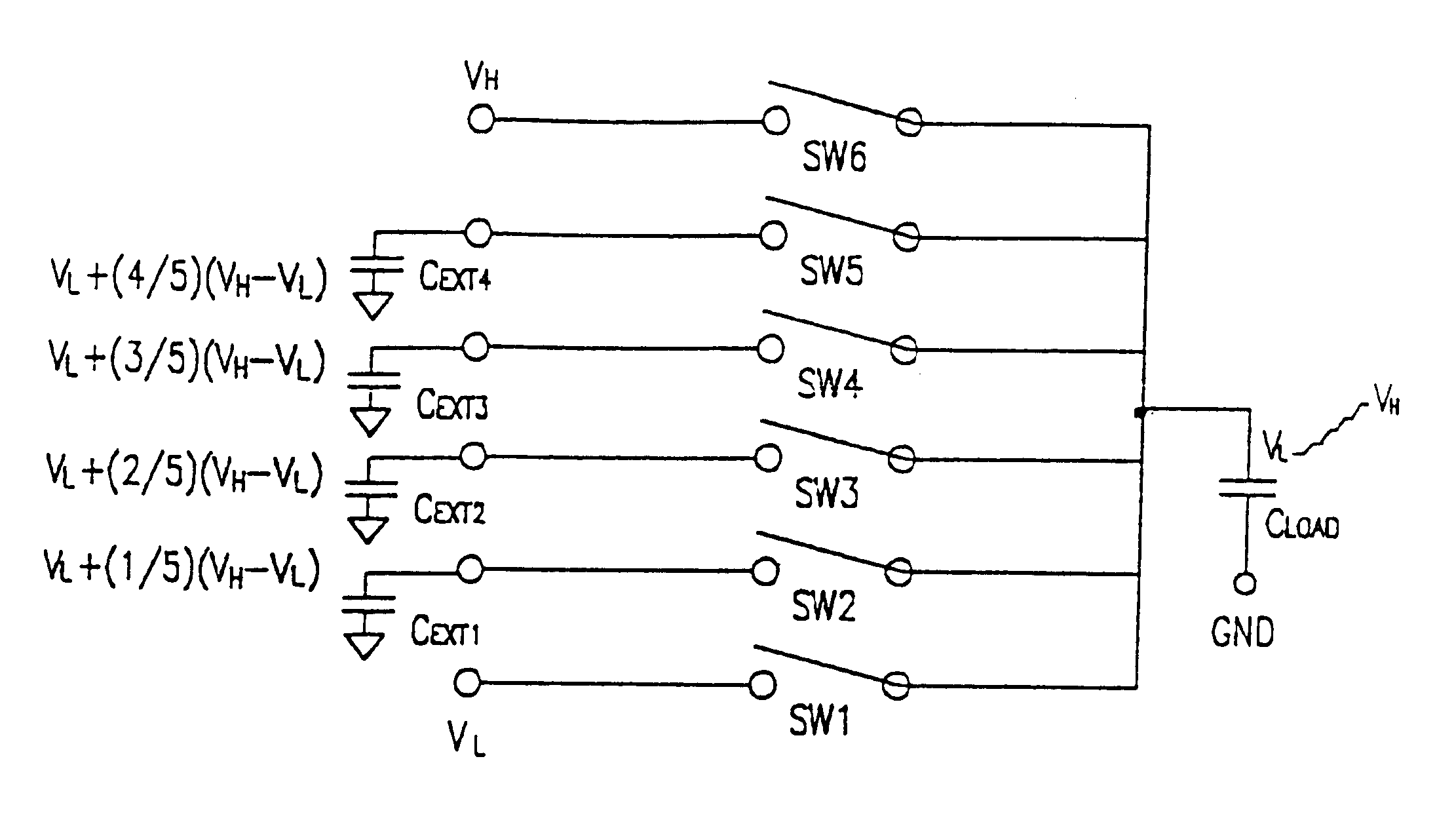

Circuit for driving source of liquid crystal display

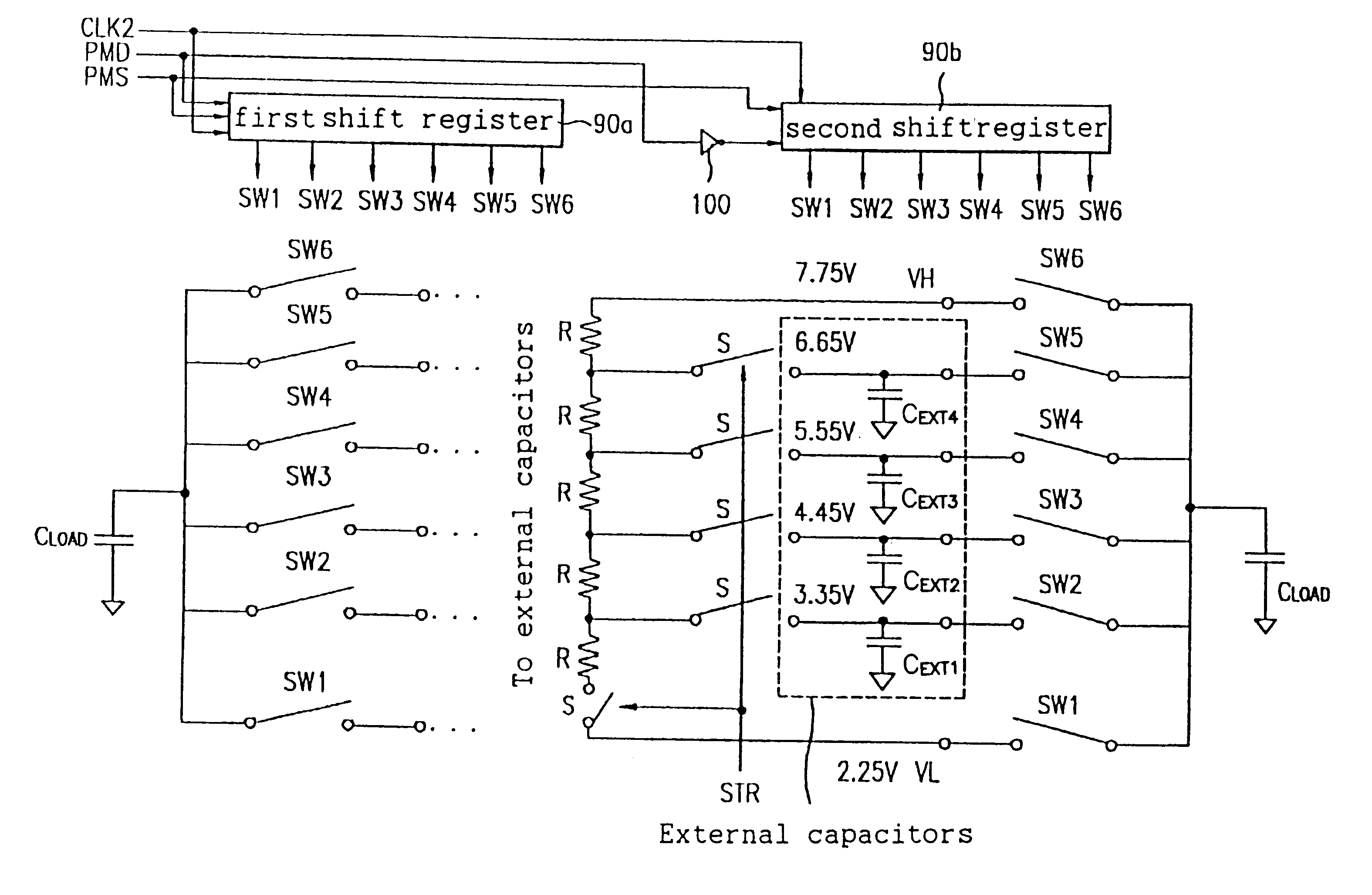

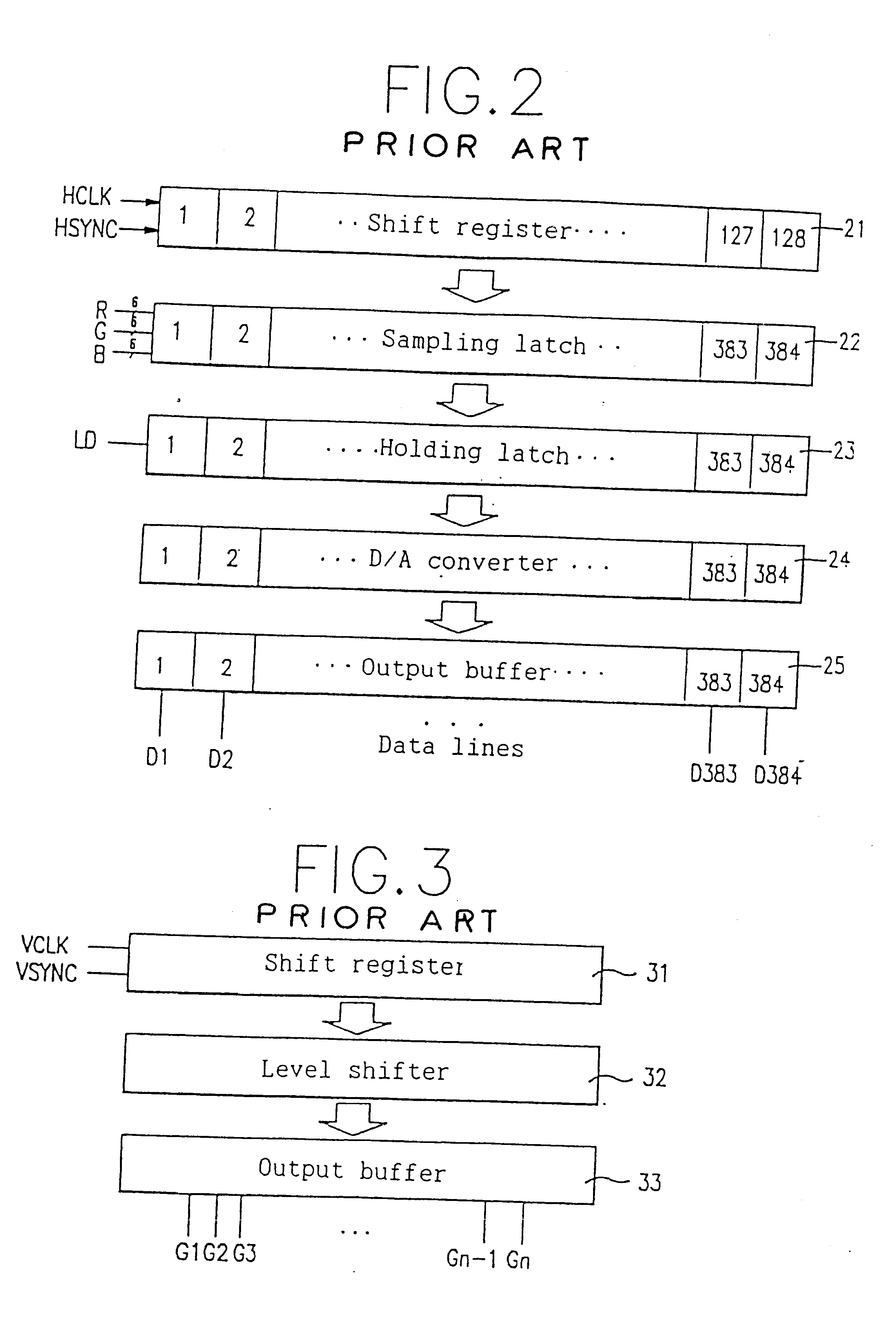

InactiveUS6538631B1Reduce power consumptionReduce drive power consumptionTelevision system detailsCathode-ray tube indicatorsLiquid-crystal displayElectrical polarity

There is provided a source driving circuit in a liquid crystal display, which applies negative and positive video signals to source lines of the liquid crystal display including a first and second plates and a liquid crystal being inserted therebetween, in which each video signal is applied, with its voltage being divided two phases of polarity modulation and gray scale decision. The polarity modulation is accomplished through stepwise charging and discharging.

Owner:SAMSUNG ELECTRONICS CO LTD

Array substrate, manufacturing method of array substrate, liquid crystal panel and liquid crystal display

ActiveCN102629059AReduce drive power consumptionReverse implementationStatic indicating devicesSolid-state devicesLiquid-crystal displayTransparent conducting film

The invention discloses an array substrate, a manufacturing method of the array substrate, a liquid crystal panel and a liquid crystal display, relates to the technical field of liquid crystal display, and aims to reduce the driving power consumption required by reverse driving. The array substrate comprises a substrate base plate, grid lines, data lines and pixel units; each pixel unit comprises two layers of transparent conducting films and a thin film transistor; the pixel units are divided into first pixel units and second pixel units; the first pixel units and the second pixel units are arranged at intervals in the directions of the data lines; in each first pixel unit, the first layer of transparent conducting film is electrically connected with a corresponding common electrode wire, and the second layer of transparent conducting film is electrically connected with a drain electrode of the corresponding thin film transistor; in each second pixel unit, the first layer of transparent conducting film is electrically connected with the drain electrode of the corresponding thin film transistor, and the second layer of transparent conducting film is electrically connected with the corresponding common electrode wire; and the common electrode wires in all the pixel units are electrically connected. The array substrate, the manufacturing method of the array substrate, the liquid crystal panel and the liquid crystal display are applied to the technical field of the liquid crystal display.

Owner:BOE TECH GRP CO LTD +1

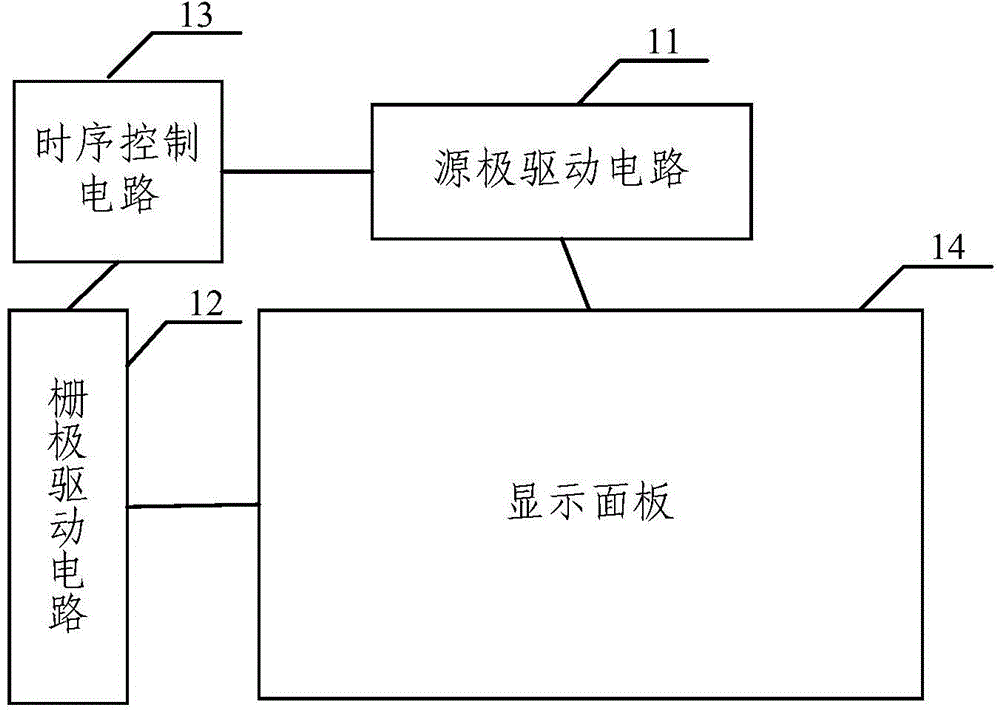

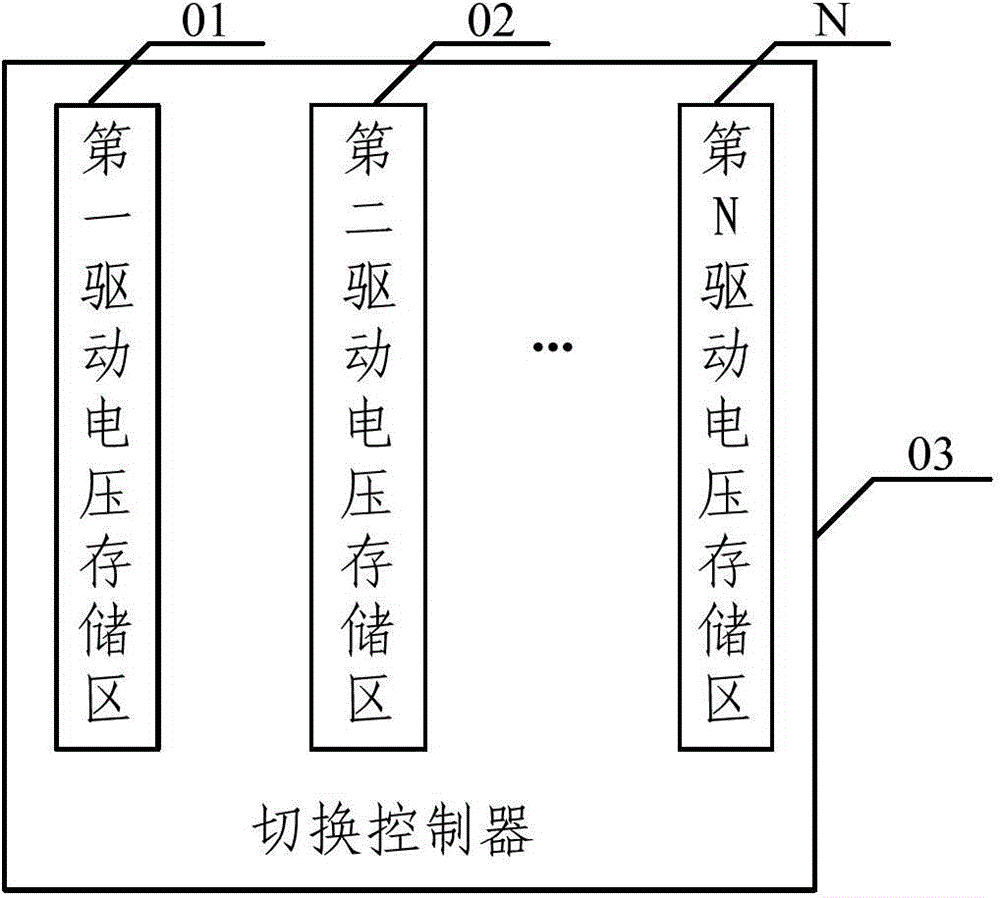

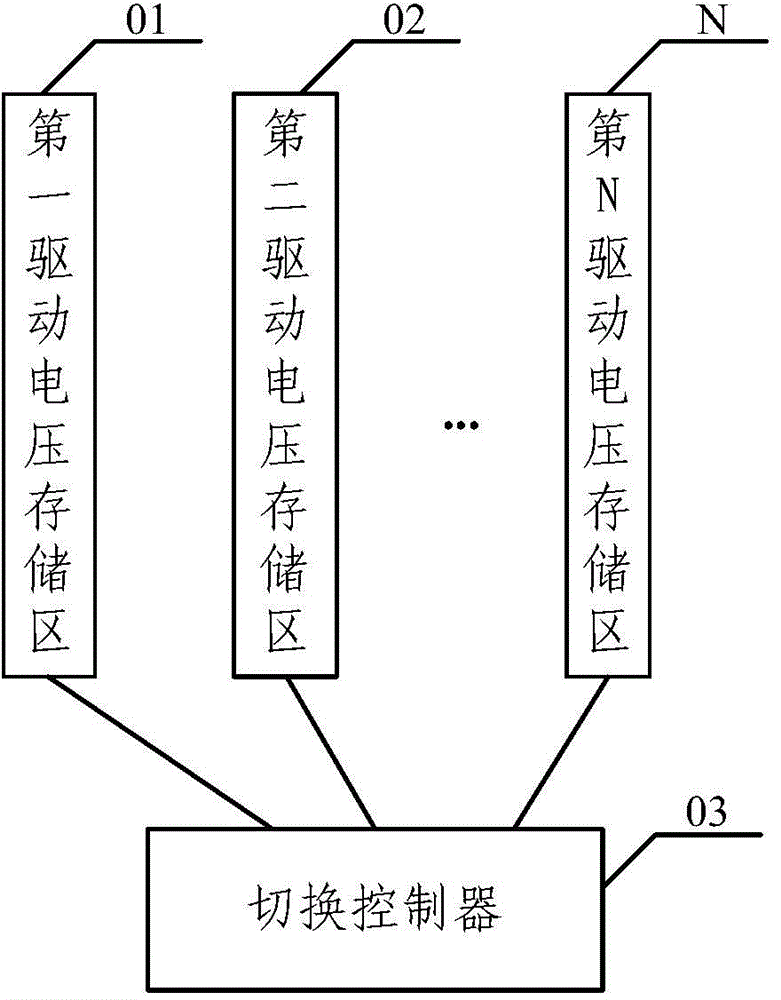

Display panel driving circuit, control method of display panel driving circuit and display device

InactiveCN103915073AReduce drive power consumptionReduce power consumptionStatic indicating devicesDisplay deviceEngineering

The invention discloses a display panel driving circuit, a control method of the display panel driving circuit and a display device. The display panel driving circuit comprises a switch controller and at least two driving voltage storage areas, wherein the switch controller controls the switching between the driving voltages stored in different driving voltage storage areas according to control instructions. By the adoption of the display panel driving circuit, a control instruction can be generated when a USB line is connected in specific environments such as USB3.0, and then a current driving voltage storage area for controlling driving is switched to another driving voltage storage area; the source driving voltage stored in the area is reduced after switching, driving power consumption for display of the display panel is reduced, and then the power consumption of the whole display panel is reduced so that energy can be saved.

Owner:BOE TECH GRP CO LTD +1

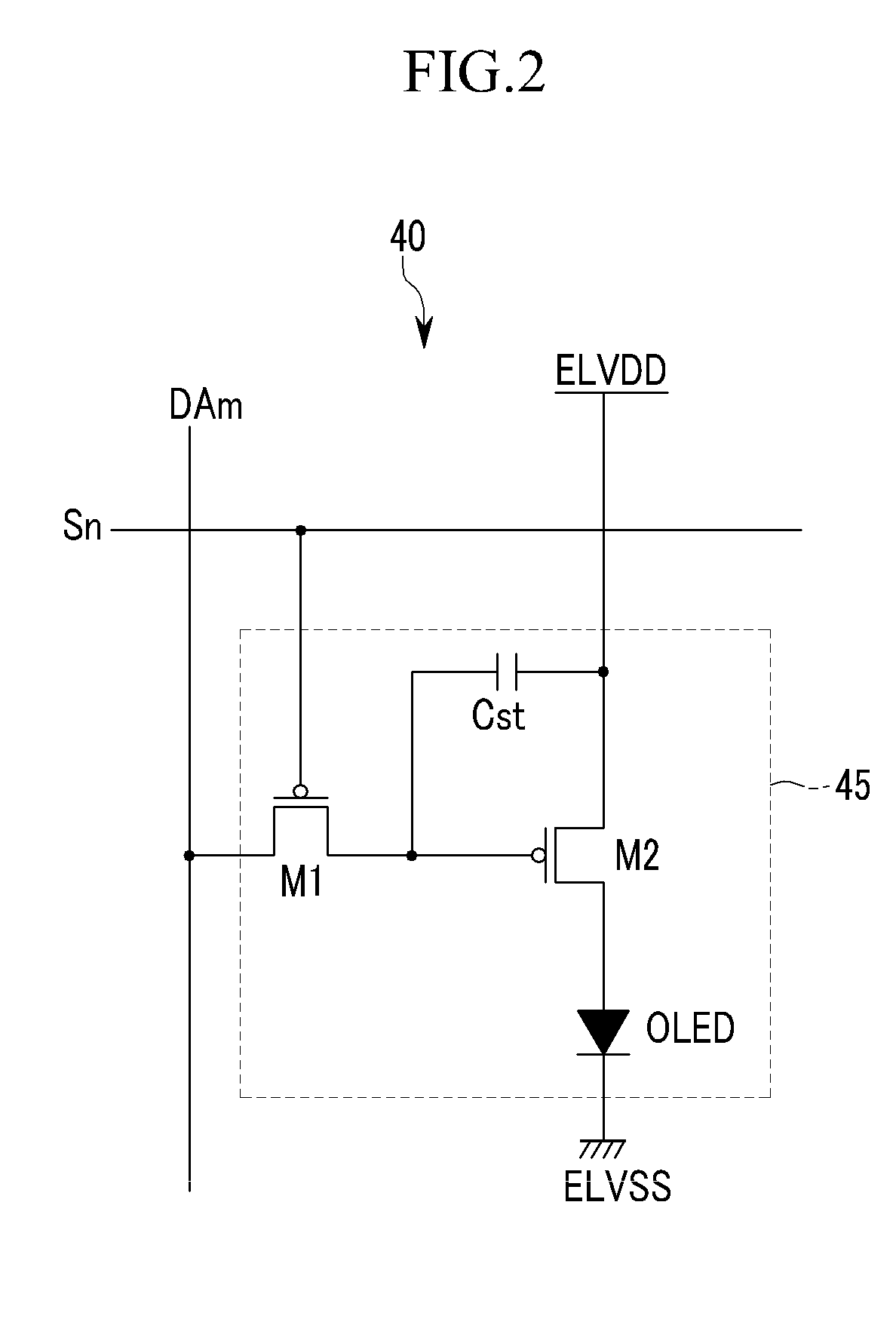

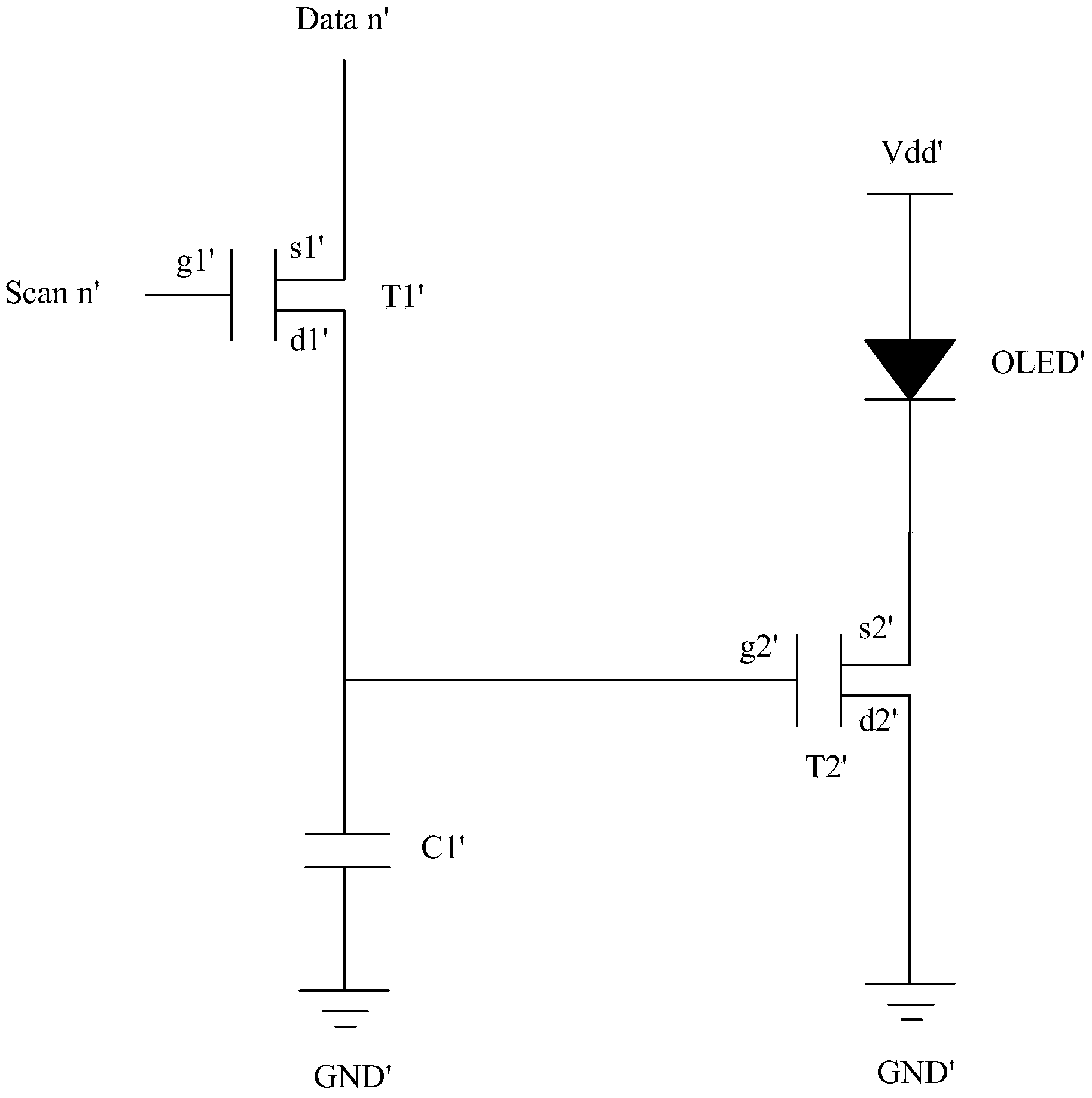

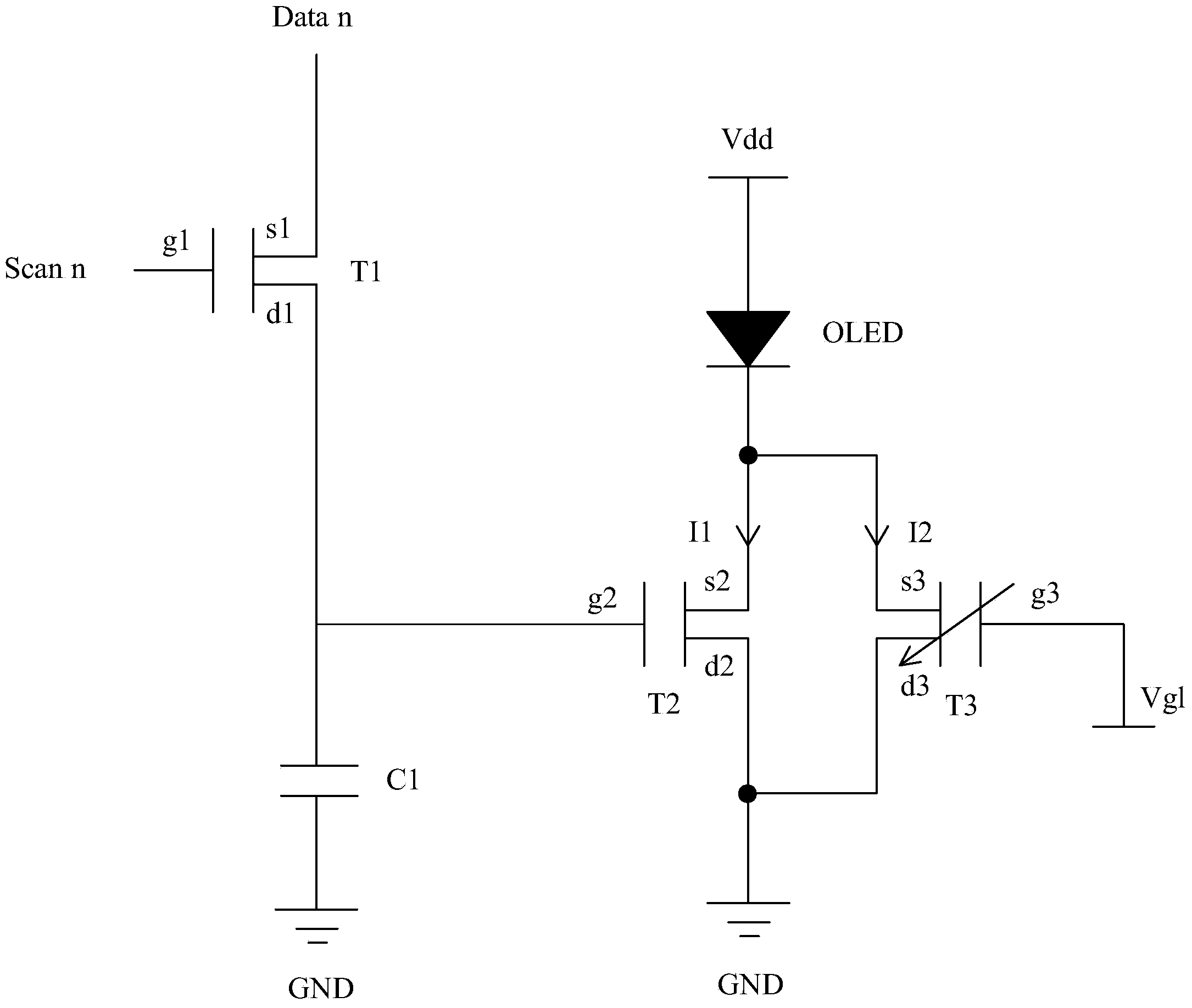

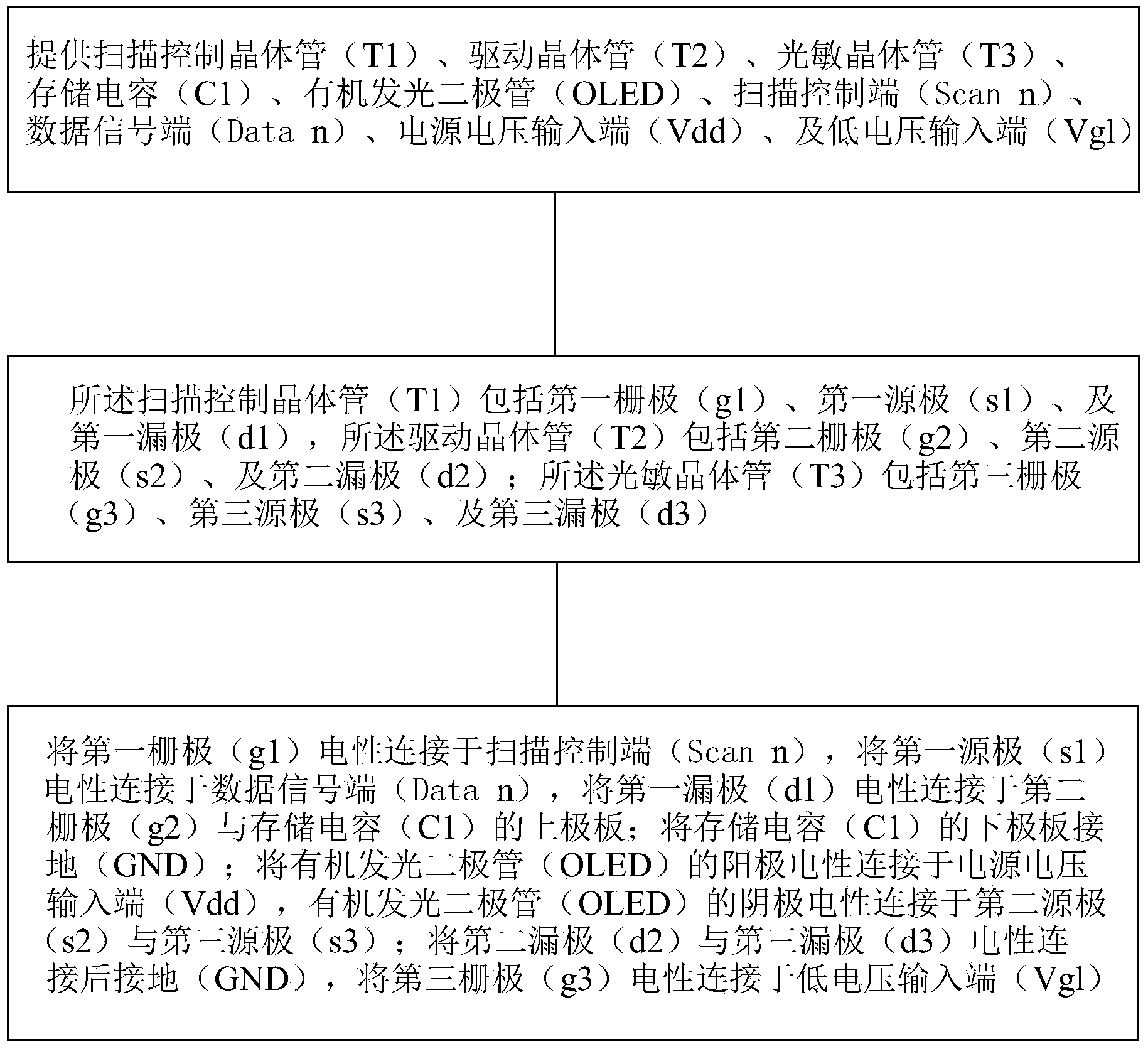

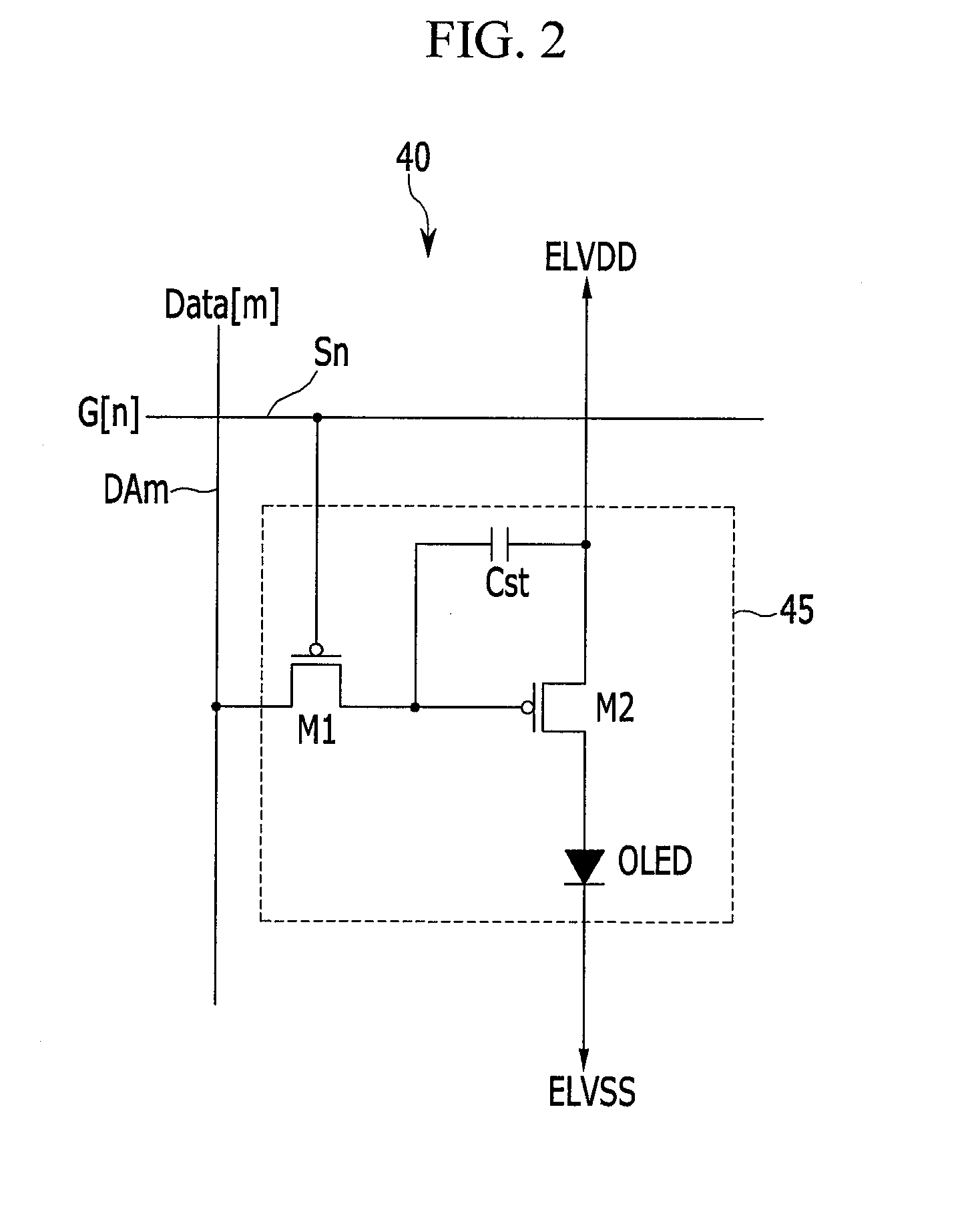

Panel drive circuit and panel drive method

ActiveCN103956142AReduce drive power consumptionExtended service lifeStatic indicating devicesCapacitanceDriving current

The invention provides a panel drive circuit and a panel drive method. The panel drive circuit comprises a scanning control transistor (T1), a drive transistor (T2), a photo-transistor (T3), a storage capacitor (C1) and an OLED. The panel drive circuit further comprises a scan control end (Scan n), a data signal end (Data n), a power voltage input end (Vdd) and a low voltage input end (Vgl). The drive currents of the drive transistor (T2) are gray-scale currents (I1), the currents of the photo-transistor (T3) are environment lighting currents (I2), the gray-scale currents (I1) depend on gray-scale voltages stored in the storage capacitor (C1), and the environment lighting currents (I2) depend on environment lighting. The luminance of a panel depends on the sum of the gray-scale currents (I1) and the environment lighting currents (I2).

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

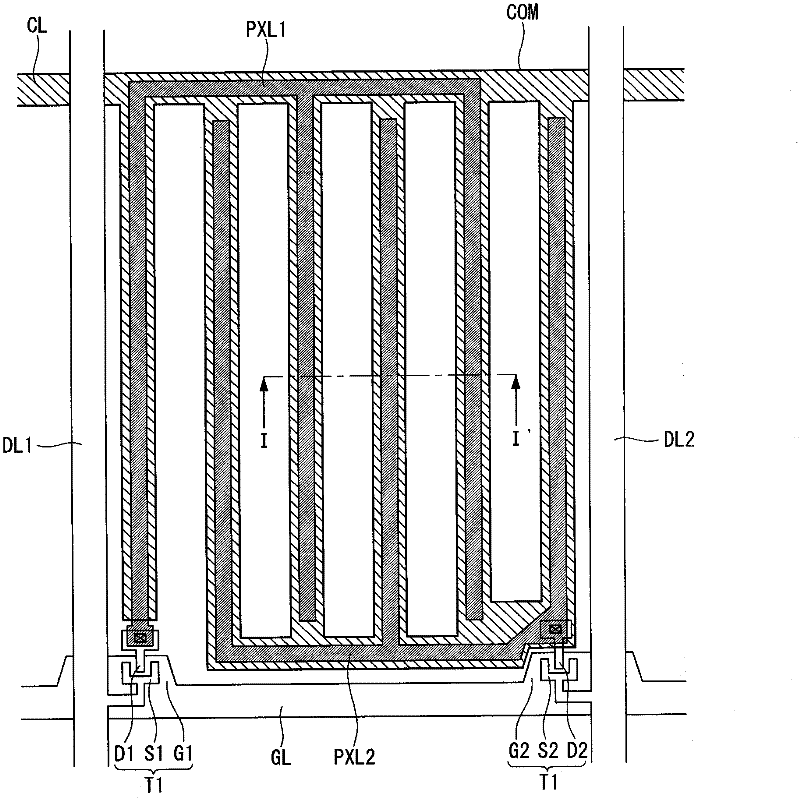

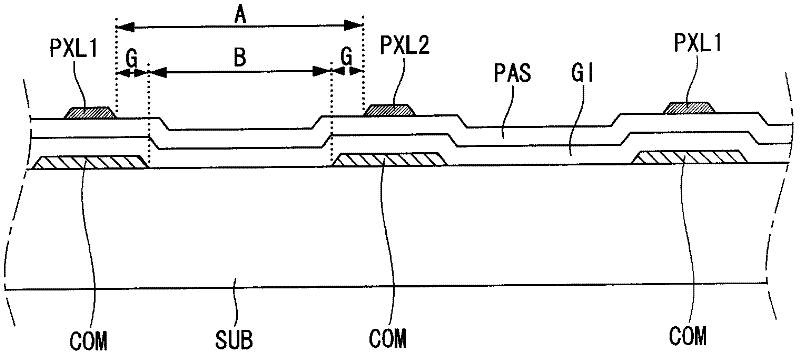

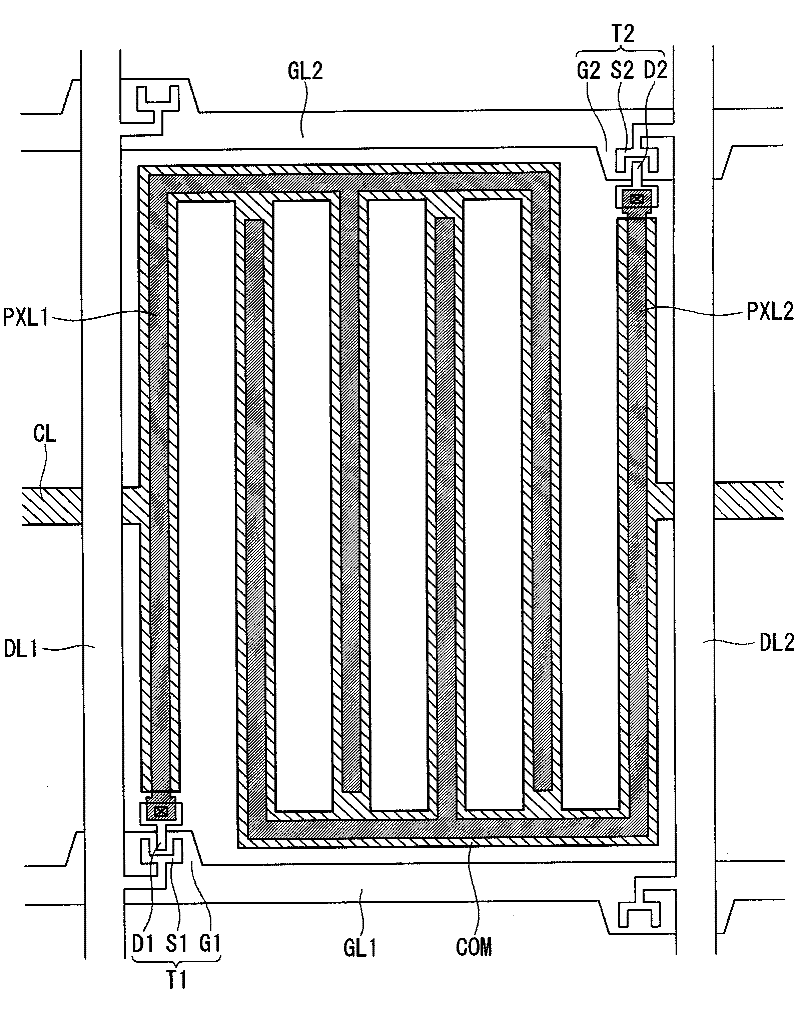

High light transmittance in-plane switching liquid crystal display device

ActiveCN102455558AReduce drive power consumptionDecreaseStatic indicating devicesNon-linear opticsIn planeElectricity

The present disclosure relates to a high light transmittance in-plane switching liquid crystal display device. The present disclosure suggests a horizontal electric field type liquid crystal display device comprising: a substrate (SUB); a plurality of gate lines (G) disposed in horizontal direction on the substrate; a plurality of data lines (DL) disposed in vertical direction on the substrate; a plurality of pixel area defined by the crossing the plurality of the gate lines and the plurality of the data lines; a first pixel electrode (PXL1) having a plurality of segments arraying with a predetermined distance within the pixel area; a second pixel electrode (PXL2) having a plurality of segments arraying in parallel with the first pixel electrode (PXL1) within the pixel area; and a common electrode (COM) overlapping with the first pixel electrode (PXL1) and the second pixel electrode (PXL2) within the pixel area.

Owner:LG DISPLAY CO LTD

Method for driving source of liquid crystal display

InactiveUS6577293B1Reduce power consumptionReduce drive power consumptionTelevision system detailsCathode-ray tube indicatorsLiquid-crystal displayElectrical polarity

There is provided a source driving method in a liquid crystal display, which applies negative and positive video signals to source lines of the liquid crystal display including a first and second plates and a liquid crystal being inserted therebetween, in which each video signal is applied, with its voltage being divided two phases of polarity modulation and gray scale decision. The polarity modulation is accomplished through stepwise charging and discharging.

Owner:SAMSUNG ELECTRONICS CO LTD

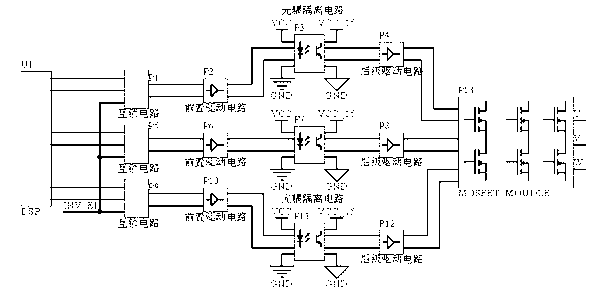

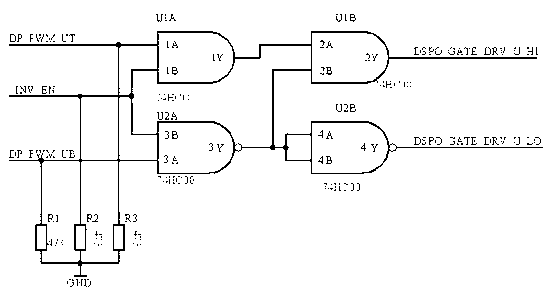

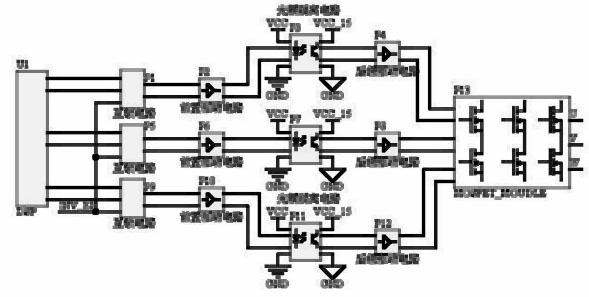

PWM (pulse-width modulation) interlocking drive circuit

InactiveCN102710116AReduce drive power consumptionSolution to short lifePower conversion systemsMOSFETField-effect transistor

The invention provides a PWM (pulse-width modulation) interlocking drive circuit which is stable and reliable, lower in drive power, long in service life and fast in switching speed and comprises a digital signal processor which can be used for generating a PWM signal, wherein the digital signal processor has N pairs of PWM signal outputs and each PWM signal is connected with each pair of upper and lower bridge arms of a MOSFET (metal-oxide-semiconductor field effect transistor) module. The digital signal processor which is fast in operational speed and has a PWM signal generator is adopted as a drive core, the duty cycle and the output frequency of the PWM can be programmed by software; and PWM pulses of the upper and lower bridge arms of the MOSFET module are controlled to adjust appropriate dead time, so that the condition that the upper and lower bridge arms of the MOSFET module are not conducted is ensured; and meanwhile, the PWM can be connected to the upper and lower bridge arms of the MOSFET module through an interlocking circuit, namely that the PWM signals are not simultaneously input to the upper and lower bridge arms of the MOSFET module from the aspect of circuit, and safety of the MOSFET module is ensured.

Owner:CHERY AUTOMOBILE CO LTD

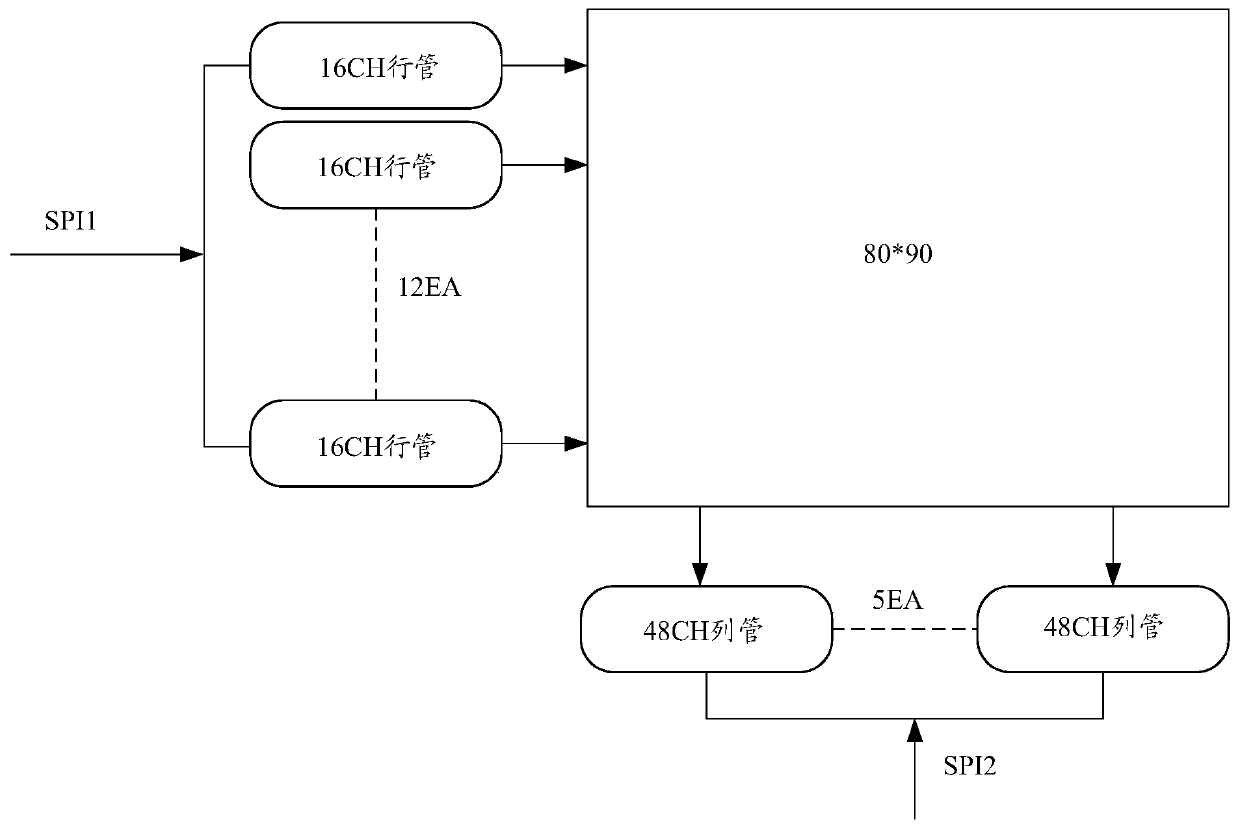

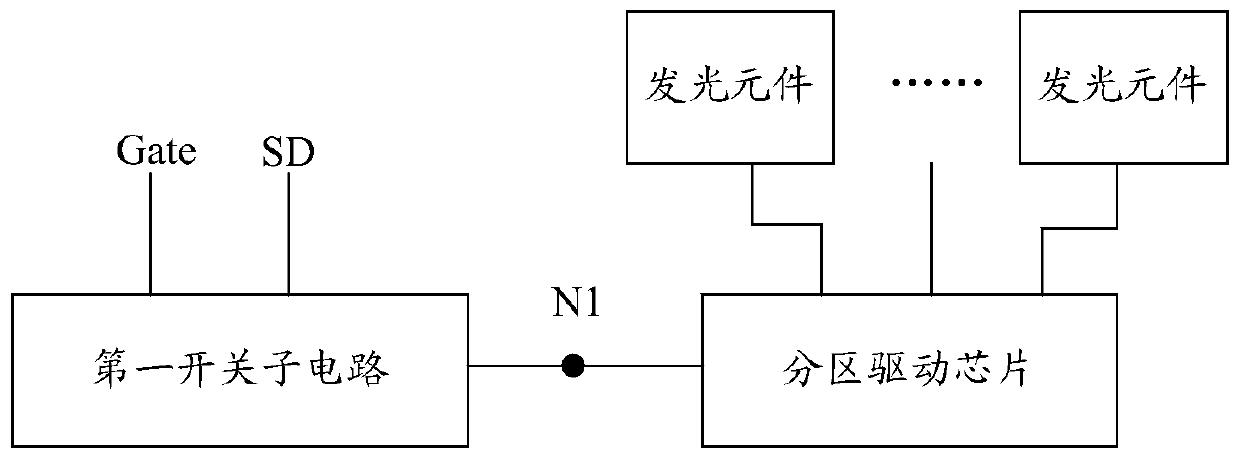

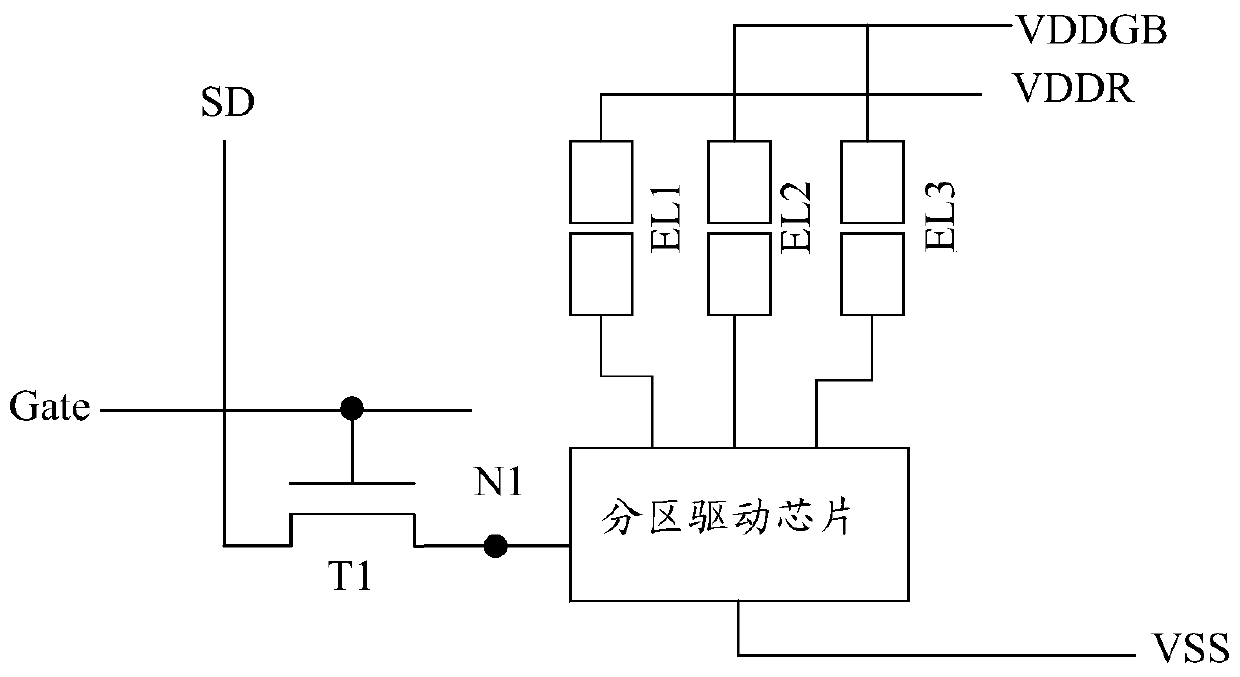

Pixel circuit, driving method thereof and display device

ActiveCN111243496AReduce the number of tracesReduce drive power consumptionStatic indicating devicesScan lineDisplay device

The invention discloses a pixel circuit, a driving method thereof and a display device. The pixel circuit comprises a first switch sub-circuit, a partition driving chip and a plurality of light-emitting elements. The first switch sub-circuit is respectively connected with a scanning line, a data line and a first node and is used for writing a data voltage signal of the data line into the first node under the control of the scanning line; and the partition driving chip is connected with the first node and the plurality of light-emitting elements respectively and is used for judging driving timecorresponding to each light-emitting element according to a data voltage signal input by the first node, and driving the light-emitting elements to emit light by using the data voltage signal withinthe corresponding driving time. Active site selection driving is realized through the first switch sub-circuit and the partition driving chip, so that the number of glass-based wires is effectively reduced, the difficulty of a side edge wire routing process is greatly reduced, the driving power consumption and the driving cost of the whole display module are reduced, and the competitive advantageof a product is greatly improved.

Owner:BOE TECH GRP CO LTD +1

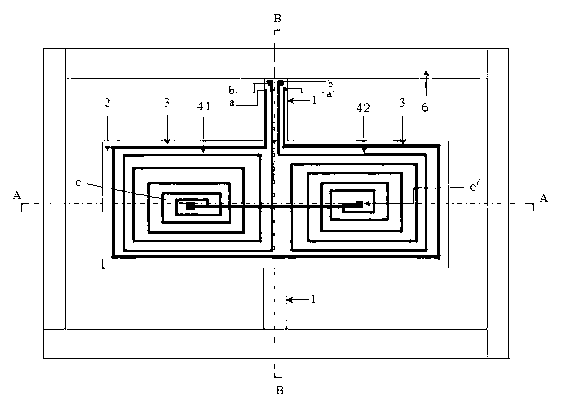

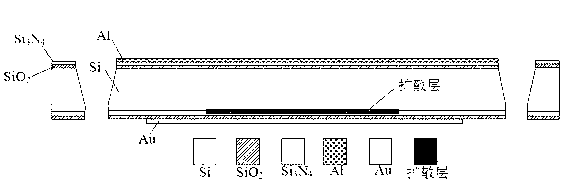

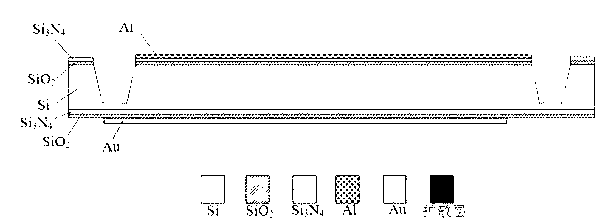

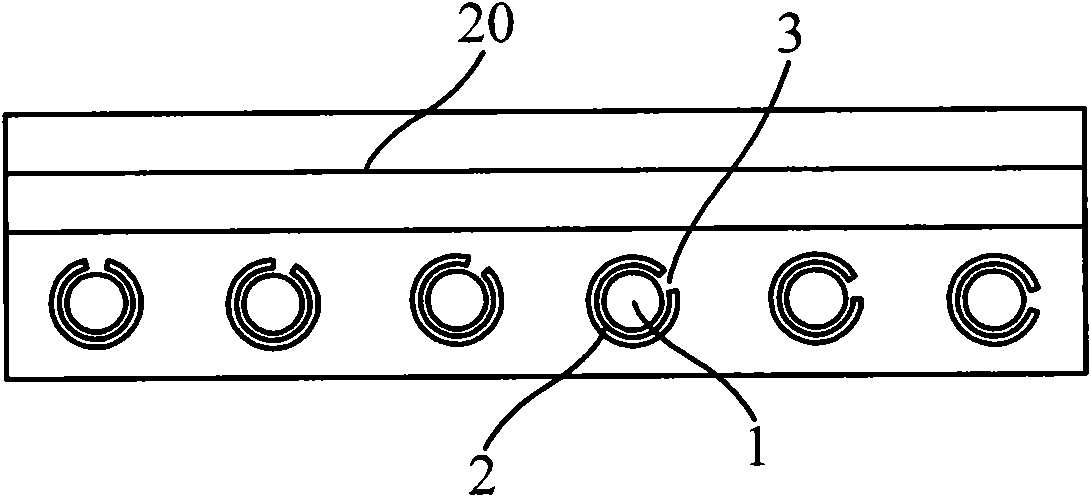

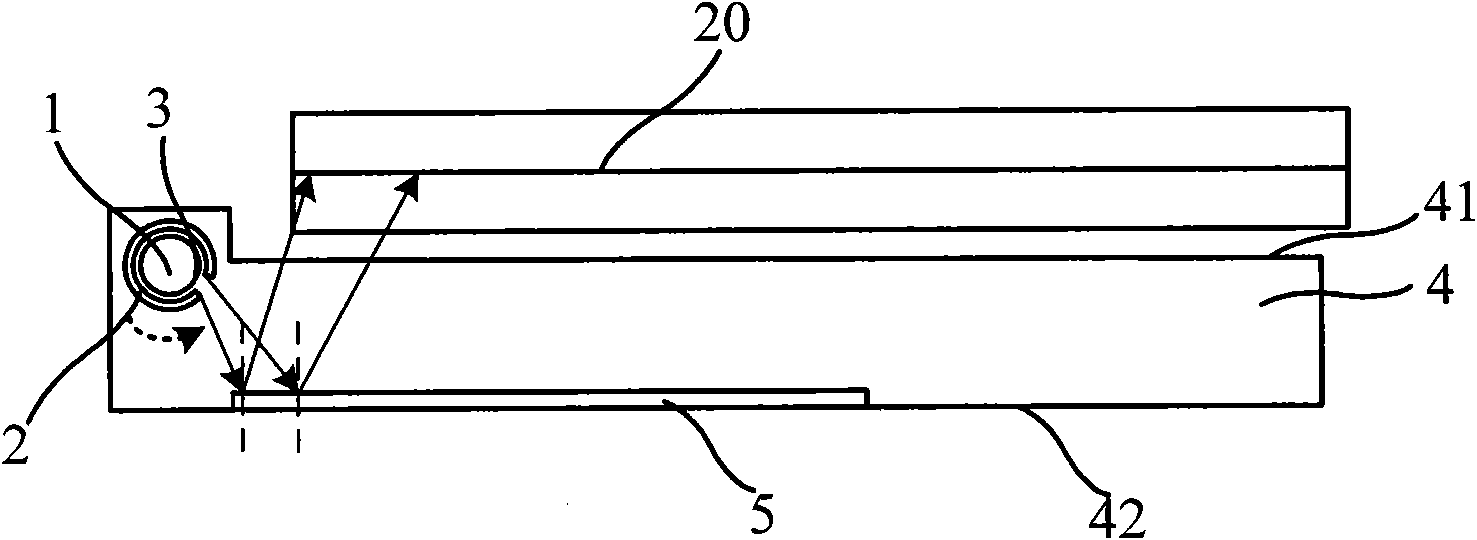

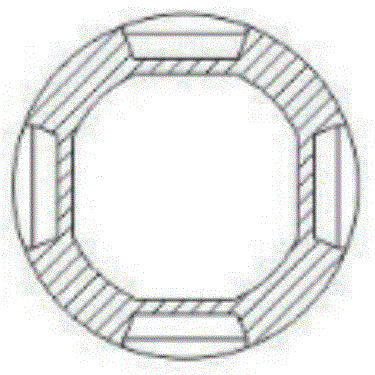

Bipolar electromagnetic scanning micro lens

InactiveCN102707435AExtend the scan rangeReduce drive power consumptionTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesSignal processing circuitsSpectrograph

The invention discloses a bipolar electromagnetic scanning micro lens which is processed by taking a silicon base material as a substrate and adopting MEMS (microelectronic mechanical system) process, and is provided with a micro reflecting mirror 2, a bipolar electromagnetic micro driver 4, a torsion beam 1, an angular transducer 3, a bipolar electromagnetic micro driver loop connection pole 5 and a supporting frame 6. According to the invention, a bipolar driving manner is adopted to drive the micro lens, so that attraction force and repulsive force are simultaneously acted on the torsion beam, and wide-angle scanning of the micro lens is realized at lower driving voltage; due to the adoption of the bipolar electromagnetic system driving structure, the response time is greatly shortened and the working frequency of the micro lens is greatly improved; and at the same time, the electromagnetic angular transducer is integrated, so that the accurate measurement of the scanning angle is realized. Therefore, the peripheral signal processing circuit of the scanning micro lens is simple and feasible, and the results of the scanning micro lens can be widely applied to the fields of medical imaging, projector spectrograph, graphic code reader and the like.

Owner:CHONGQING UNIV

Back light module, driving method thereof and liquid crystal display

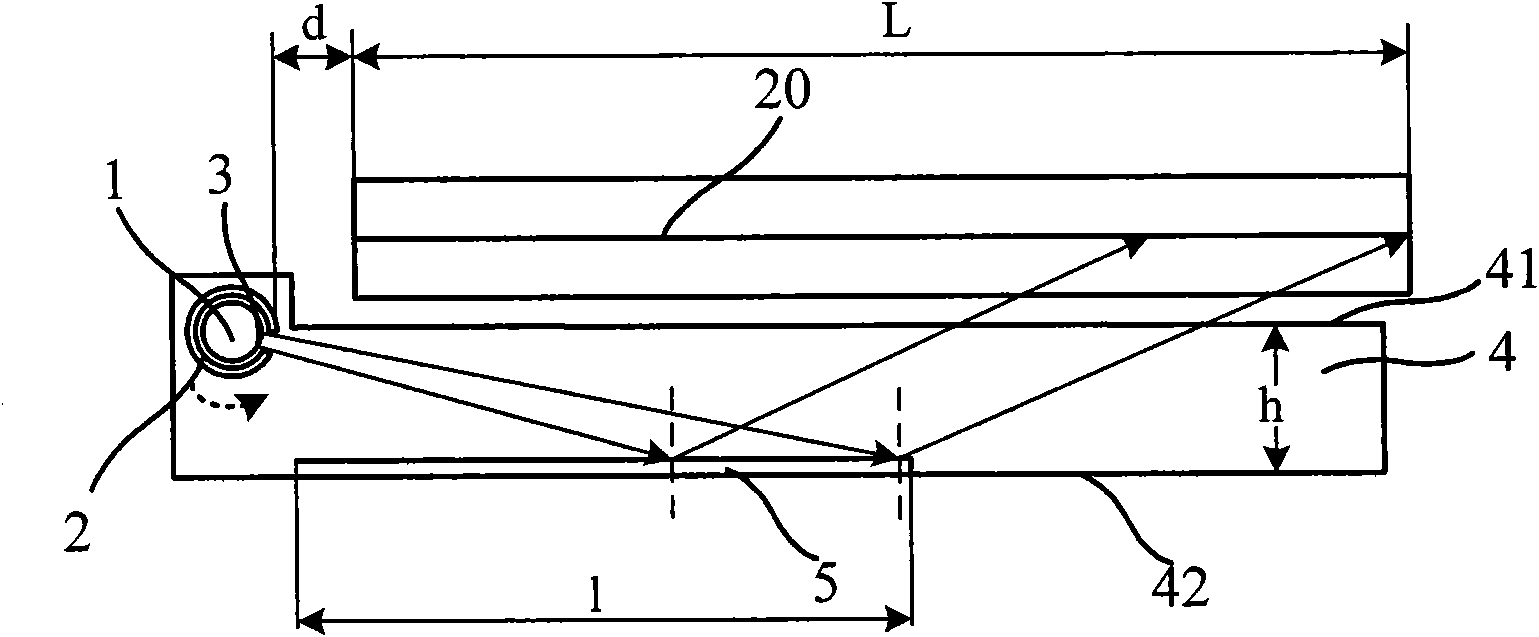

InactiveCN101852362AReduce thicknessReduce in quantityStatic indicating devicesNon-linear opticsLiquid-crystal displayGrating

The invention relates to a back light module, a driving method thereof and a liquid crystal display. The back light module comprises a light guide chamber, a back light source, a grating cover and a reflection mirror, wherein the light guide chamber comprises a back plate; the back light source is arranged at the side of the light guide chamber; the grating cover covers outside the back light source, at least one grating seam for transmitting light beams emitted by the back light source to form scanning light beams is arranged on the grating cover, and the grating cover rotates around the back light source so that the scanning light beams movably irradiates on the back plate of the light guide chamber; and the reflection mirror is arranged on the back plate of the light guide chamber and used for reflecting the movably-irradiated scanning light beams out of the light guide chamber. The method comprises the steps of: driving the back light source to lighten, and forming the scanning light beams through the transmission of the light beams out of the grating seam on the grating cover; driving the grating cover to rotate according to the set frequency, movably irradiating on the back plate by the scanning light beams, and reflecting the scanning light beams out of the light guide chamber by the reflection mirror. The technical scheme can reduce the thickness of the liquid crystal display, reduce the energy consumption for driving, and save the cost.

Owner:BOE TECH GRP CO LTD +1

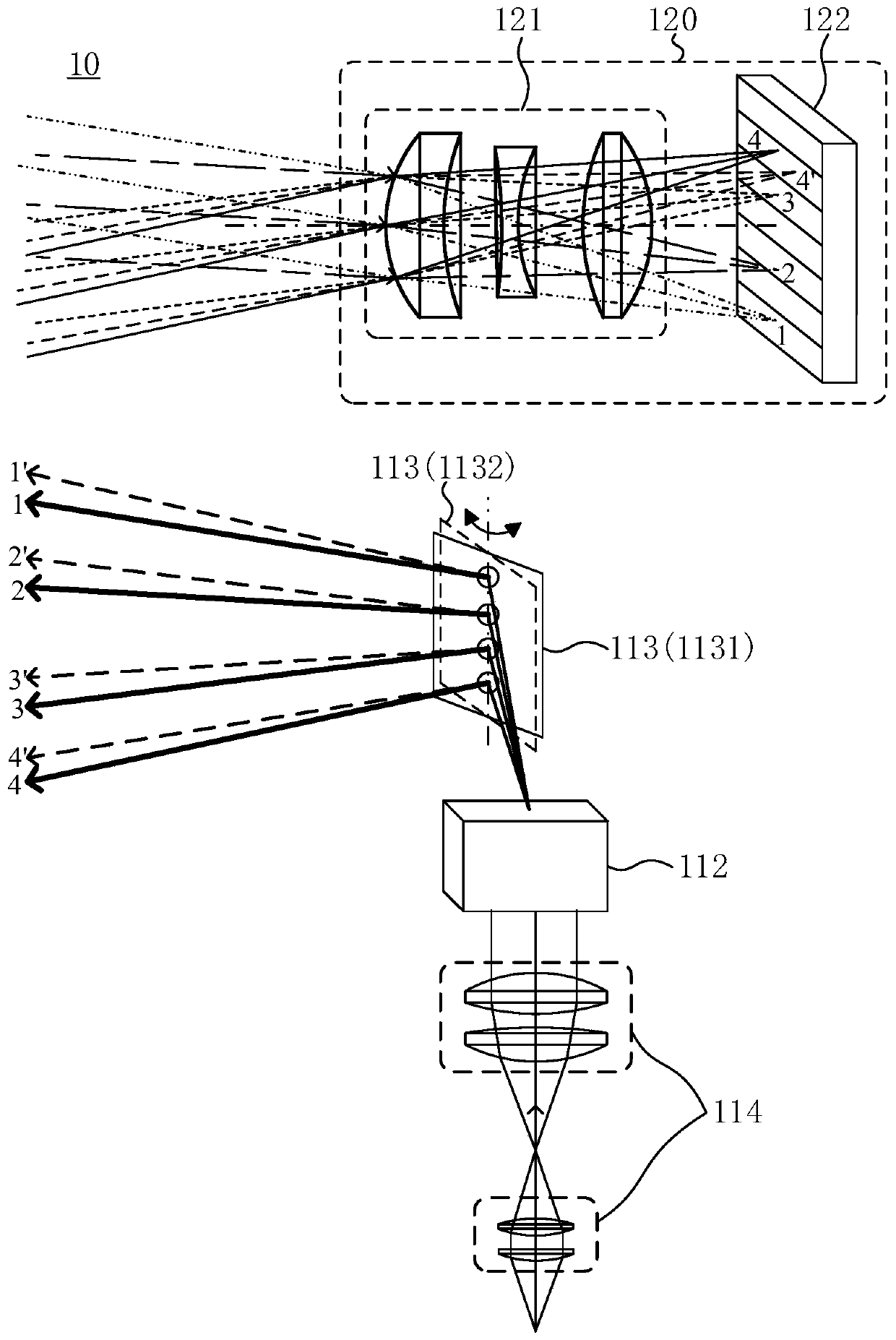

Laser radar

PendingCN109782256AReduce drive power consumptionReduce feverElectromagnetic wave reradiationRadarLight beam

The invention discloses a laser radar comprising a light emitting unit, a light receiving unit and a control processing unit. The light emitting unit comprises a light source subunit, an optical phased array subunit and a MEMS scanning mirror subunit that are arranged successively in a light propagation direction; and the light source subunit, the optical phased array subunit and the MEMS scanningmirror subunit are connected with the control processing unit electrically. The light source subunit emits an incident beam; the optical phased array subunit deflects the incident beam in the first plane to form a one-dimensional beam having a predetermined scan angle on the first plane; the one-dimensional beam is irradiated onto the reflective surface of the MEMS scanning mirror subunit; the MEMS scanning mirror subunit is rotated by the driving force to deflect the one-dimensional beam irradiated onto the reflective surface in a second plane intersected with the first plane, thereby realizing scanning of the one-dimensional beam on the second plane and forming a detection beam. Therefore, the e mechanical losses are reduced and the service life of the laser radar is prolonged.

Owner:LEISHEN INTELLIGENT SYST CO LTD

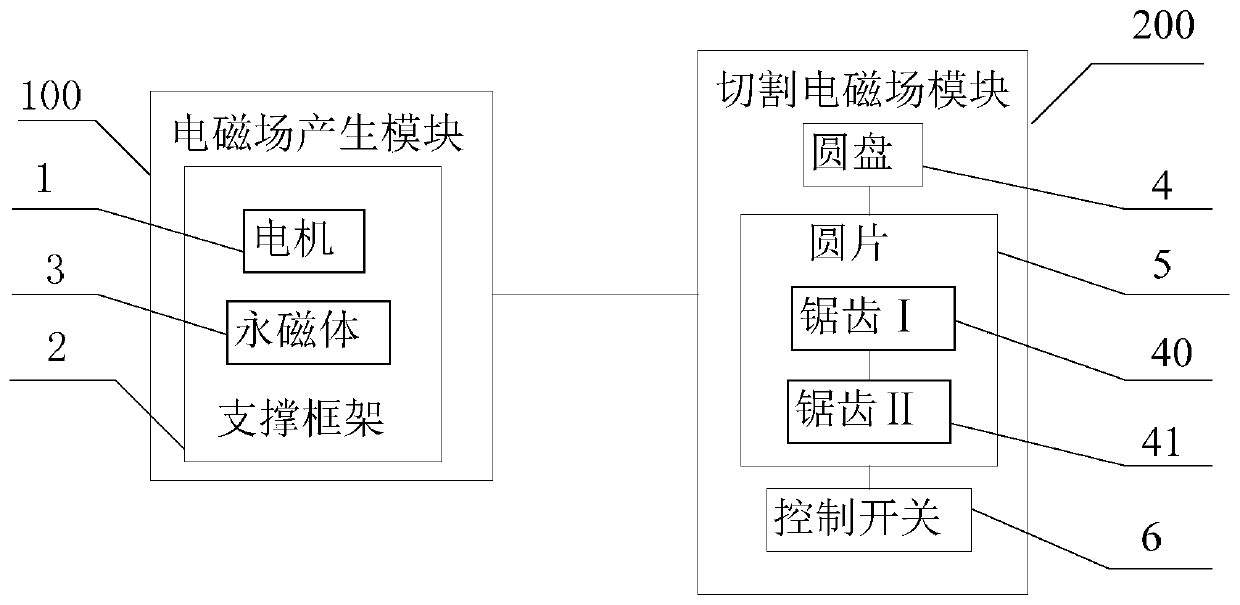

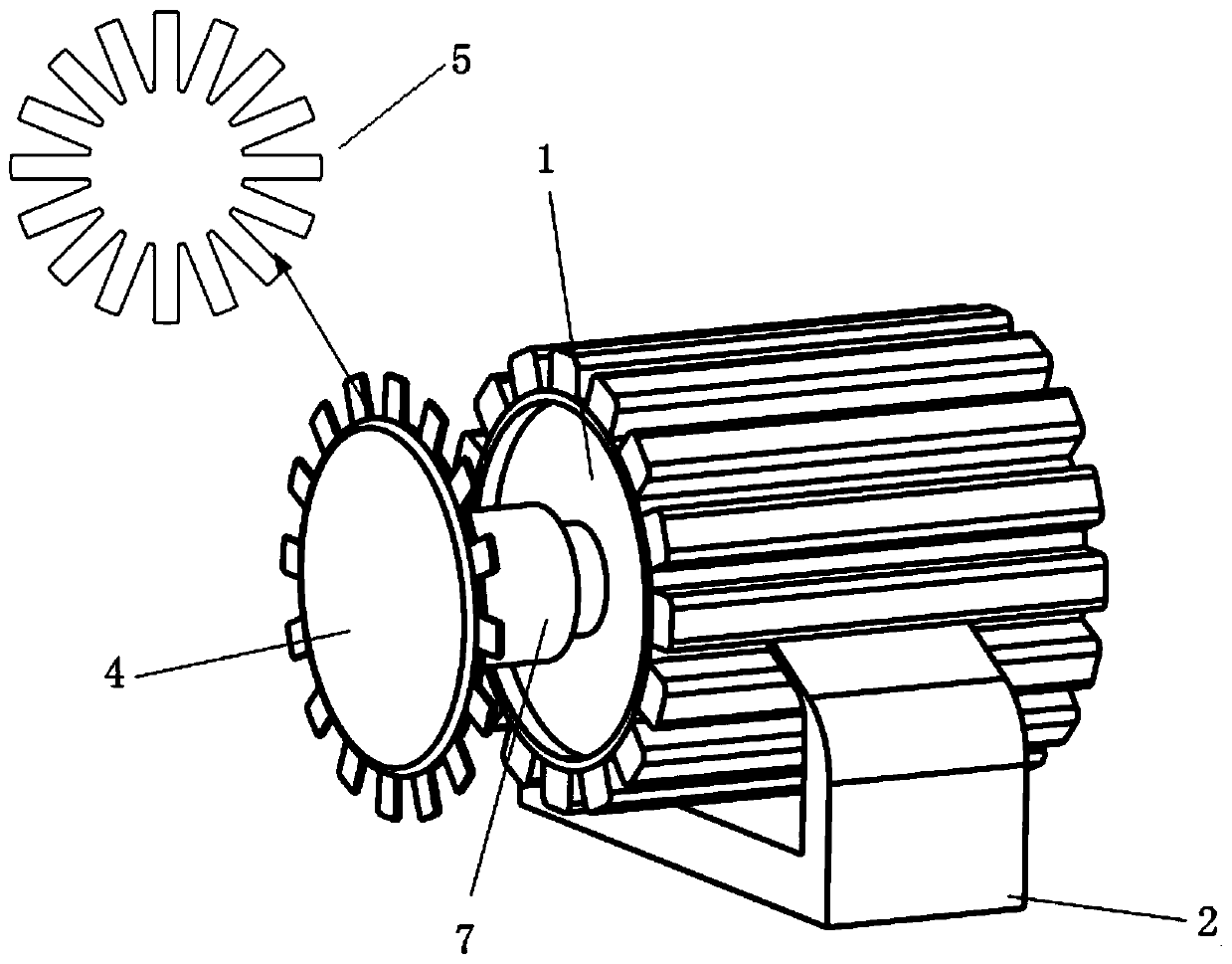

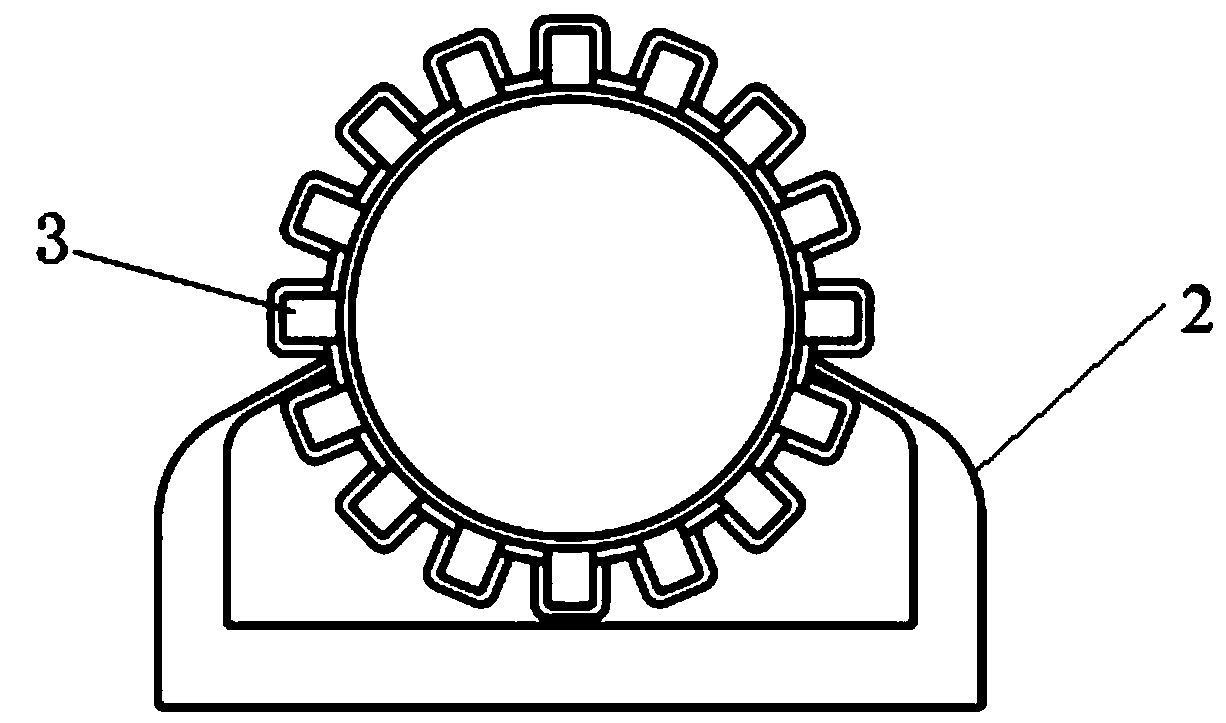

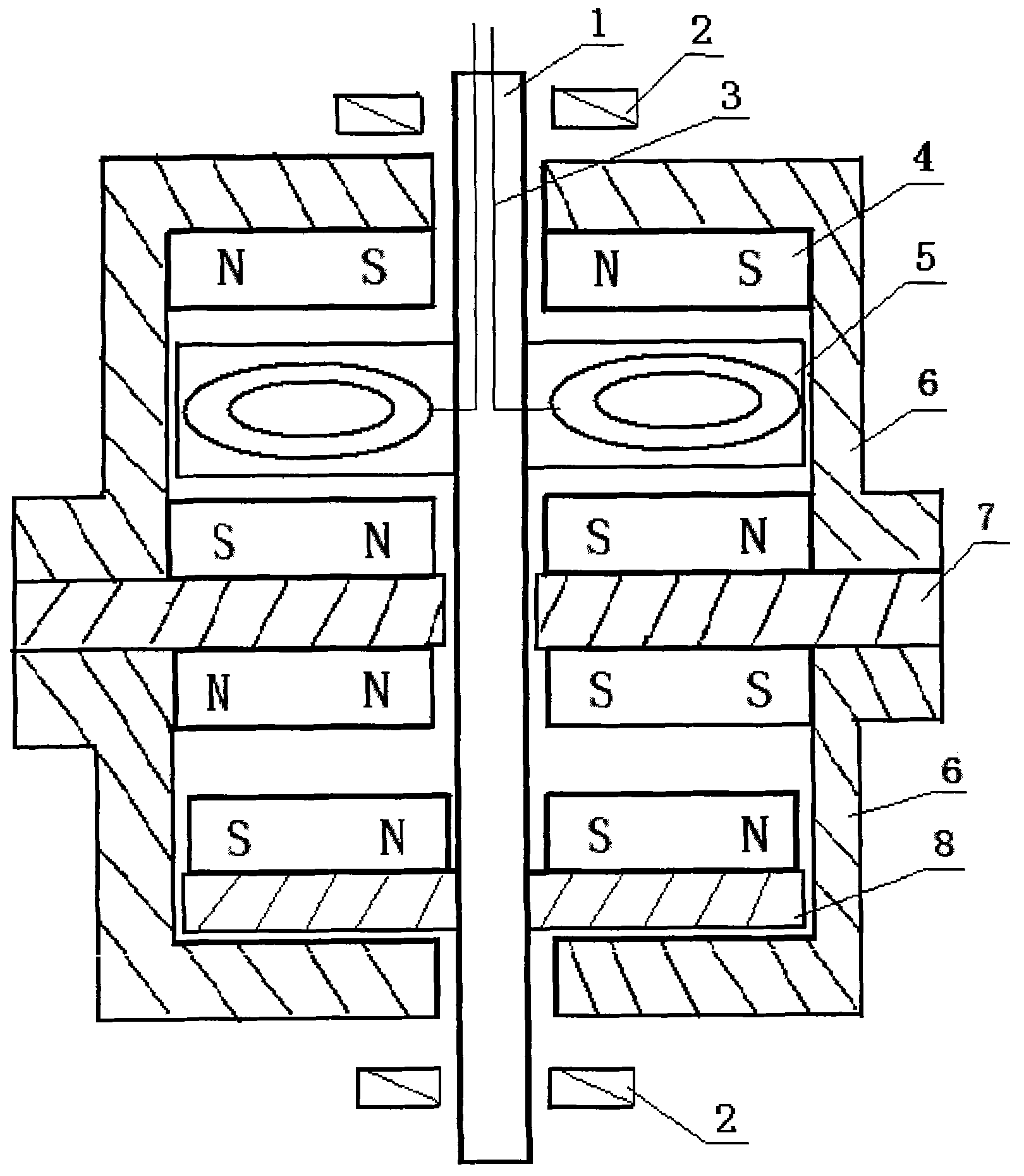

Frequency-adjustable ultralow-frequency mechanical antenna structure

ActiveCN111585018ALight in massEasy to processSimultaneous aerial operationsRadiating elements structural formsElectric machineControl switch

The invention discloses a frequency-adjustable ultra-low frequency mechanical antenna structure and belongs to the technical field of ultra-low frequency communication. The antenna structure comprisesa static magnetic field generation module for generating a static magnetic field and a static magnetic field cutting module for cutting the static magnetic field generation module to generate an electromagnetic field changing with time, and the static magnetic field generation module comprises a motor, a plurality of permanent magnets and a supporting frame for fixing the rotating motor and the plurality of permanent magnets; the supporting frame is arranged outside the motor; the plurality of permanent magnets are uniformly arranged on the outer surface of the supporting frame; the static magnetic field cutting module comprises a disc, a wafer with sawteeth and a control switch for controlling the sawtooth length change of the wafer and driving the wafer to move; the number of teeth of the sawtooth wafer is the ratio of the time-varying magnetic field frequency to the working frequency of the rotating motor, and by changing the mechanical motion mode, the frequency of electromagneticwaves generated by a mechanical antenna is improved while the weakening of the magnetic induction intensity is reduced as much as possible, so that the requirement for the frequency in the transmission process is met.

Owner:DALIAN JIAOTONG UNIVERSITY

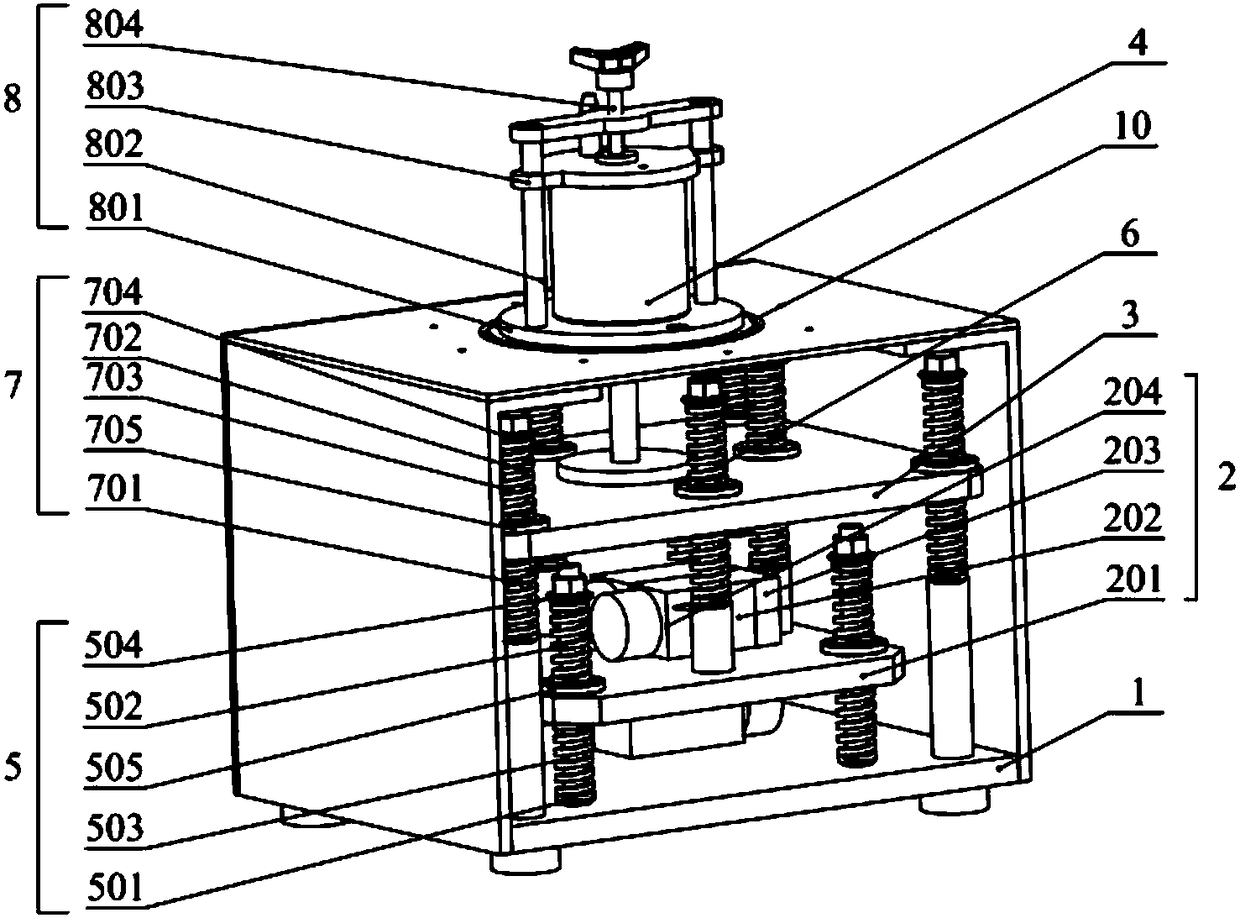

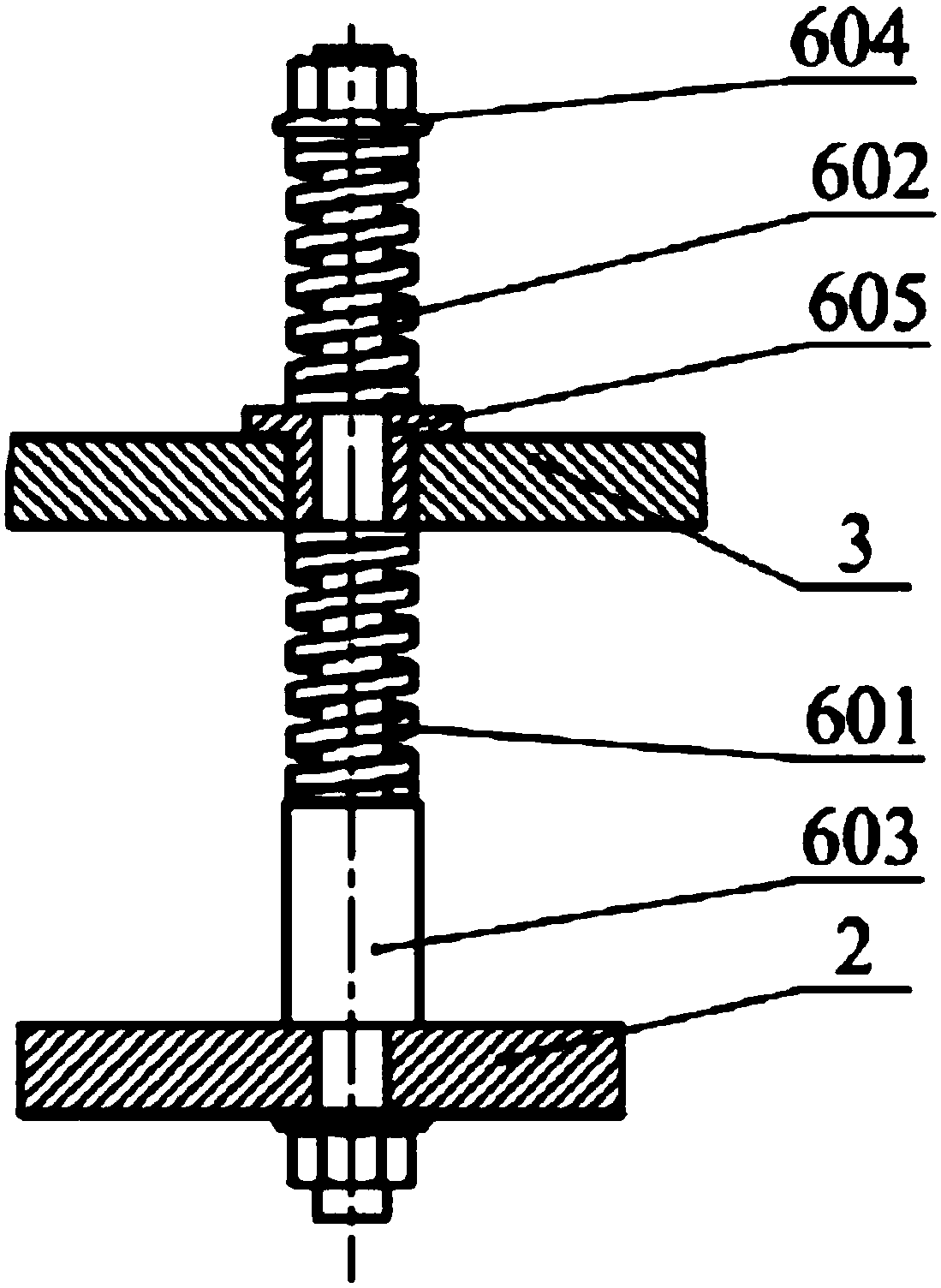

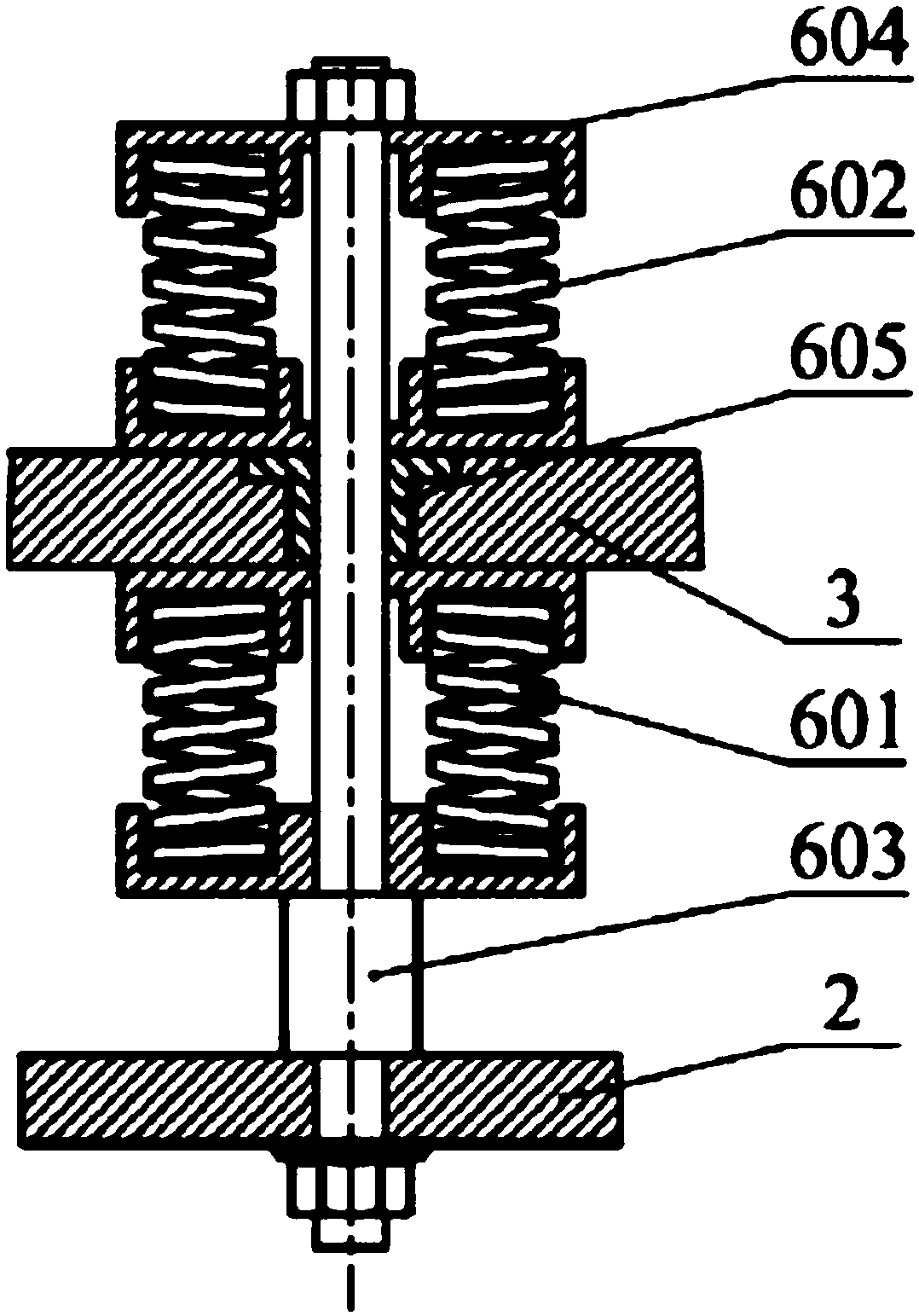

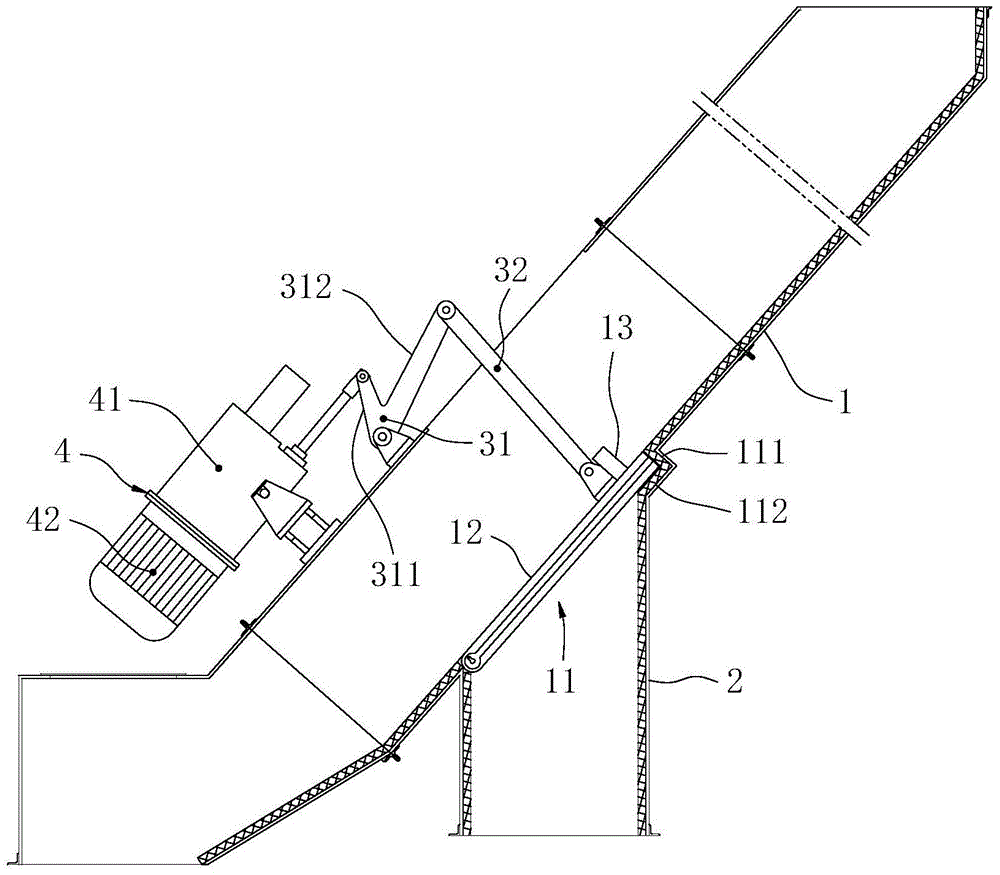

Dual-plastid acoustic-resonance mixing device suitable for compound energetic material

PendingCN108393020AReduce forceReduce noise pollutionShaking/oscillating/vibrating mixersTransportation and packagingEngineeringAcoustic resonance

The invention belongs to the technical field of multiphase flow mixing correlation and discloses a dual-plastid acoustic-resonance mixing device suitable for a compound energetic material. The dual-plastid acoustic-resonance mixing device comprises an installation platform, shock excitation plastid, load plastid, a first elastic support, a second elastic support and a third elastic support, wherein the installation platform comprises a bottom plate and a top plate which are oppositely arranged, the fist elastic support is connected with the shock excitation plastid and the bottom plate, the second elastic support is connected with the load plastid and the shock excitation plastid, the third elastic support is connected with the load plastid and the bottom plate. The dual-plastid acoustic-resonance mixing device disclosed by the invention can effectively reduce driving power consumption, reduce acting force on foundation and improve stability and safety.

Owner:HUAZHONG UNIV OF SCI & TECH +1

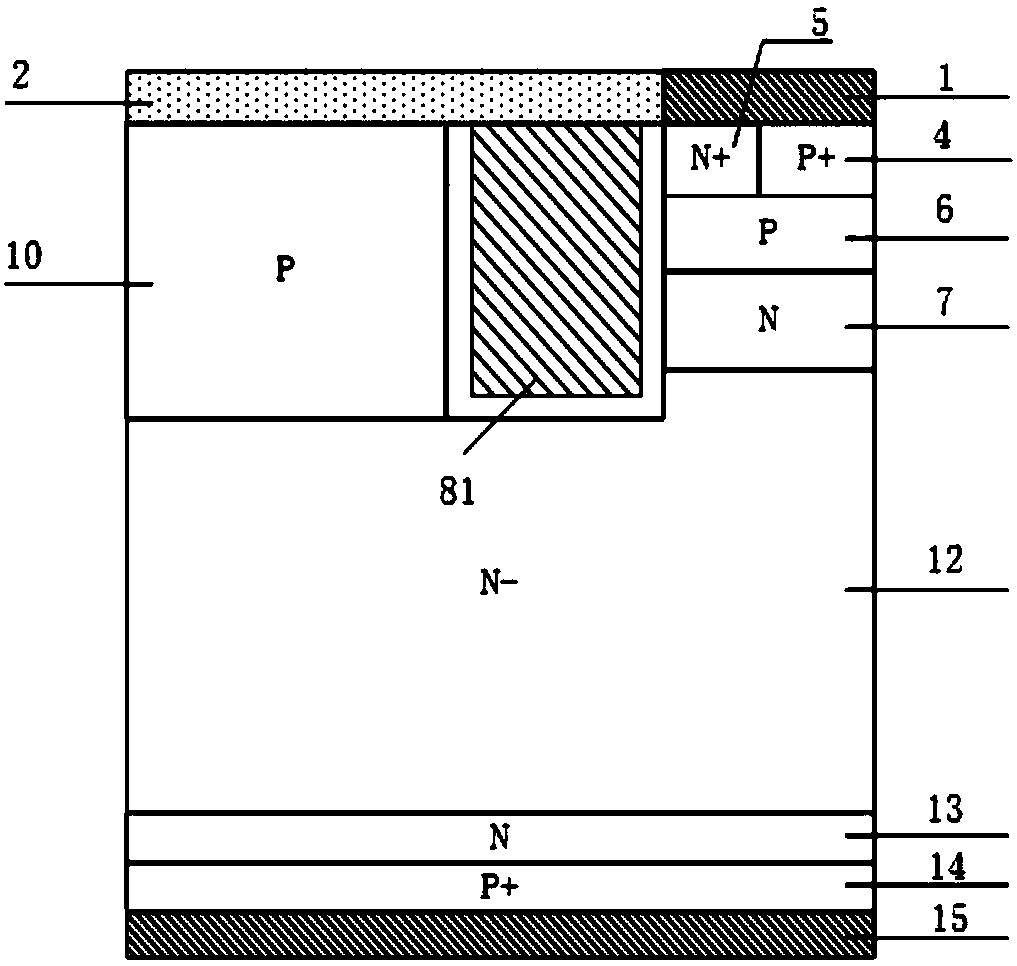

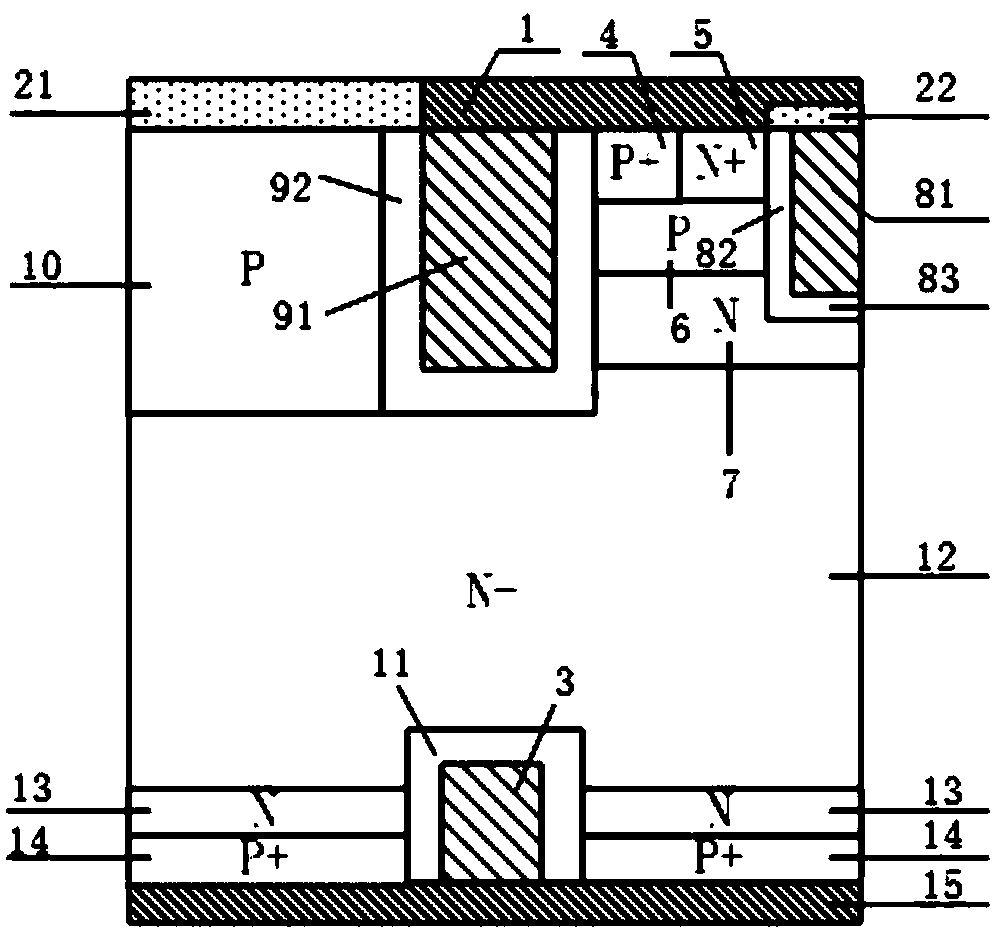

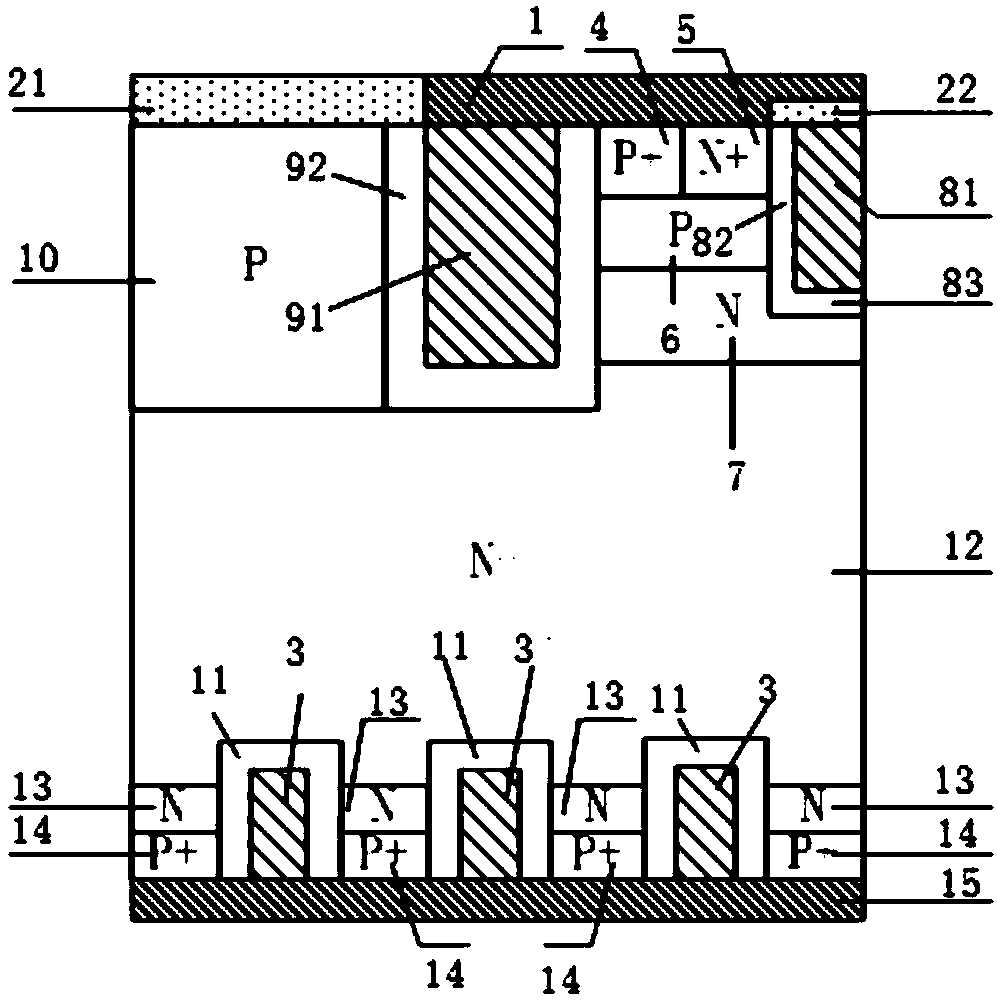

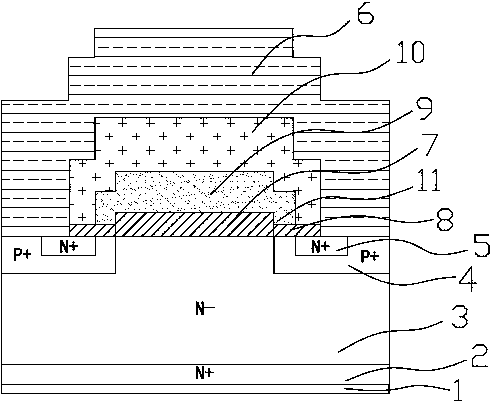

Reverse blocking type IGBT and manufacturing method therefor

InactiveCN107799588AImprove reverse breakdown voltageFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention discloses a reverse blocking type IGBT and a manufacturing method therefor, and belongs to the technical field of a semiconductor power device. By introducing trench emitter and trench collector structures, the reverse breakdown voltage of a device is improved without influencing the threshold voltage and switch-on of an IGBT device; the overall gate capacitance is lowered, the switching speed of the device is improved, the switching loss and driving power consumption of the device are lowered, and the compromising relation between forward switch-on voltage drop and switch-off loss of the conventional CSTBT structure is improved; the problems of current, voltage oscillation and EMI in the device starting dynamic process can be avoided, and device reliability is improved; theelectric field concentration effect at the bottom of the trench is improved, the forward breakdown voltage of the device is improved, and reliability of the device is further improved; and the currentcarrier enhancement effect at the emitter end of the device is further improved, the current carrier concentration distribution in a drift region can be improved, and compromising between forward switch-on voltage drop and switch-off loss can be further improved. The manufacturing method disclosed in the invention is compatible with the existing manufacturing process of a CSTBT device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

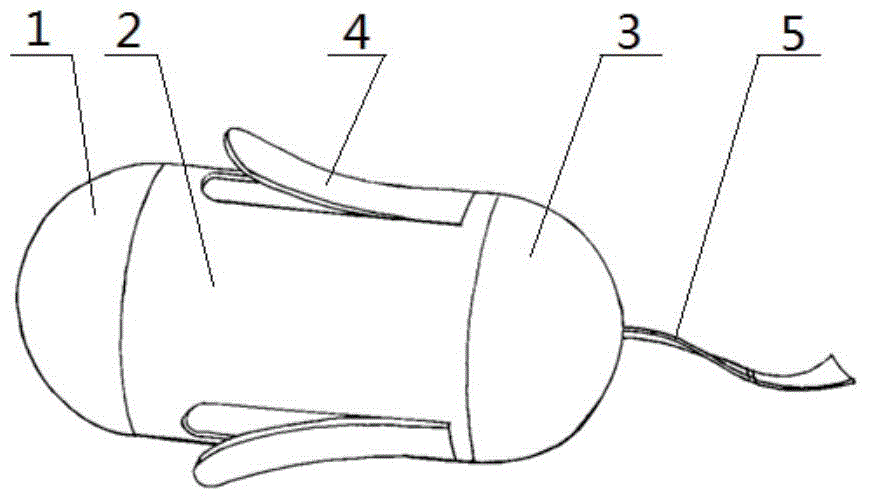

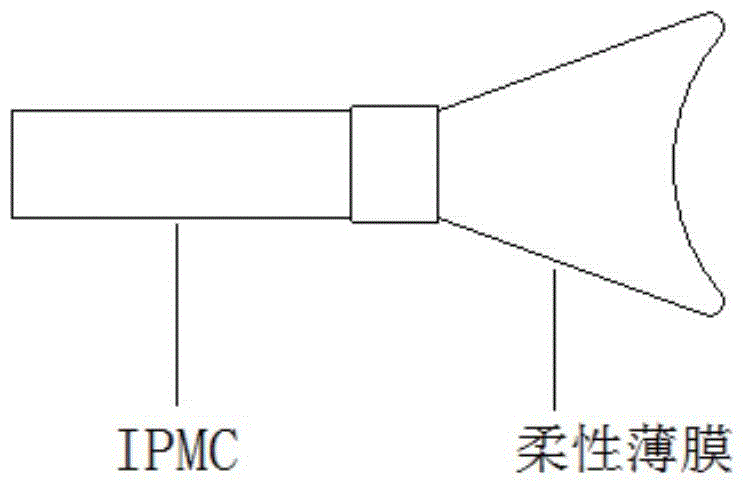

Capsule endoscope based on IPMC (ionic polymer metal composite) driving and driving method thereof

InactiveCN104873166ATo achieve the purpose of losslessEasy to swallowGastroscopesOesophagoscopesIonic polymer–metal compositesAttitude control

The invention relates to a capsule endoscope based on IPMC (ionic polymer metal composite) driving and a driving method thereof. The capsule endoscope based on the IPMC driving comprises a capsule front cover, a capsule main body structure and a capsule tail structure, wherein a plurality of slice IPMCs are arranged on the outer side of the capsule main body structure and on the capsule tail structure along the axial direction of a capsule. Under normal moving status of the capsule endoscope based on the IPMC driving, the slice IPMCs on the outer side of the capsule main body structure can be folded along the capsule, and are unfolded outwards after control signals are applied onto the slice IPMCs on the outer side of the capsule main body structure, and thereby can be used to achieve a deceleration or clamping function. When the slice IPMCs on the outer side of the capsule main body structure are respectively controlled, a posture adjustment for the capsule can be achieved. One or two IPMCs can be installed at the tail end of the capsule, and are used to achieve an active driving function. The capsule endoscope based on the IPMC driving and the driving method thereof use IPMC artificial muscle smart materials good in biocompatibility to achieve movement and posture control of the capsule endoscope based on the IPMC driving in a human body.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Display panel, driving method thereof and display device

ActiveCN110070821AReduce power lossReduce drive power consumptionStatic indicating devicesDigital storageParasitic capacitorCapacitance

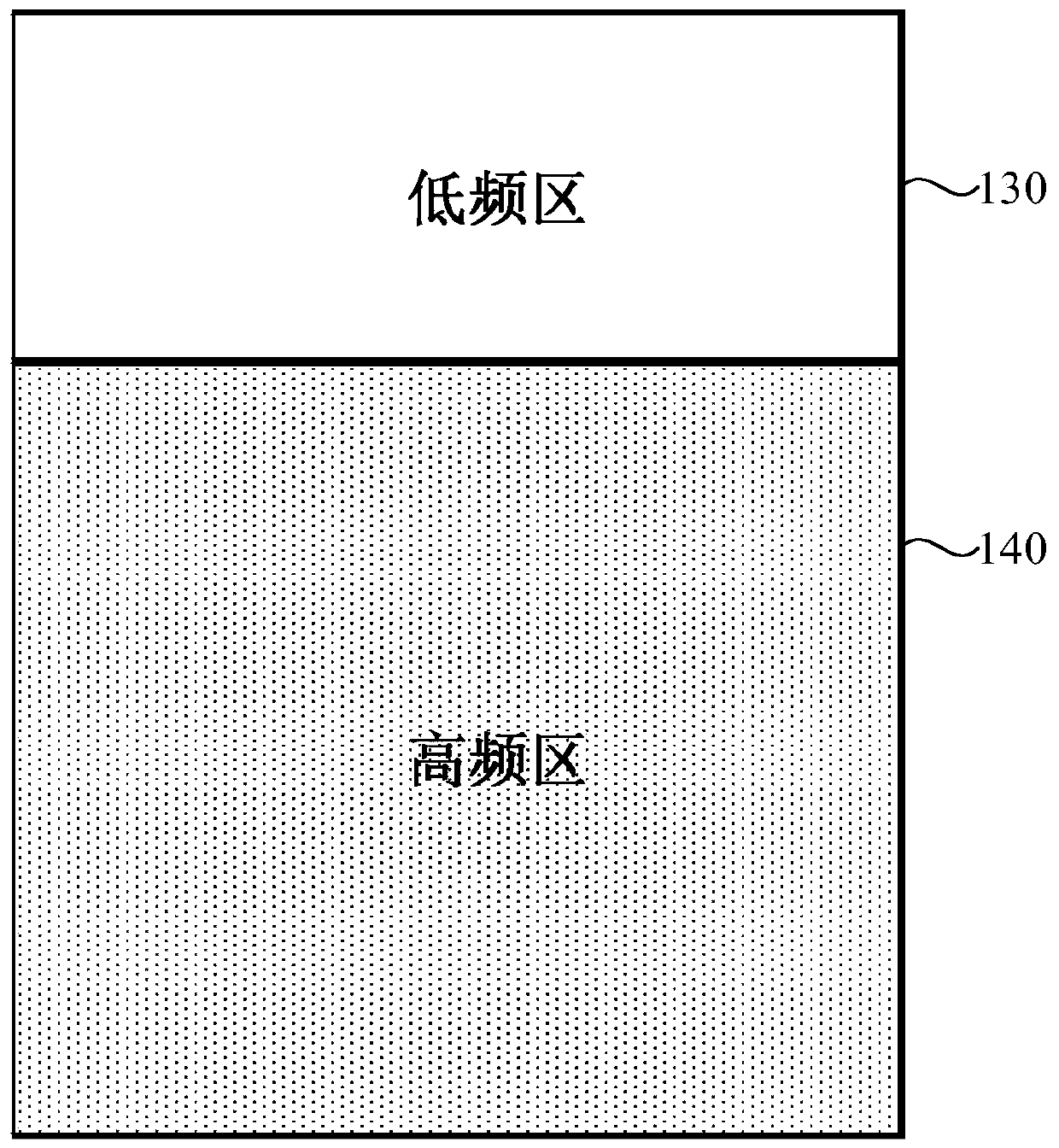

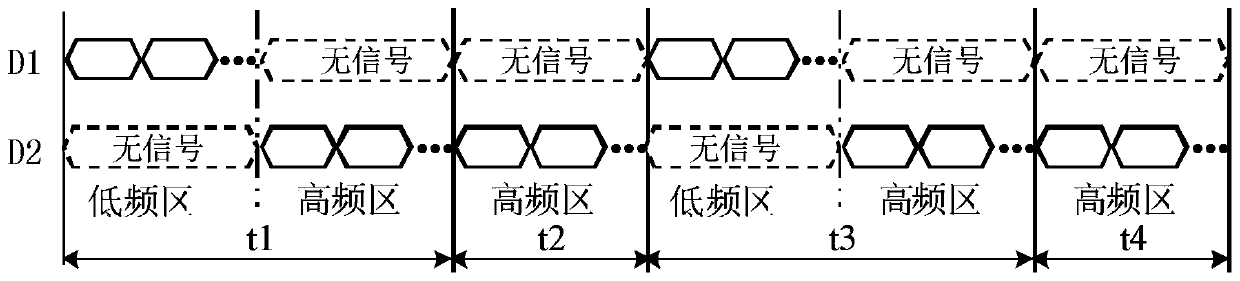

The embodiment of the invention discloses a display panel, a driving method thereof and a display device. A display area of the display panel comprises a sub-pixel array and a plurality of data lines.The sub-pixel array is divided into at least two sub-pixel areas. In the same column of sub-pixels of the sub-pixel array, the sub-pixels located in different sub-pixel areas are electrically connected with different data lines, and the sub-pixels located in the same sub-pixel area are electrically connected with at least one data line. The scanning frequencies of scanning units with sub-pixel behaviors corresponding to the at least two sub-pixel areas are different. Therefore, different sub-pixel areas can be scanned at different scanning frequencies. In one frame, data voltage can be written into the storage capacitor in the pixel circuit in the sub-pixel area with higher scanning frequency. Therefore, the charging and discharging frequency of the parasitic capacitor between the data line electrically connected with the sub-pixel in the sub-pixel area with lower scanning frequency and other film layers is lower, and the electric quantity loss caused by frequent charging and discharging of the parasitic capacitor between the data line and other film layers is reduced.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Array substrate wiring structure, liquid crystal display panel and liquid crystal display

ActiveCN106125433AImprove qualityReduce polarity switching frequencyStatic indicating devicesNon-linear opticsLiquid-crystal displayElectrical polarity

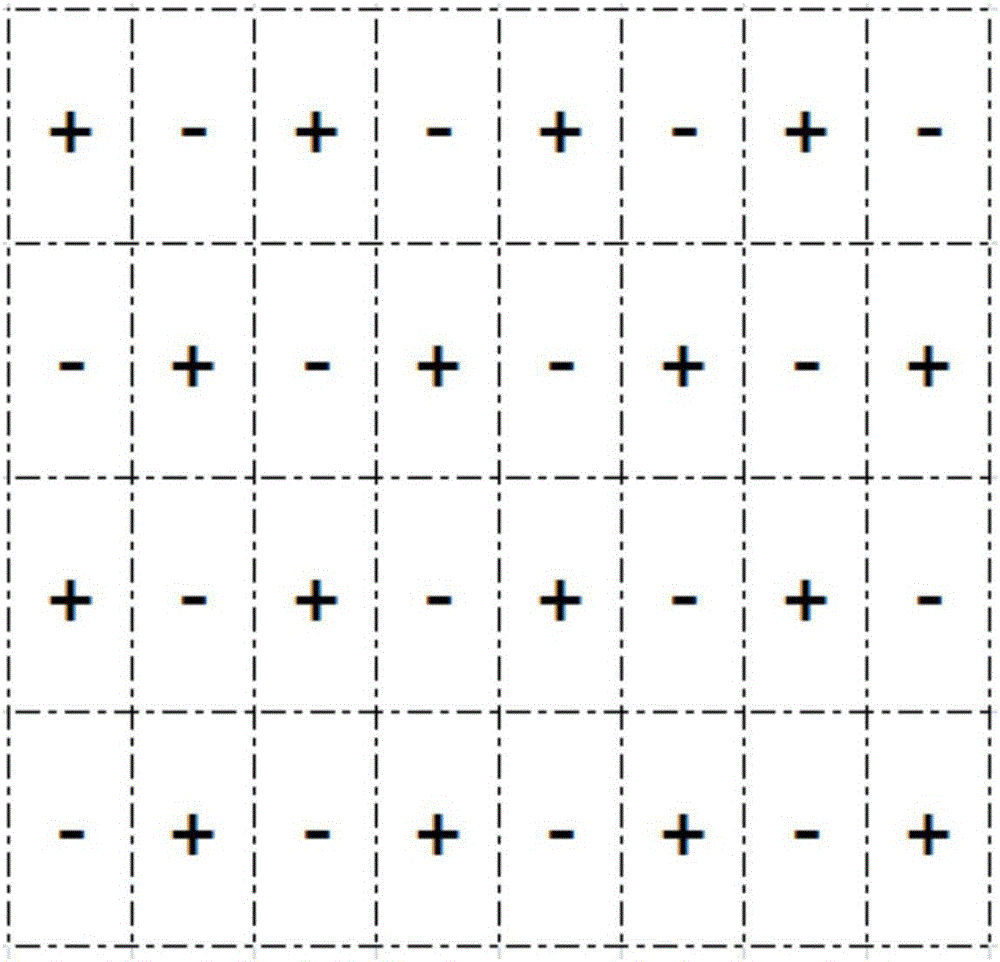

The invention provides an array substrate wiring structure. The wiring structure comprises a plurality of wiring units, each wiring unit comprises a first data line, a second data line, a third data line, a fourth data line, a fifth data line, a sixth data line, a seventh data line, an eighth data line, a first gate line, a second gate line, a third gate line, a fourth gate line, a fifth gate line and a thin film transistor matrix; the first data line, the fourth data line, the sixth data line and the seventh data line are taken as first data lines, the second data line, the third data line, the fifth data line and the eighth data line are taken as second data lines, the polarity of the first data lines is opposite to that of the second data lines, the first data lines are connected with source electrodes of thin film transistors in odd-numbered rows and odd-numbered columns and thin film transistors in even-numbered rows and even-numbered columns in a corresponding array, and the second data lines are connected with source electrodes of thin film transistors in odd-numbered rows and even-numbered columns and thin film transistors in even-numbered rows and odd-numbered columns in a corresponding array; the second gate line and the fourth gate line are connected with gate electrodes of two thin film transistors which are located in two adjacent rows of the first data line side, and the first gate line, the third gate line and the fifth gate line are connected with gate electrodes of two thin film transistors which are located in two adjacent rows of the second data line side, so that the polarity of each pixel in the pixel matrix corresponding to the thin film transistor matrix is opposite to that of any adjacent pixels.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Array substrate, display panel and driving method thereof and display device

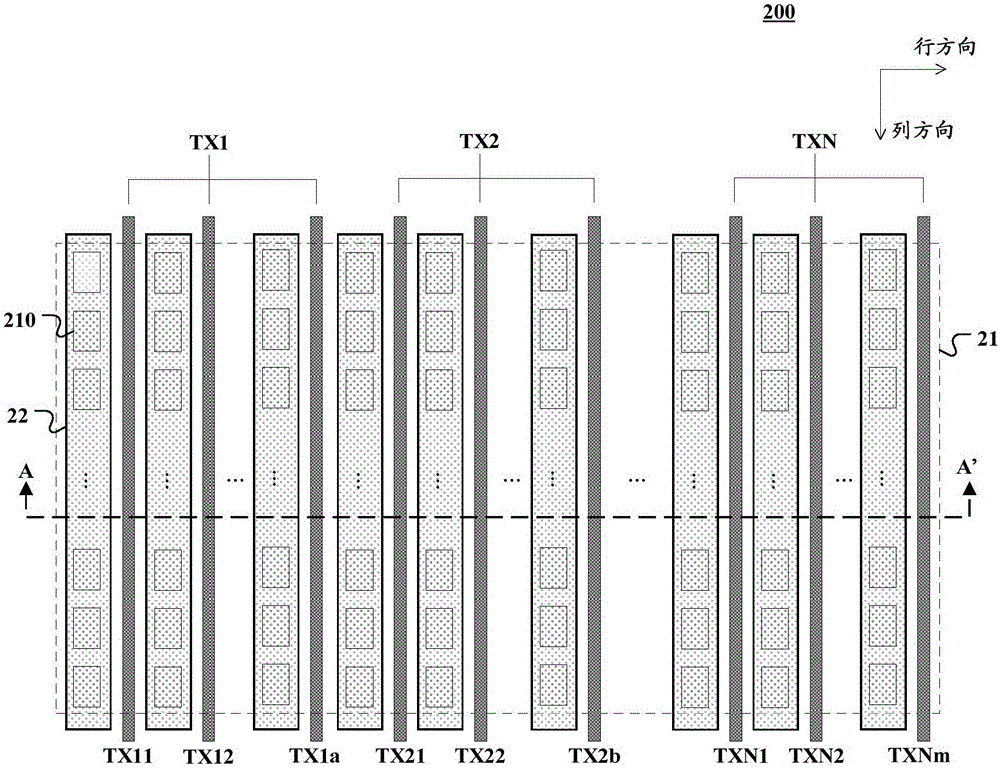

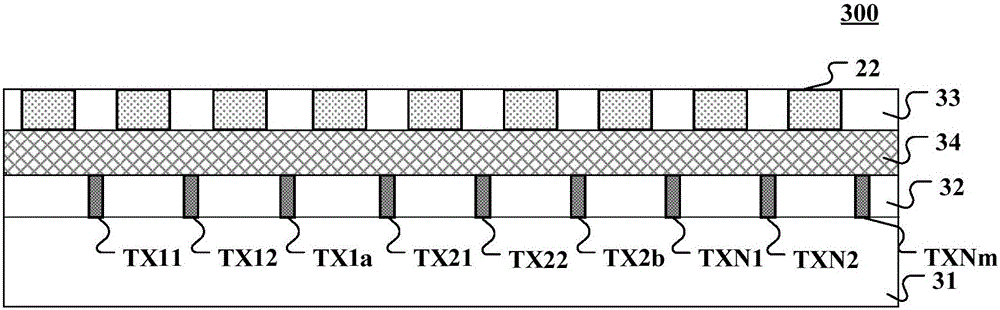

PendingCN106293212ALower resistanceImprove touch sensitivityStatic indicating devicesNon-linear opticsTransfer procedureDisplay device

The invention discloses an array substrate, a display panel and a driving method thereof and a display device. According to one embodiment, the array substrate comprises sub-pixels arranged in an array in the row direction and the column direction and multiple touch electrodes arranged in the row direction; each touch electrode comprises multiple touch sub-electrodes arranged sequentially in the row direction, and each touch sub-electrode provides a data signal to one column of sub-pixels at the display stage; each touch sub-electrode receives a touch detection signal at the touch detection stage. According to the embodiment, the touch sub-electrodes are reused as data lines, therefore, losses of touch signals in the transmission process in the touch electrodes can be effectively reduced, the touch sensitivity of a display screen is improved, and meanwhile driving power consumption can be lowered.

Owner:XIAMEN TIANMA MICRO ELECTRONICS +1

Permanent magnet frequency conversion power generator

InactiveCN102857151ASignificant progressSlow downBatteries circuit arrangementsMagnetic circuit stationary partsPush pullMagnet

The invention discloses a permanent magnet frequency conversion power generator which comprises an outer shell, a main shaft, a bearing and coils. The permanent magnet frequency conversion power generator is characterized in that a permanent magnet block is pasted on the inner part of the outer shell; the main shaft is in a hollow structure, and is fixed on the bearing; a plurality of coils are wound on the main shaft; a wire is guided out from the hollow shaft; the outer shell is driven by wind power, water power, fire power and other motive powers to rotate around the main shaft; the coils cut off a magnetic force wire during the rotational process of the permanent magnet and emits current, and the current is output to an electricity using device or a storage electric appliance from the wire at the middle of the main shaft; and a full-magnetic suspending and magnetic push-pull combined device is formed in the shell through the pasted permanent magnet block and an installation panel, so that the permanent magnet frequency conversion power generator can rotate continuously when rotating to a heteropolar interval, the friction resistance in operation is reduced, the driving power consumption is reduced, and rated power output can be emitted out with external micro force driving and low rotation speed, and electricity energy is supplied independently and normally.

Owner:宋开泉 +1

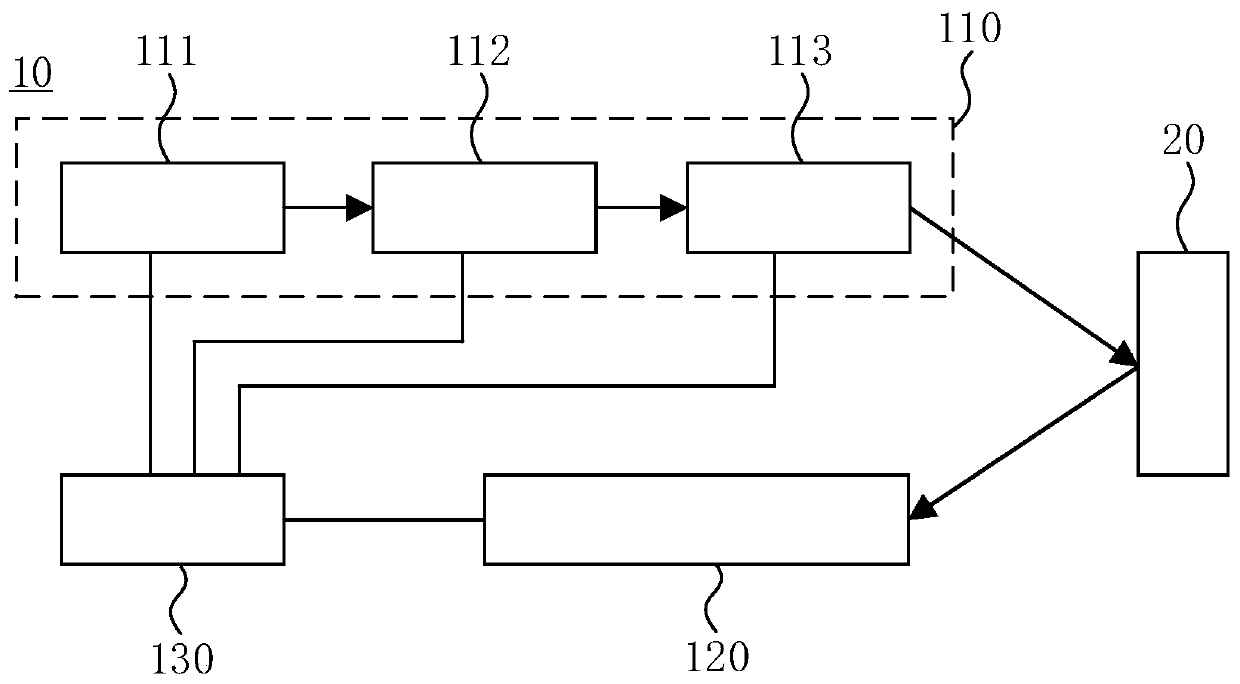

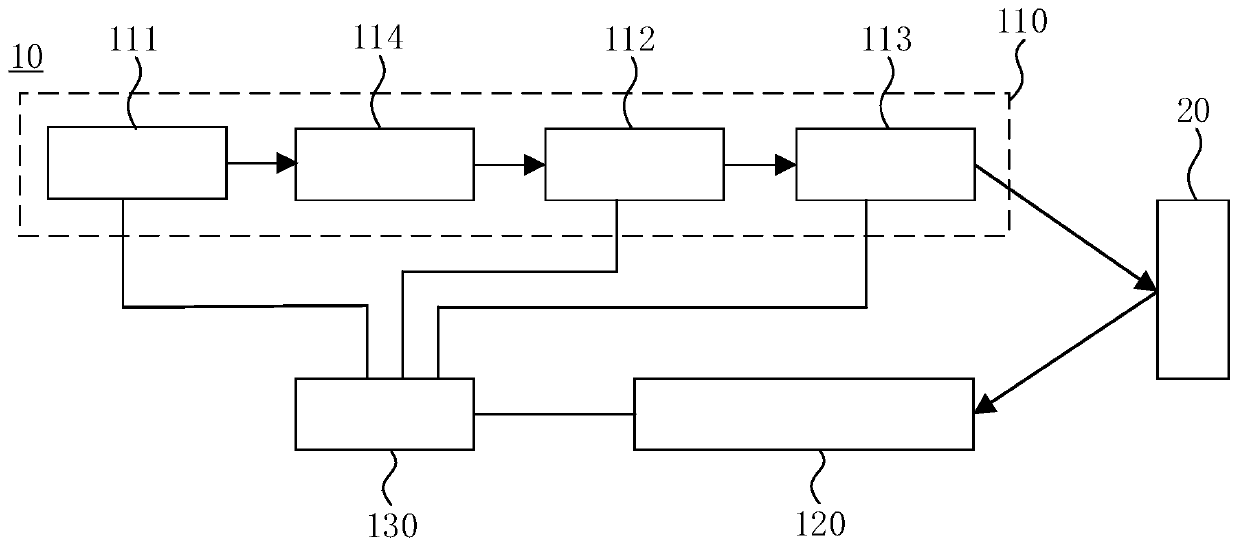

Stereoscopic image display device and driving method thereof

InactiveUS20130258466A1Reduce drive frequencyReduce power consumptionStatic indicating devicesOptical elementsVoltageScan line

A stereoscopic image display device includes: a scan driver for transmitting scan signals to scan lines; a data driver for transmitting data signals to data lines; a display unit including pixels and configured to receive a corresponding data signal when a corresponding scan signal is transmitted to the pixels; a power supply controller for supplying a driving voltage to drive the pixels; and a controller for controlling the scan driver, the data driver, and the power supply controller, for generating an image data signal corresponding to each period of a plurality of periods, and for supplying the corresponding image data signal to the data driver. The power supply controller controls the driving voltage to block light emitting during a first view point image non-light emitting period and a second view point image non-light emitting period.

Owner:SAMSUNG DISPLAY CO LTD

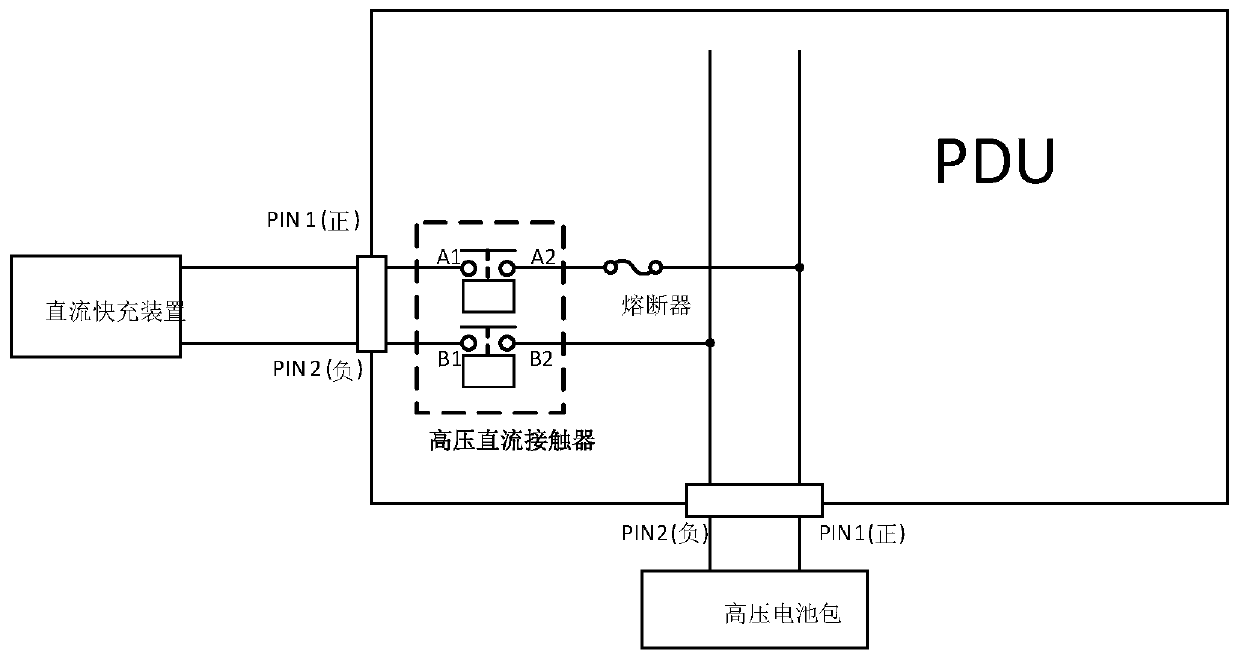

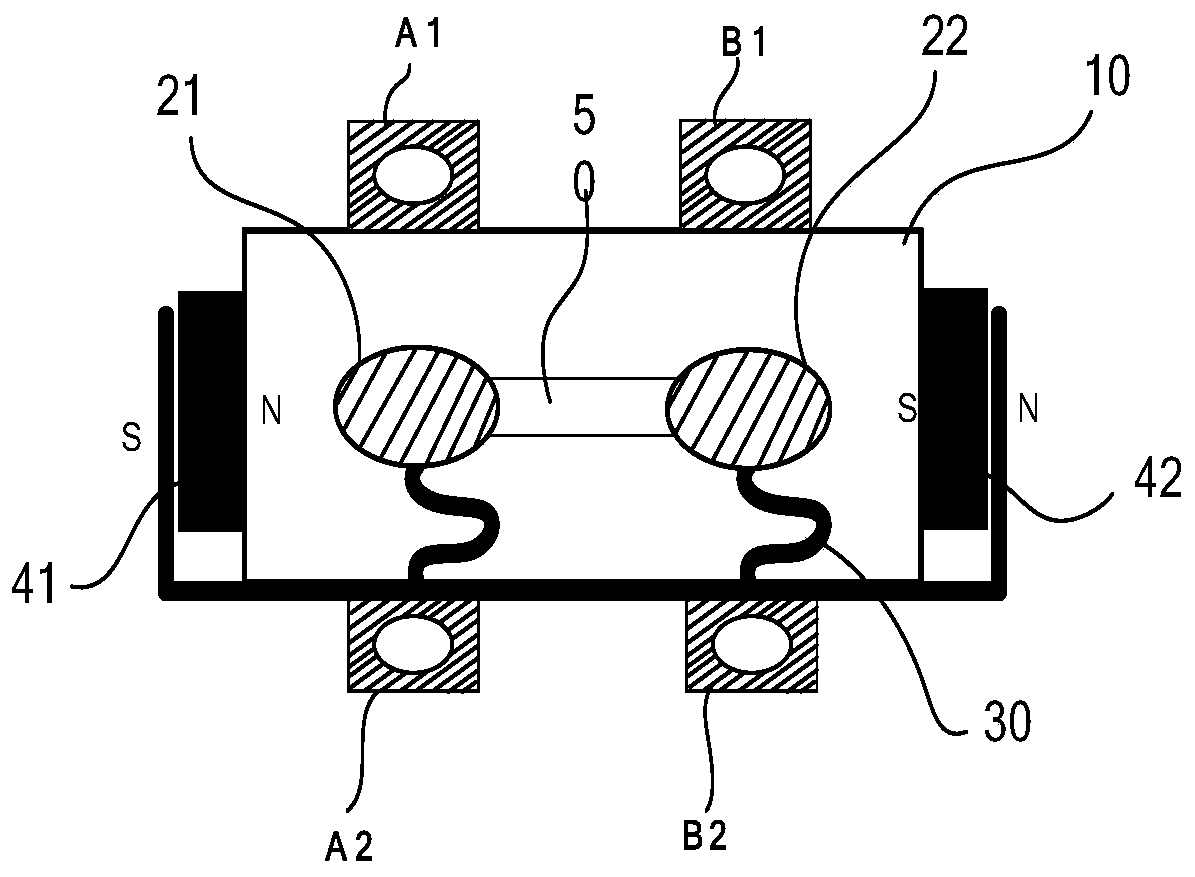

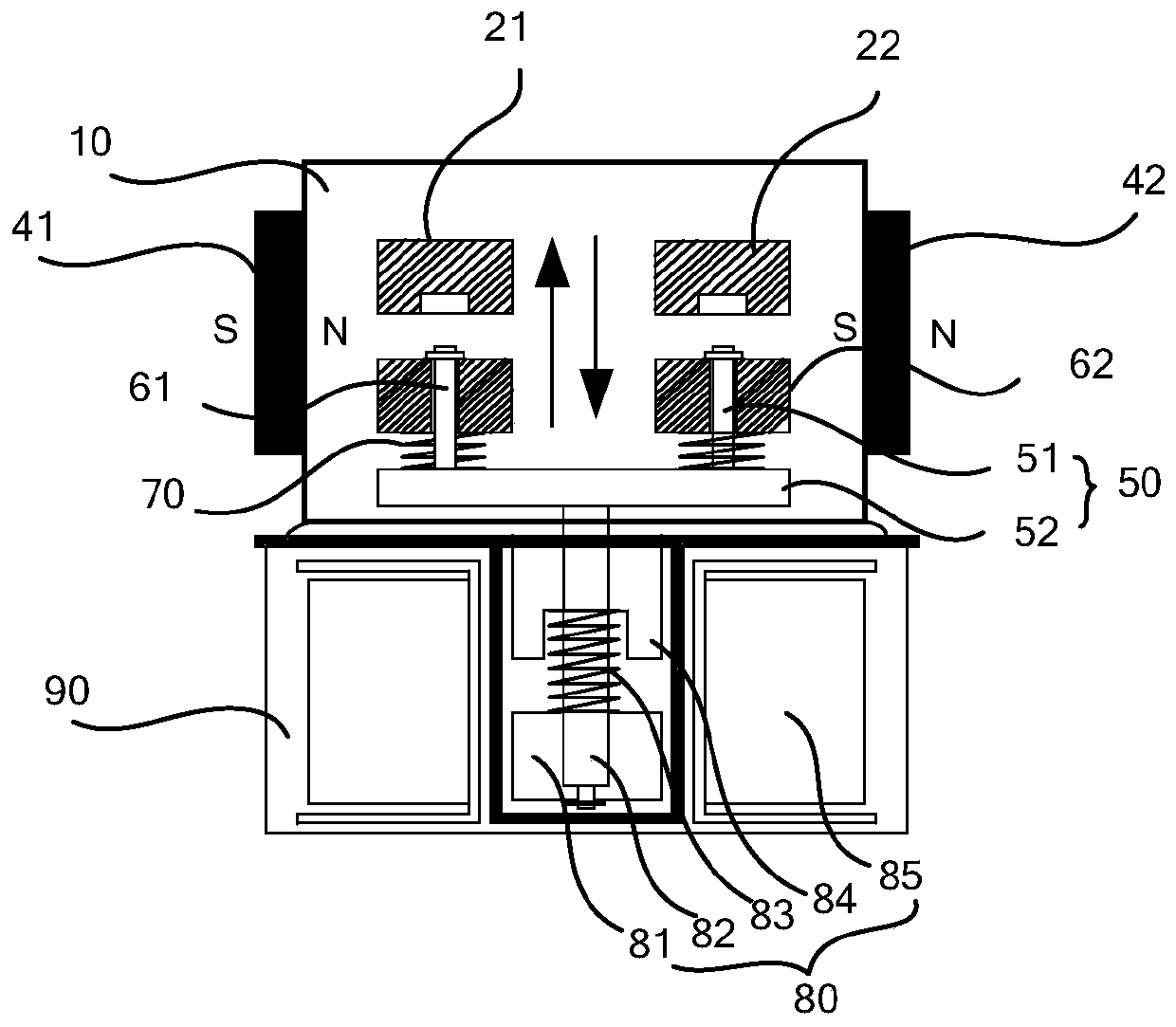

DC contactor and automobile

ActiveCN110783147AReduce drive power consumptionReduce difficultyElectric switchesElectric vehicle charging technologyControl theoryContact resistance

The invention provides a DC contactor and an automobile. The DC contactor comprises a shell, a first static contact and a second static contact fixed to the shell, and a first moving contact and a second moving contact located in the shell. A driving mechanism comprises an insulating rod connected with the first moving contact and the second moving contact, a driving assembly for driving the insulating rod to drive the first moving contact and the second moving contact to synchronously move towards the first static contact and the second static contact, and a pressing assembly used for pushingthe moving contact to be pressed on the static contact. Through the description, only two pairs of contacts are adopted to achieve on-off of a two-pole circuit, the total contact resistance is reduced by half compared with the prior art, and the problem that in the prior art, the through-current loss is large is solved. Meanwhile, half of coil driving power consumption is reduced; and only a single driving mechanism is needed to drive the two contacts, so that the difficulty of realizing the on-off synchronism of the two-pole contacts is greatly reduced.

Owner:HUAWEI DIGITAL POWER TECH CO LTD

Light refractory castable material for heat insulation lining of cast steel plate (CPS) furnace roller

The invention discloses a light refractory castable material for a heat insulation lining of a cast steel plate (CPS) furnace roller. The light refractory castable material comprises the following components by weight percent: 40-50% of light mullite bone material, 5-8% of flint clay with a particle size of 0.1-1mm, 5-7% of kyanite powder, 6-9% of first-class bauxite chamotte with a particle size of less than or equal to 180 meshes, 7-9% of silicon micro powder, 5-8% of alpha-Al2O3 micro powder, 10-18% of bauxite cement, 1-4% of refractory fiber, 1-1.5% of spodumene, 0.05-0.154% of sodium hexametaphosphate, 0.05-0.15% of organic water reducing agent, 0.04-0.07% of organic silane coupling agent and 0.013-0.06% of defoaming agent. The refractory castable material has the characteristics of light volume weight, strong high temperature resistance, good mechanical property, good heat insulation property and excellent thermal shock stability performance.

Owner:武钢集团有限公司 +1

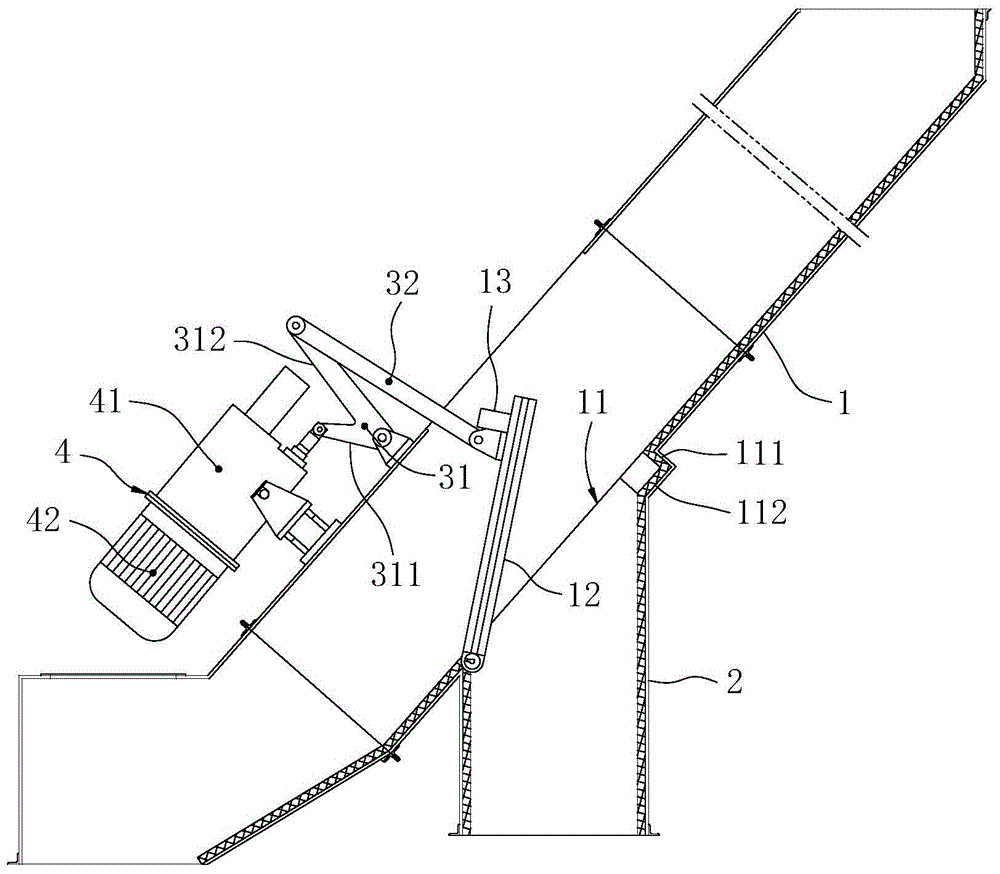

Distribution tank

The invention discloses a distribution tank which has not high requirements on the connection of a rotationally connecting part of a turning plate and makes the turning plate turn more conveniently. The distribution tank comprises a main conveyor chute provided with a main discharge hole at the lower end thereof, a secondary discharge chute arranged on the main conveyor chute, a crank-link mechanism and a drive mechanism, wherein an opening which is located in the main conveying chute and communicated with the secondary discharge chute is provided with the turning plate, and the lower end of the turning plate is rotationally connected with the main conveying chute; the drive mechanism is arranged on the main conveying chute and is connected with the turning plate through the crank-link mechanism, and the crank-link mechanism is driven by the drive mechanism to drive the turning plate to rotate around the rotationally connecting part. The drive mechanism drives the turning plate to turn by virtue of the crank-link mechanism which is directly connected with the turning plate, and turning force needed is smaller when the turning plate turns, therefore the turning plate turns more conveniently; meanwhile, the load on the rotationally connecting part between the turning plate and the main conveying chute is lower, therefore the requirements on the connection of the rotationally connecting part between the turning plate and the main conveying chute is not high.

Owner:SICHUAN HONGJIAN HEAVY MACHINERY MFG

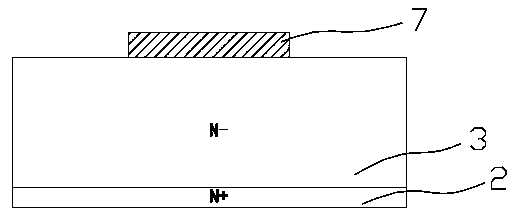

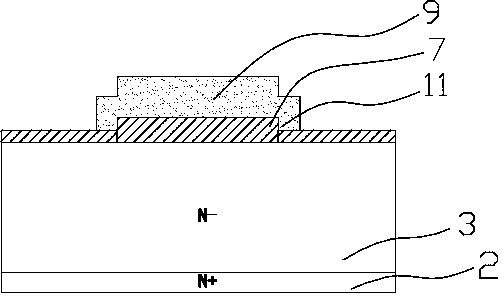

Low-grid charge power device and manufacturing method thereof

InactiveCN103730506AReduce drive power consumptionIncreasing the thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceGate oxide

The invention discloses a low-grid charge power device. A combined type grid oxidation layer composed of a primary grid oxidation layer and a secondary grid oxidation layer is adopted in a grid oxidation layer of a grid area, a step structure is formed between the secondary grid oxidation layer and the primary grid oxidation layer, the width of the primary grid oxidation layer is smaller than or equal to the width of the top face of an N- type drift area, the thickness of the primary grid oxidation layer can be independently increased so that the overall thickness of the grid oxidation layer can be increased and the vertical thickness of the secondary grid oxidation layer in contact with a channel cannot be influenced, therefore, the capacitance between the grid area and a drain electrode is reduced under the premise of not influencing the turn-on and turn-off speed of the device, the aim of reducing grid charges is achieved, and the drive power consumption of turning on and off the device is lowered. The invention further discloses a manufacturing method of the low-grid charge power device. Under the condition of being compatible with an existing process, the primary grid oxidation layer and the secondary grid oxidation layer are formed successively by two steps to obtain the combined type grid oxidation layer, the process steps are simple, and operability is strong.

Owner:HANGZHOU LION MICROELECTRONICS CO LTD

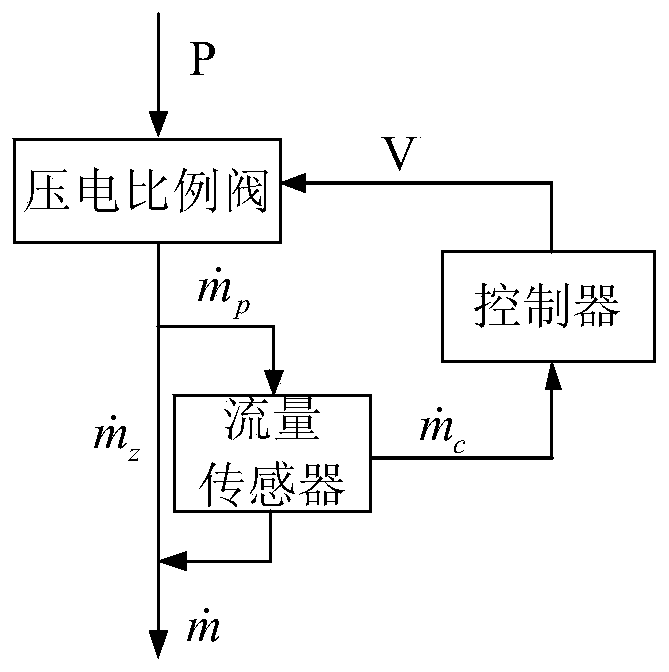

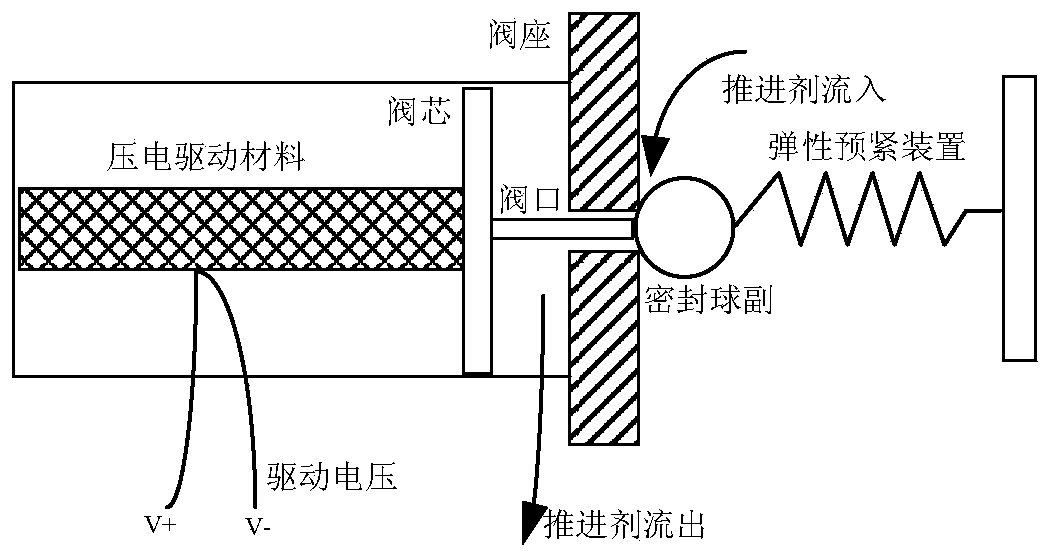

Micro-flow control system and method based on piezoelectric proportional valve

ActiveCN110502041AReduce drive power consumptionDisplacement stabilityFlow control using electric meansElectricityControl system

The invention, which belongs to the technical field of spacecraft electric propulsion, provides a micro-flow control system and method based on a piezoelectric proportional valve. The system comprisesa valve for controlling a flow output, a controller, and a flow sensor. The valve is in an off state when no drive voltage is loaded and the flow output is zero. After a driving voltage signal outputted by the controller is received, the opening degree of the valve is controlled based on the driving voltage signal and the output flow is controlled, wherein the output flow is divided into a plurality of main path flows and a bypass flow based on a certain proportion. The flow sensor detects the flow value of the single bypass flow within an ith control period in real time, generates a flow digital signal, and inputs the signal into the controller. The controller receives the flow digital signal within the ith control period to obtain a measured actual flow and outputs a driving voltage signal for controlling the opening degree of the valve based on a control algorithm. The micro-flow control system has advantages of stable performance, flexible adjustment, and high precision.

Owner:BEIJING INST OF CONTROL ENG