Pre-amplifier circuit of CMOS comparator

A preamplifier and comparator technology, which is applied to DC-coupled DC amplifiers, differential amplifiers, and improved amplifiers to reduce temperature/power supply voltage changes, etc. Pole frequency reduction, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

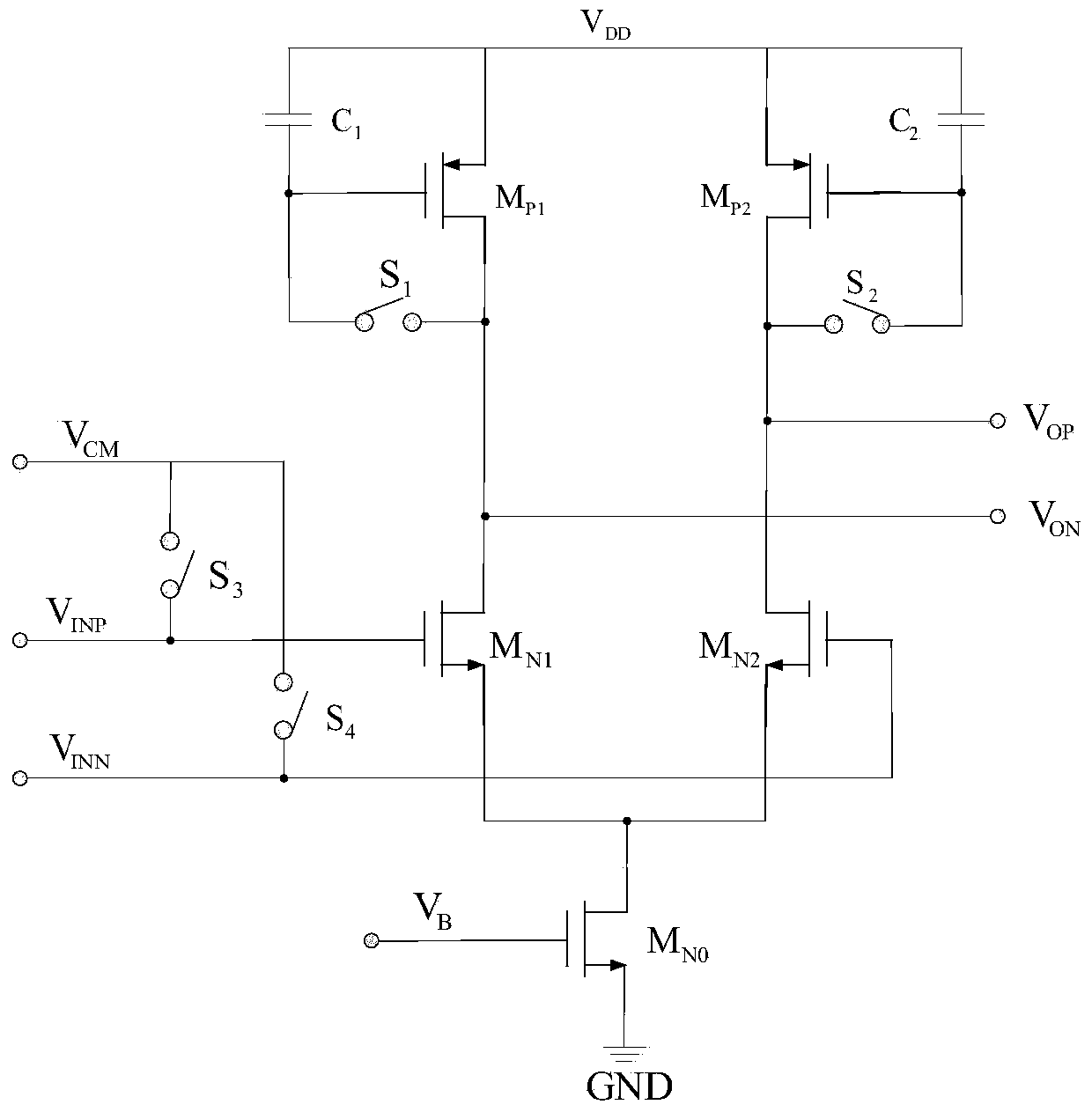

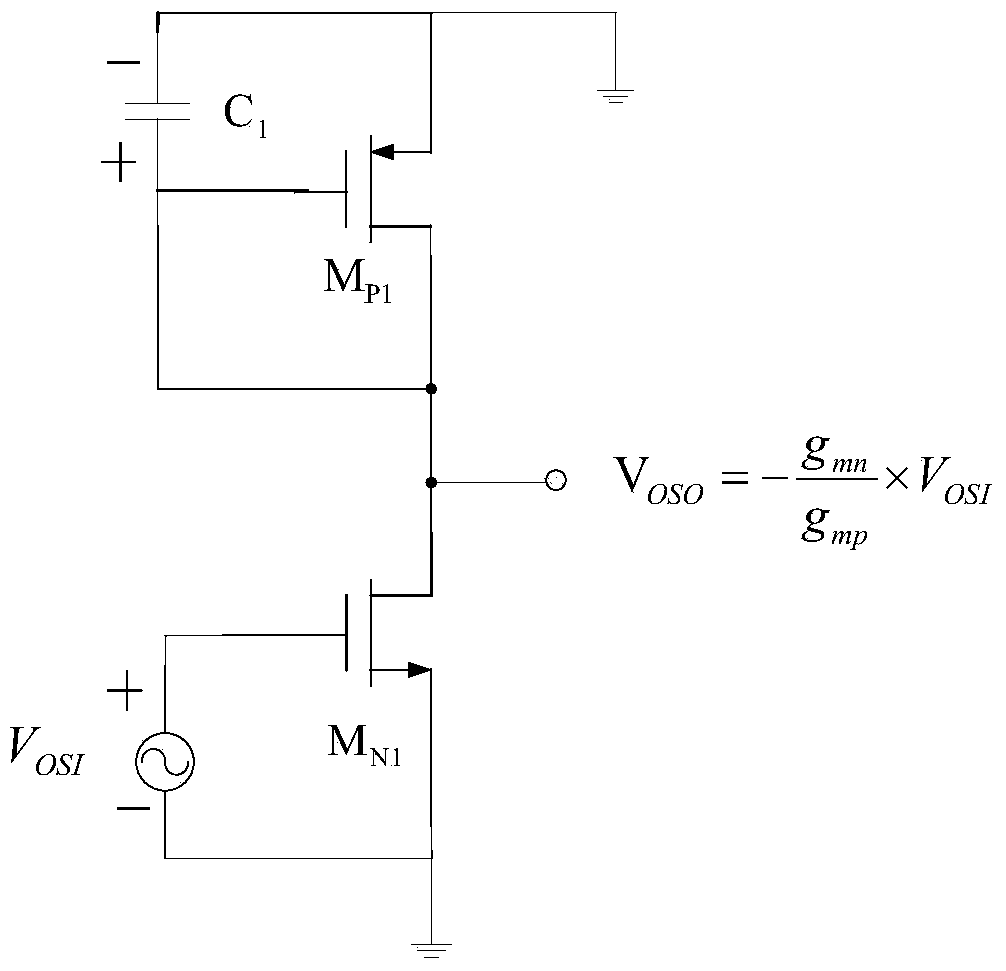

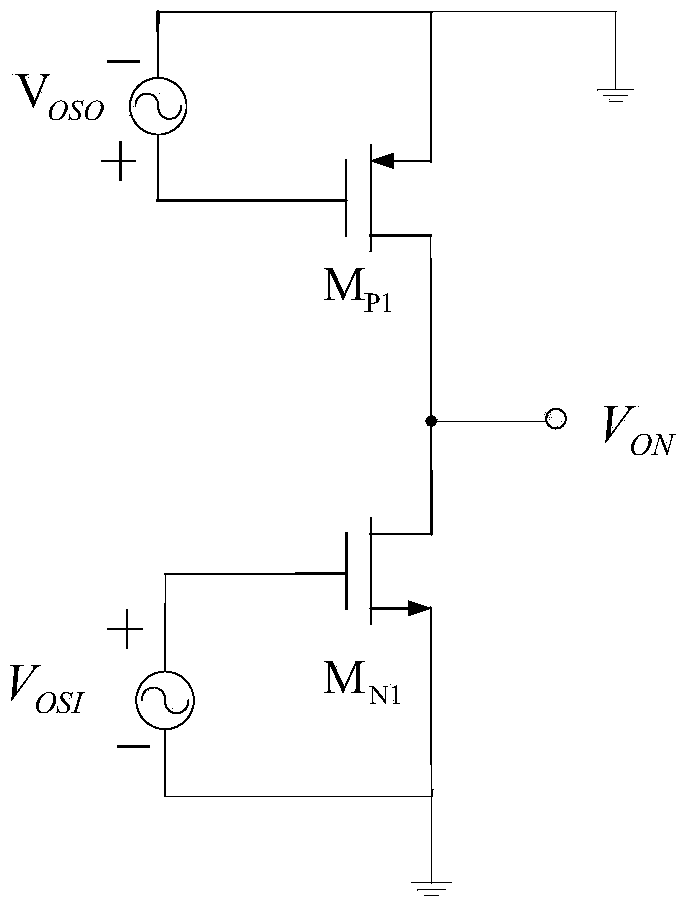

[0012] refer to Figure 1-3 . The preamplifier circuit of the CMOS comparator of the present invention comprises an NMOS transistor M N1 , NMOS transistor M N2 , NMOS transistor M N0 , PMOS transistor M P1 , PMOS transistor M P2 , switch S 1 , switch S 2 , switch S 3 , switch S 4 , storage capacitor C 1and storage capacitor C 2 . NMOS transistor M N1 and NMOS transistor M N2 As a differential input pair; PMOS transistor M P1 and PMOS transistor M P2 As a load, switch S 1 and S 2 respectively connected to the PMOS transistor M P1 and PMOS transistor M P2 Between gate and drain; offset storage capacitor C 1 and offset storage capacitor C 2 One end of each is connected to the PMOS transistor M P1 and PMOS transistor M P2 gate, the offset storage capacitor C 1 and offset storage capacitor C 2 The other end is connected to the power supply V DD superior. NMOS transistor M N1 and NMOS transistor M N2 The gates are respectively connected to the input signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More