MOS transistor structure and its manufacturing method

A technology of MOS transistor and manufacturing method, applied in the field of MOS transistor structure and its manufacturing, can solve problems such as inability to meet the development requirements of integrated circuits, and achieve the effects of eliminating RDF effect, reducing power consumption, and improving on-current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0041] Such as Figure 9 As shown, the MOS transistor structure 100 in this embodiment includes:

[0042] Substrate 101;

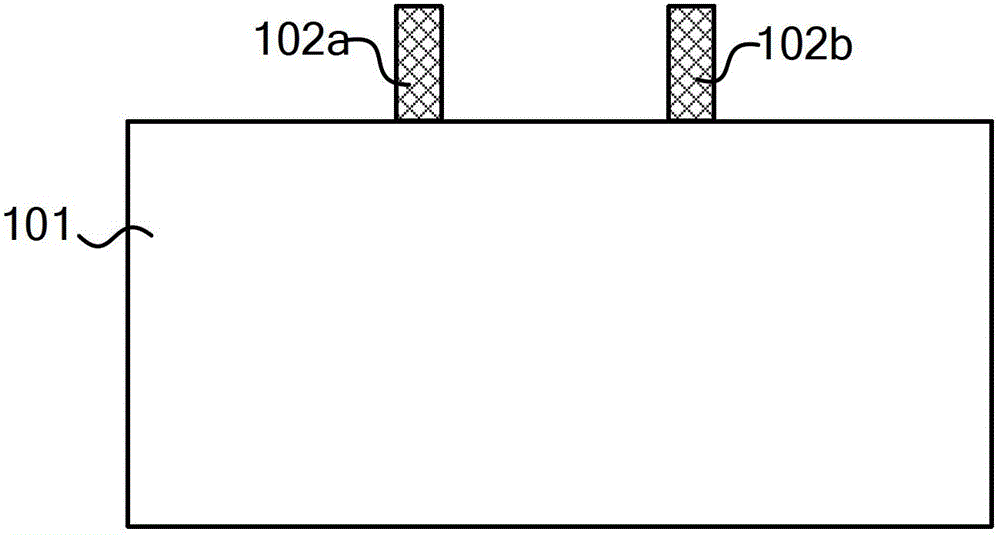

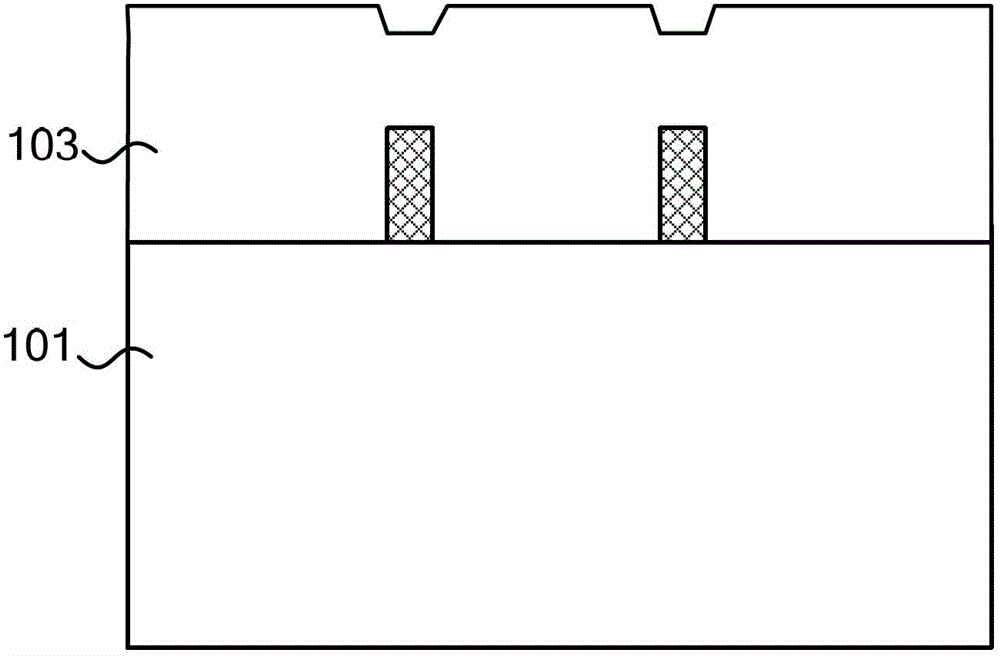

[0043] an isolator formed in the substrate 101, the isolator includes a first isolation block 102a and a second isolation block 102b;

[0044] A lightly doped layer 104 formed on the substrate 101 and the spacer;

[0045] a source region 109 and a drain region 110 formed on both sides of the spacer;

[0046] an undoped layer 105 formed on the lightly doped layer 104;

[0047] a gate structure formed on the undoped layer 105, the gate structure comprising a gate oxide layer 106 and a gate 107; and

[0048] Gate spacers 108 are formed on both sides of the gate structure.

[0049] Wherein, the cross-sectional width of the undoped layer 105 is smaller than or equal to the distance between the first isolation block 102a and the second isolation block 102b, so as to suppress the short channel effect caused by too close source / drain distance.

[0050] Combi...

Embodiment 2

[0061] Such as Figure 16 As shown, the MOS transistor structure 200 in this embodiment includes:

[0062] substrate 201;

[0063] an isolator 202 formed in the substrate 201;

[0064] A lightly doped layer 204 formed on the substrate 201 and the spacer 202;

[0065] a source region 209 and a drain region 210 formed on both sides of the spacer 202;

[0066] an undoped layer 205 formed on the lightly doped layer 204;

[0067] a gate structure formed on the undoped layer 205, the gate structure comprising a gate oxide layer 207 and a gate 208; and

[0068] Gate spacers 209 are formed on both sides of the gate structure.

[0069] Wherein, the cross-sectional width of the undoped layer 205 is smaller than or equal to the cross-sectional width of the spacer 202 .

[0070] Combine below Figure 10 to Figure 16 Each step of the method for manufacturing the MOS transistor structure in Embodiment 2 of the present invention will be described in detail.

[0071] Such as Figure ...

Embodiment 3

[0080] Such as Figure 28 As shown, the MOS transistor structure 300 in this embodiment is the same as the MOS transistor structure 100 in the first embodiment, and will not be repeated here.

[0081] Combine below Figure 17 to Figure 28 Each step of the manufacturing method of the MOS transistor structure according to the third embodiment of the present invention will be described in detail.

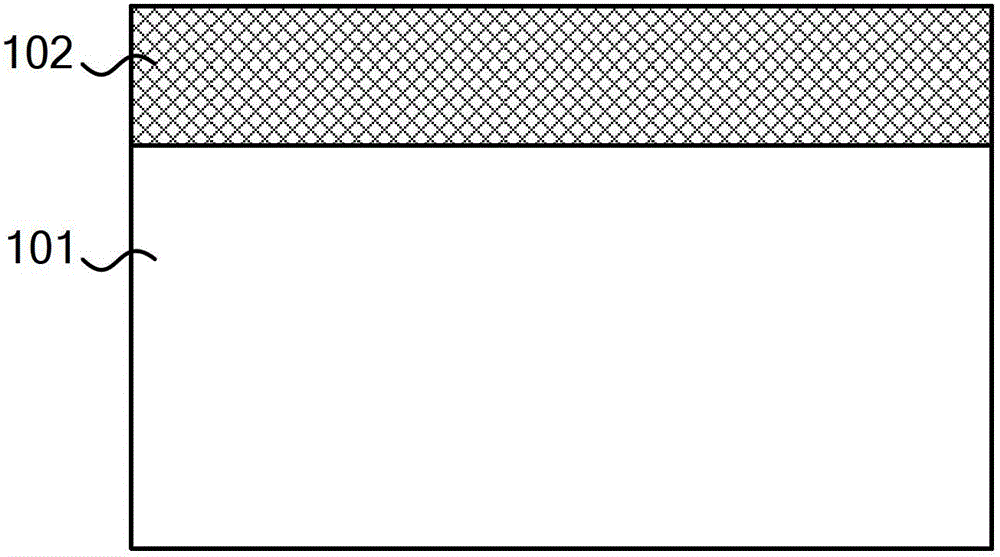

[0082] First, if Figure 17 As shown, a substrate 301 is provided, and a buffer layer film and a mask layer film are sequentially deposited on the substrate 301 . Then etching removes part of the mask layer film, the buffer layer film and part of the thickness of the substrate to form the mask layer 303 and the buffer layer 302 . For the convenience of description, the substrate that has not been etched at all is called the first substrate 301a, the substrate remaining under the mask layer 303 and the buffer layer 302 is called the second substrate 301b, and the mask layer 303 , th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More