Triggering vibration real-time correction circuit and method in random sampling process

A technology of triggering jitter and real-time correction, applied in electrical components, pulse processing, pulse technology, etc., can solve the problems of nonlinear error of double-slope widening circuit, expansion multiple affecting interpolation time accuracy, increasing circuit board volume, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

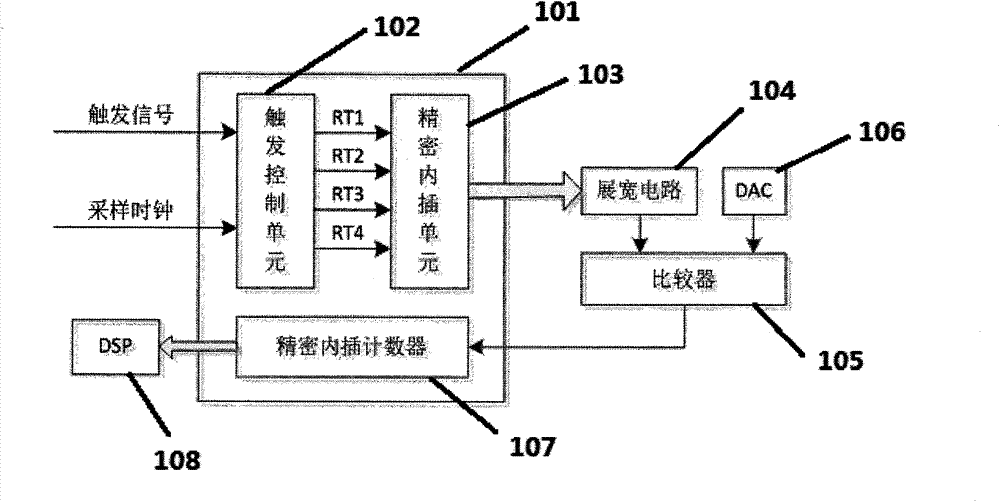

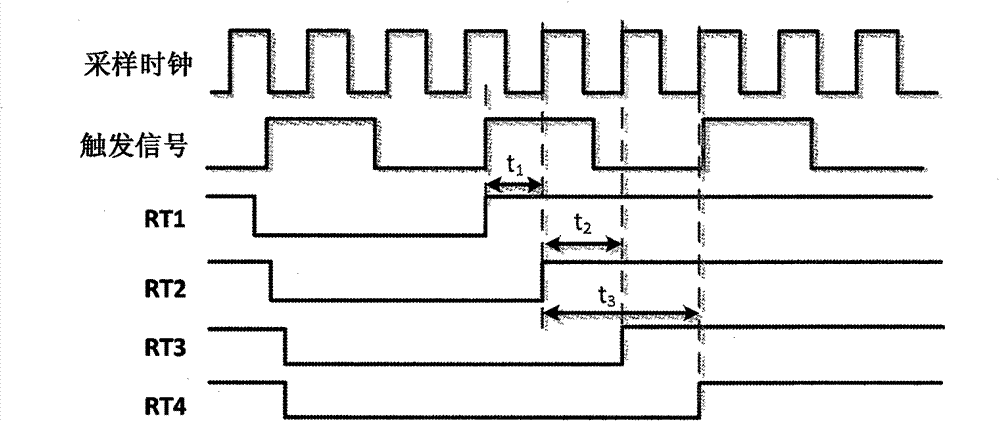

[0013] Such as Figure 1-2 As shown, in the pulse power measurement, in the random sampling process, since the signal under test is arbitrary, the trigger signal synchronous with the signal under test is also arbitrary, and the trigger signal is not related to the sampling clock, so the trigger signal and the trigger point after The time interval between the first sampling clocks of , causes trigger jitter, which is a uniformly distributed and bounded random variable. The key to random sampling is to calculate the time interval between the trigger point and the sampling point, so as to determine the exact position of the sampling point on the screen.

[0014] The technical problems to be solved by the present invention include: 1. Design of a digital precision interpolation identification circuit; 2. Optimal design of a double-slope expansion circuit; 3. Precision interpolation time calibration technology.

[0015] Design of hardware circuit

[0016] Such as figure 1 As sho...

Embodiment 2

[0034] On the basis of the above examples, if Figure 1-2 As shown, a trigger jitter real-time correction circuit in the random sampling process, wherein the trigger signal and sampling clock settings are connected to the trigger control unit 102 in the editable logic unit FPGA101, and the trigger control unit 102 generates four-way timing After the signal is set, it is connected to the precision interpolation unit 103 in the editable logic unit 101, and the time interval t between the rising edge of the trigger signal and the rising edge of the first sampling clock thereafter is 1 , the time interval t of one sampling clock cycle 2 , or the time interval t between two sampling periods 3 Go to the stretching circuit 104 and the comparator 105, and then set it to be connected with the precision interpolation counter 107 in the editable logic unit 101, and then input the count value to the digital signal processor DSP108 for calculating the precision interpolation time interval...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More