Floating gate electricity erasable read-only memory and manufacturing method thereof

A read-only memory, floating gate technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, circuits, etc., can solve the problems of reduced voltage coupling efficiency, reduced dielectric area, reduced coupling capacitance, etc., to reduce the operating voltage. , the effect of increasing the coupling coefficient and increasing the effective voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

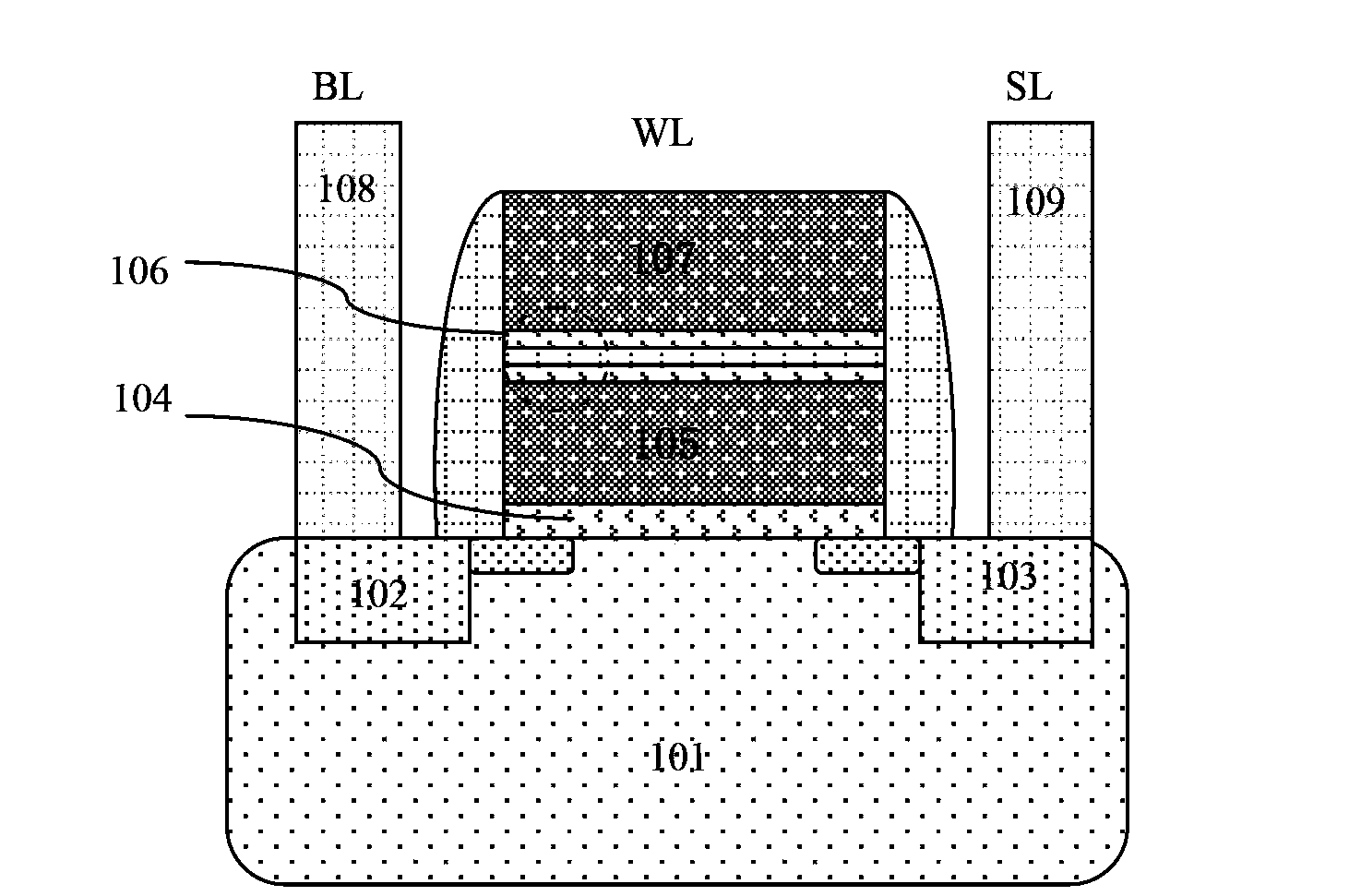

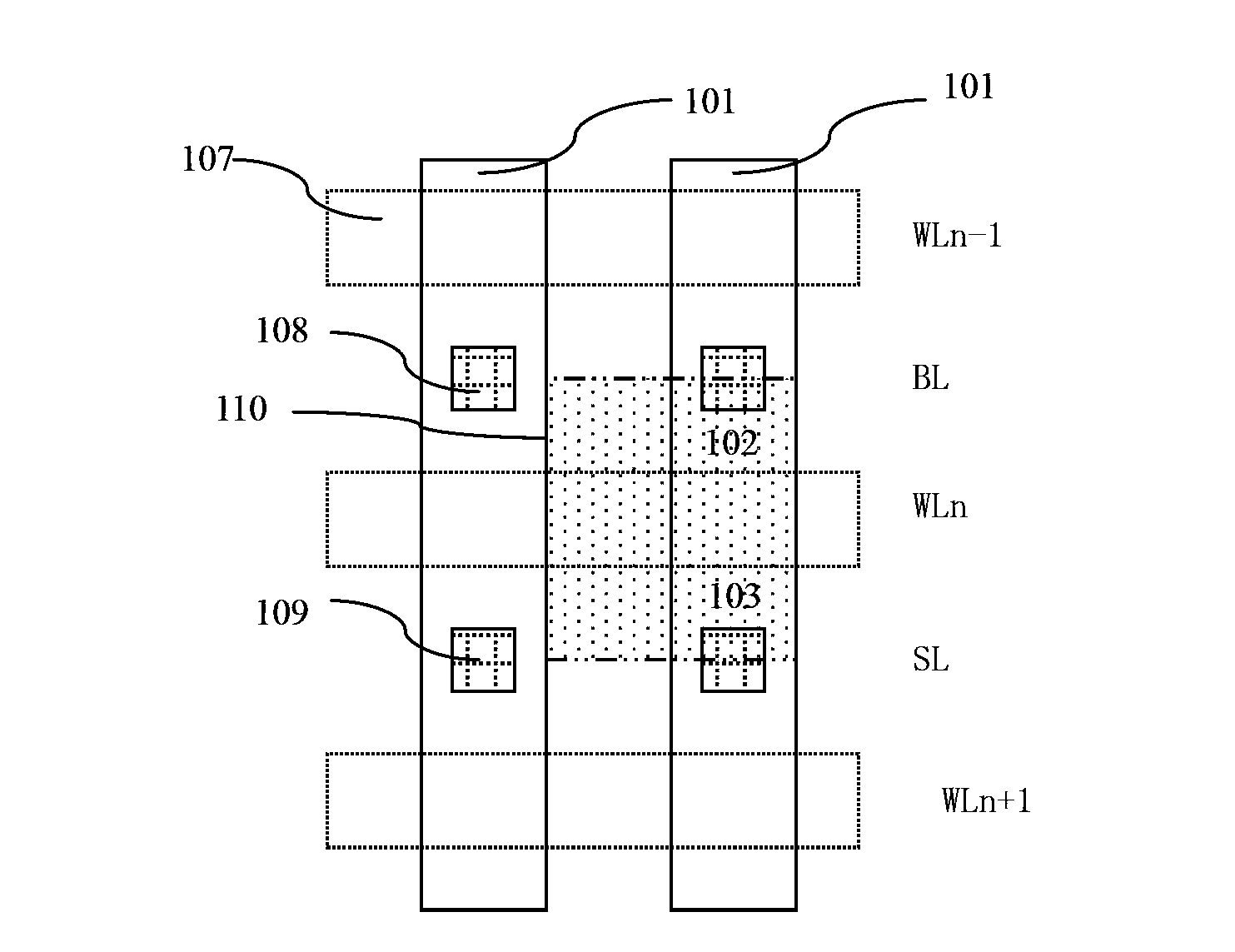

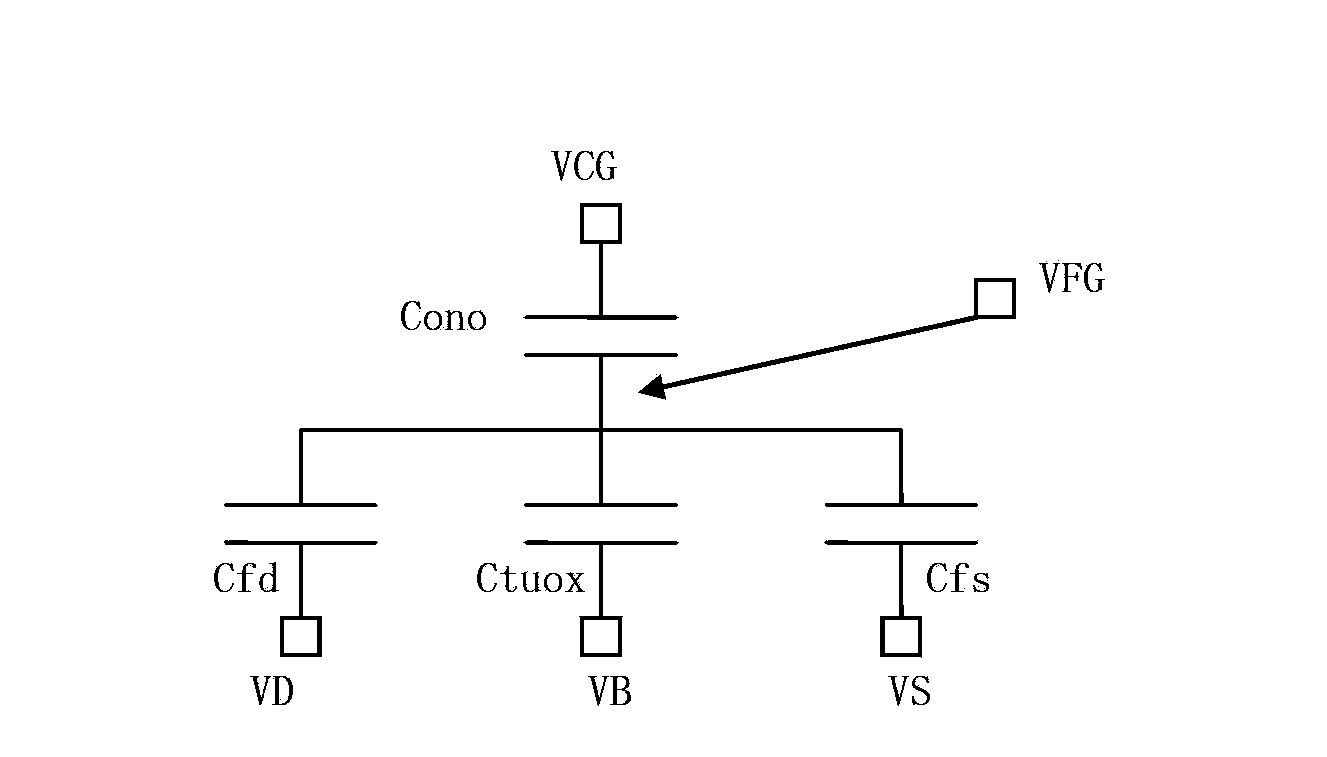

[0034] Such as Figure 4 As shown, it is a schematic diagram of the cell structure of the floating gate EEPROM according to the embodiment of the present invention; the floating gate EEPROM according to the embodiment of the present invention is described by taking an N-type device as an example, and the P-type device The doping type of each region such as the source and drain region 2 and the channel region is opposite to that of the N-type device. In the embodiment of the present invention, the floating gate electrically erasable read-only memory is formed on a silicon substrate, and the active region 3 is isolated by field oxygen, which can be shallow trench field oxygen (STI) or local field oxygen (LOCOS), A P-type well 1 is formed in the active region 3, and the cell structure of the floating gate electrically erasable read-only memory includes:

[0035] The source region 3 is composed of the N-type ion implantation region formed in the P-type well 1; the drain region 2 ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap