A Low-power Phase Detector Used in All-Digital Phase-Locked Loop

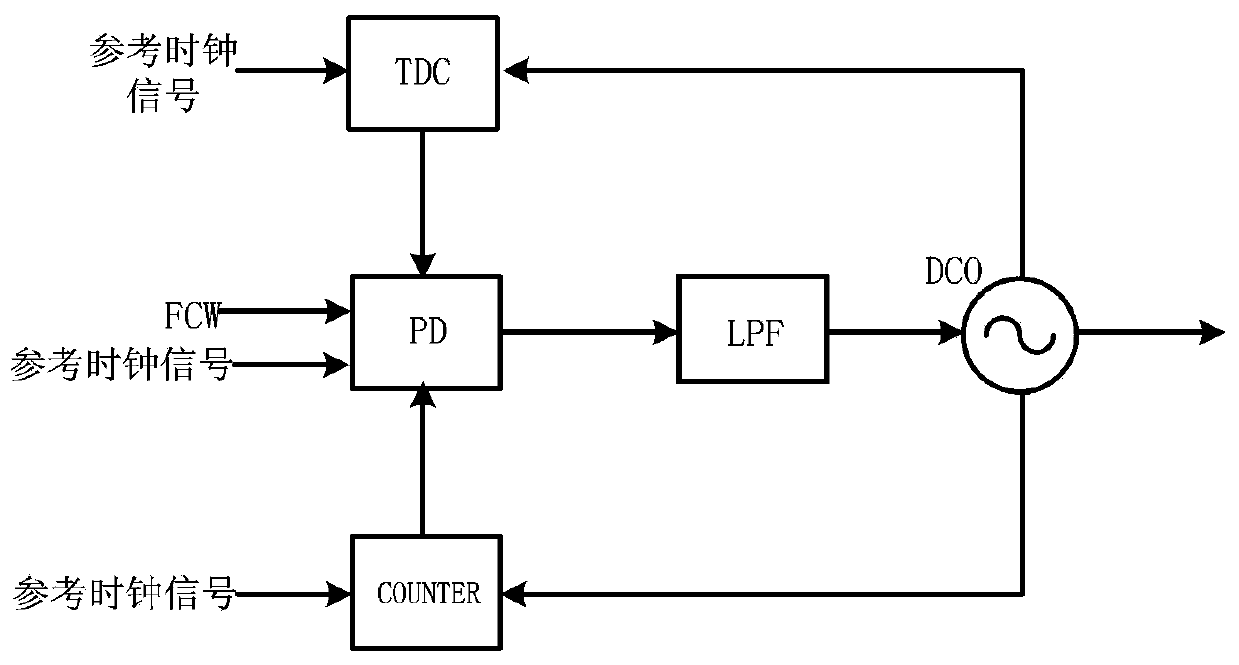

An all-digital phase-locked loop and phase detector technology, which is applied in the field of microelectronics, can solve problems such as high power consumption, and achieve the effects of reduced operation steps, easy implementation, and reduced power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

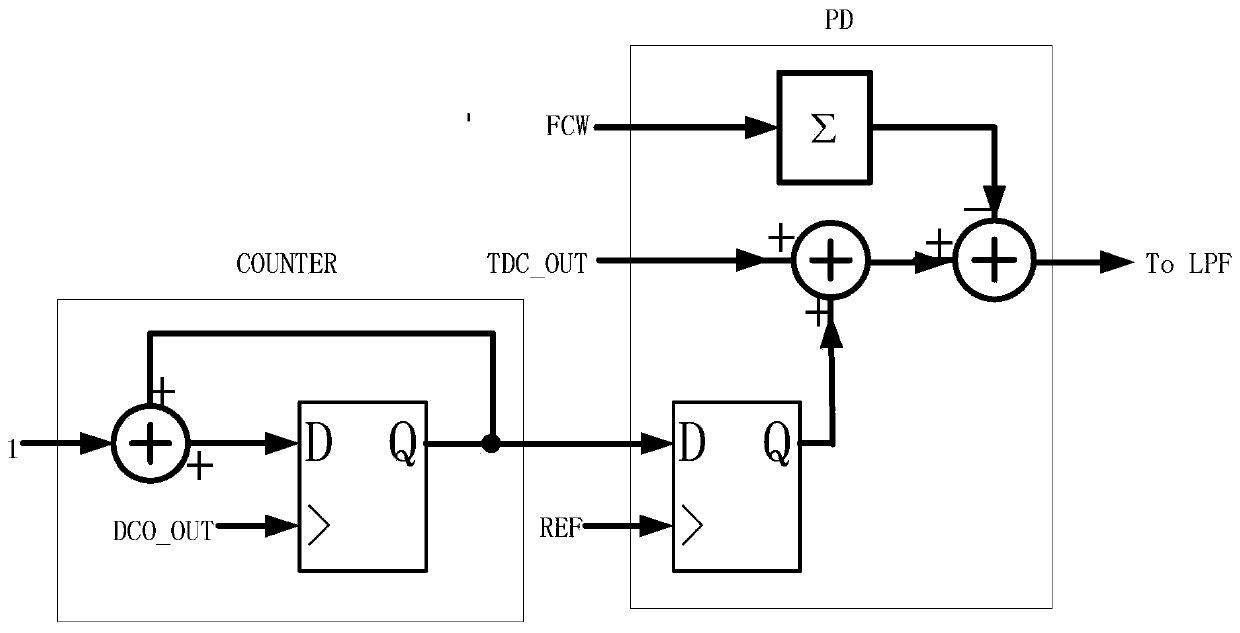

[0024] The counter used for the phase detector of the all-digital phase-locked loop adopts an accumulative counter, and directly obtains At the same time, when the circuit is realized, the Change the order of operation, change first difference and then accumulation to first accumulation and then difference. The calculation formula is:

[0025]

[0026] Among them, FCW is the frequency control word, is the accumulated output of the K-th clock cycle counter, σ K+1 is the output of the time-to-digital converter at the K+1th clock cycle.

[0027] The circuit implementation method of the phase detector of the present invention adopts formula (3), as figure 2 Shown: σ K+1 is the output of the TDC in the K+1th clock cycle, and It is the output of the accumulative COUNTER (the accumulative COUNTER is the accumulative value output in all cycles of the COUNTER in the prior art, and the accumulative COUNTER can be directly triggered by the output of the DCO) in the Kth cycle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More