High-speed data extracting method achieving input and output arranged in sequence based on FPGA

An input and output, high-speed data technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of extraction conditions and limitations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

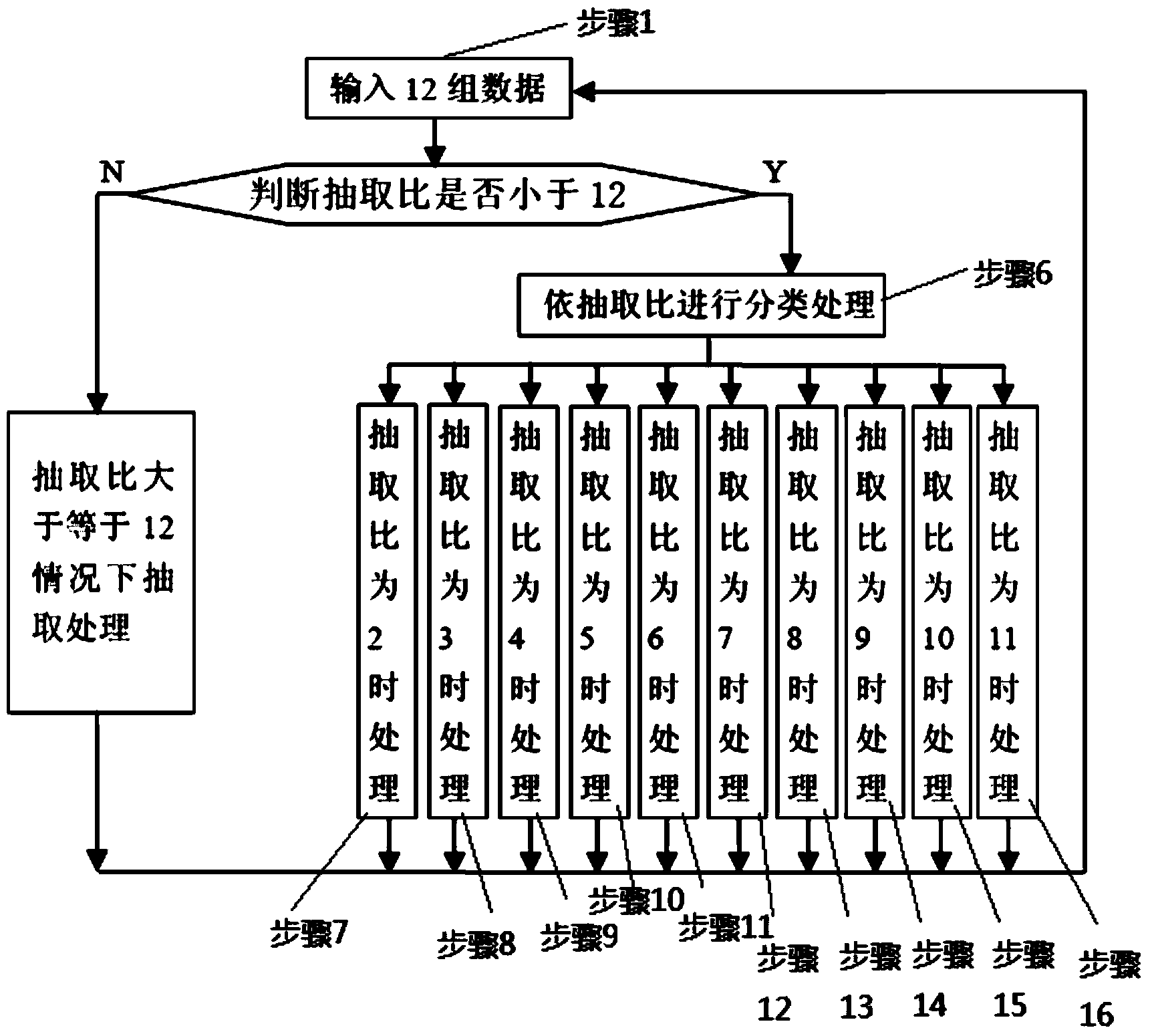

[0033] The present invention extracts 12 sets of data input each time, and solves the problem in two cases during design, one is the case that the extraction ratio is less than 12, and the other is the case that the extraction ratio is greater than or equal to 12. For the case where the extraction ratio is less than 12, because multiple values may be extracted in one input, each extraction ratio is processed separately according to the different extraction ratios. For the case where the extraction ratio is greater than or equal to 12, there is at most one extraction value for each input, which can be realized by performing a loop algorithm. The extraction method can realize arbitrary extraction ratio extraction of high-speed A / D sampling data.

[0034] The input and output data of this method are 12 groups of data groups arranged in a certain order, and the order and definition of the fields of the input and output data groups are as follows:

[0035] The input is defined a...

Embodiment 2

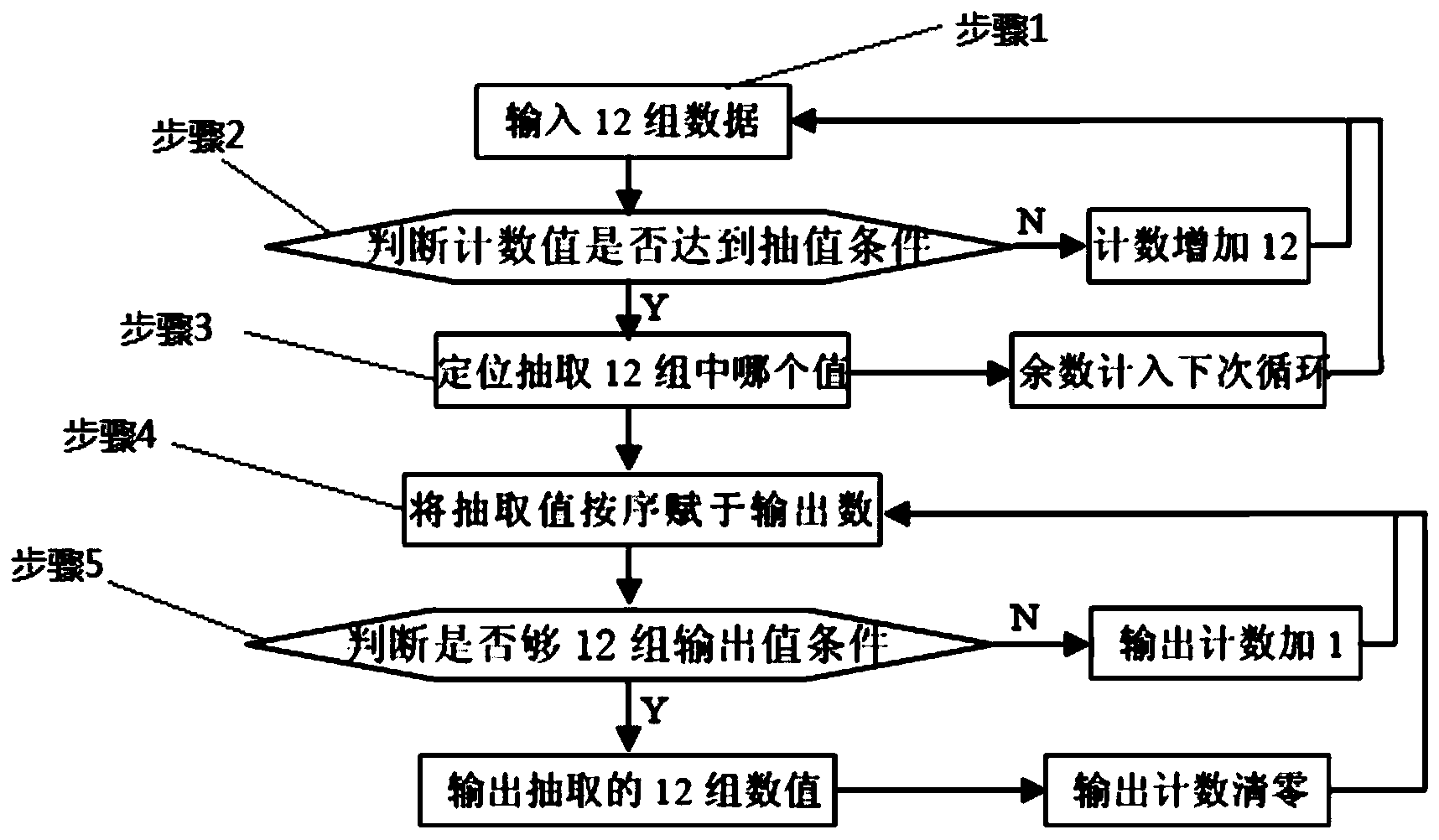

[0086] On the basis of above-mentioned embodiment, further as Figure 1 to Figure 2 As shown, a high-speed data extraction method based on an FPGA-based input and output sequence arrangement, including the following steps:

[0087] Step 1: Input 12 sets of data; judge whether the extraction ratio is less than 12, if yes, go to step 6, otherwise go to step 2;

[0088] Step 2: Determine whether the count value meets the pumping condition, if yes, go to step 3, otherwise, return to step 1 after counting up by 12;

[0089] Step 3: Position and extract one of the 12 sets of data in step 1 as the extracted value, enter step 4, count the remainder into the next cycle and return to step 1;

[0090] Step 4: assign the extracted value to the output number in sequence; go to step 5;

[0091] Step 5: Judging whether the 12 sets of data output conditions are met, if yes, output the value of the 12 sets of data extracted, and after the output count is cleared, return to step 4; otherwise,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More