Clock Data Recovery Circuit

A clock data recovery and clock recovery technology, applied in electrical components, digital transmission systems, transmission systems, etc., can solve the problems of large delay in the clock data recovery circuit system, low tolerance of the frequency difference between the transmitter and receiver, etc. System delay, improved inherent noise, effect of high transmission rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. Obviously, the described embodiments are only some embodiments of the present invention, rather than all embodiments . Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

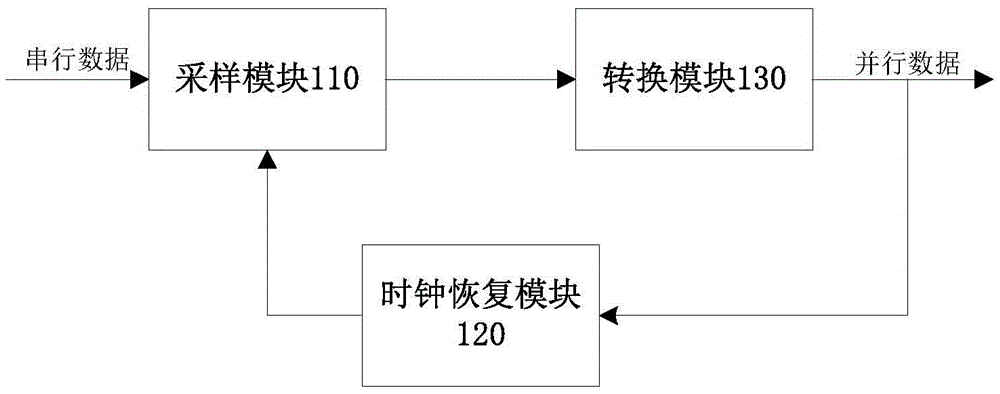

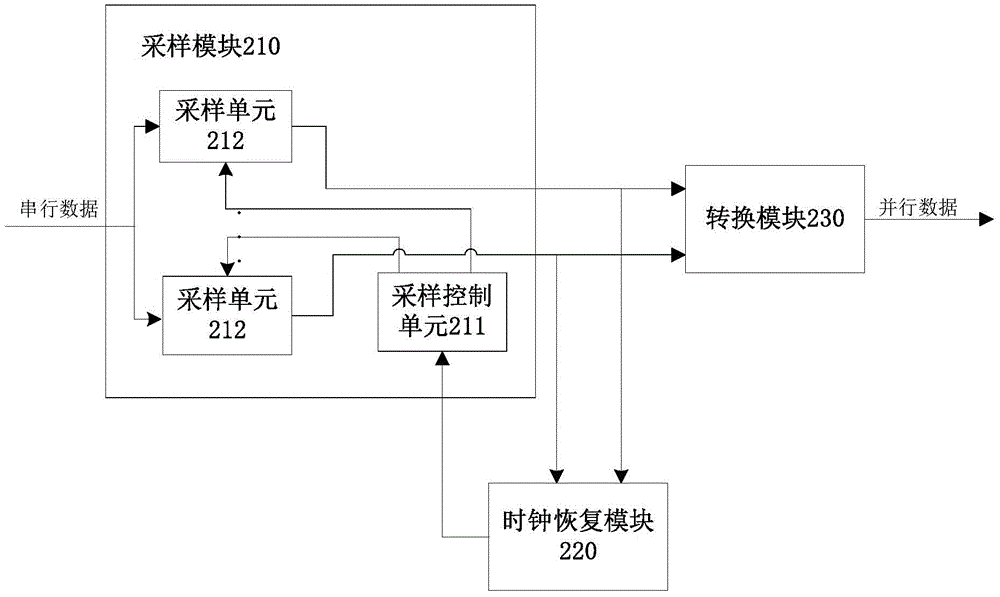

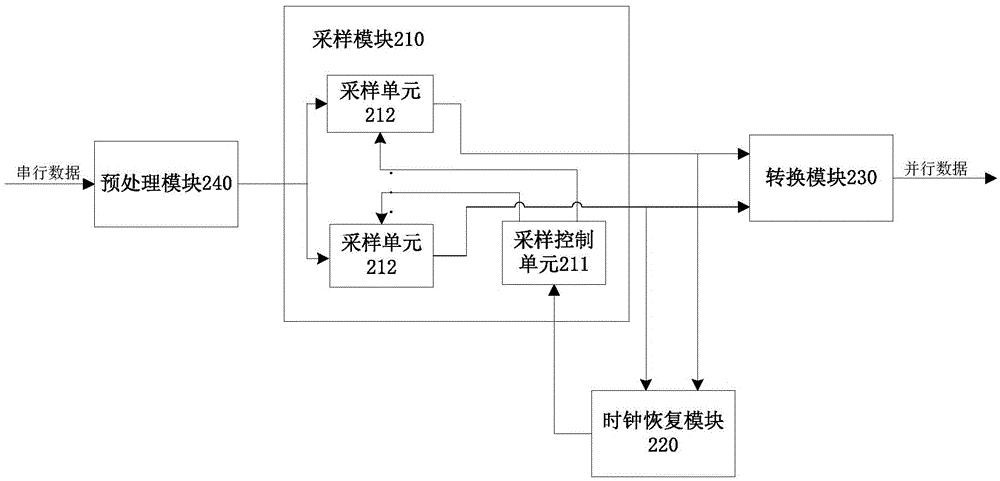

[0019] Below to figure 2 The clock data recovery circuit provided by the embodiment of the present invention will be described in detail as an example. Such as figure 2 As shown, it is a schematic structural diagram of a clock data recovery circuit provided by an embodiment of the present invention.

[0020] The clock data recovery circuit includes: a sampling module 210 , a clock recovery module 220 and a conversion module 230 .

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More