Process for manufacturing cavity of package substrate

A manufacturing process and a technology for packaging substrates, which are used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve the problems of difficult removal of solder resist ink, scratches on wire gold fingers, and low cavity yield rate, and improve the Process production efficiency, improve quality, and eliminate the effect of cumbersome operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other. The present invention will be further described in detail below in conjunction with the drawings and specific embodiments. This embodiment is based on Figure 7 The direction shown prevails.

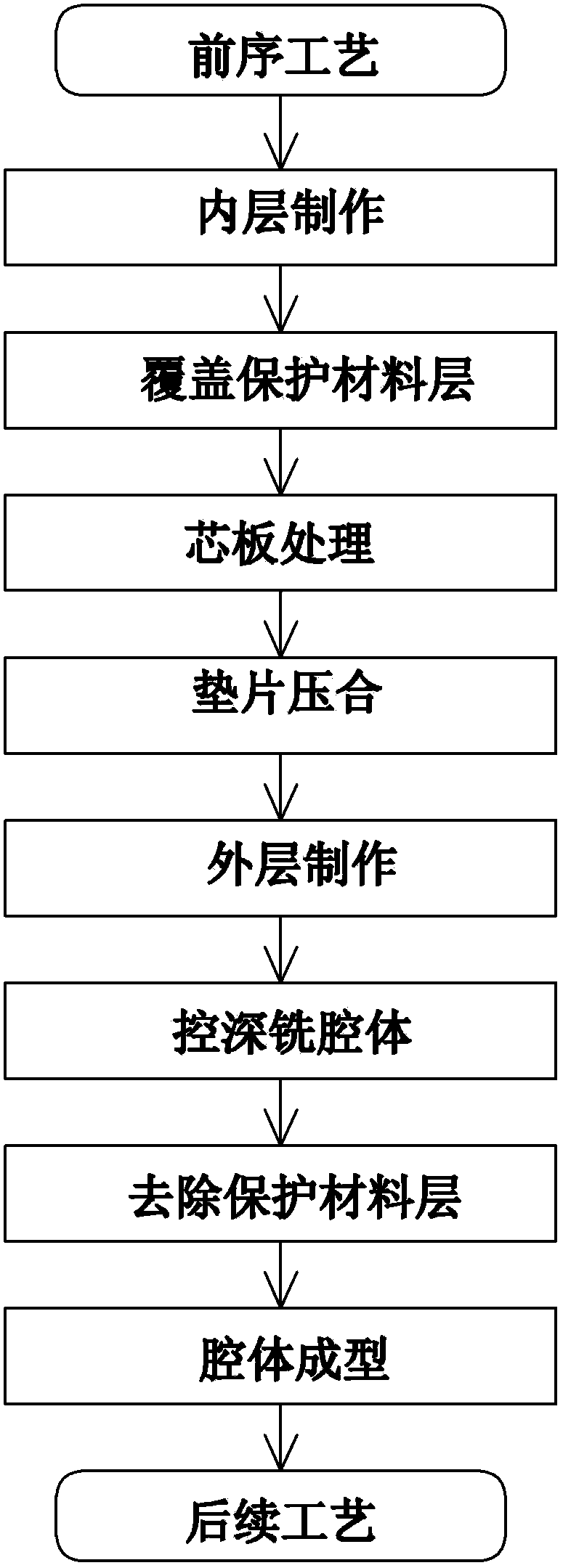

[0031] Such as Figure 1 to Figure 7 As shown, the embodiment of the present invention provides a manufacturing process of a packaging substrate cavity, including the following steps:

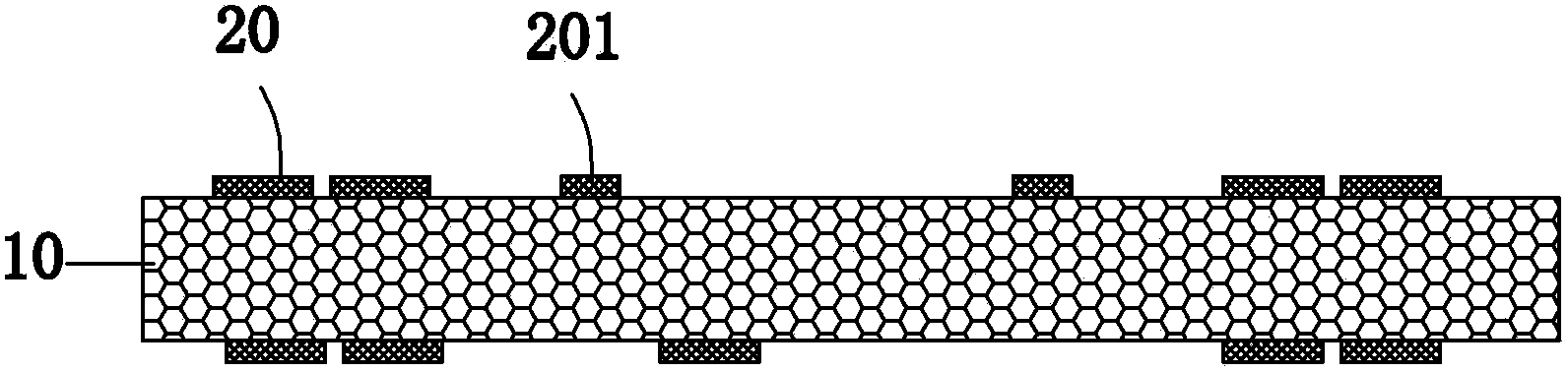

[0032] Making the inner layer: making the required circuit layer 20 on the core board 10;

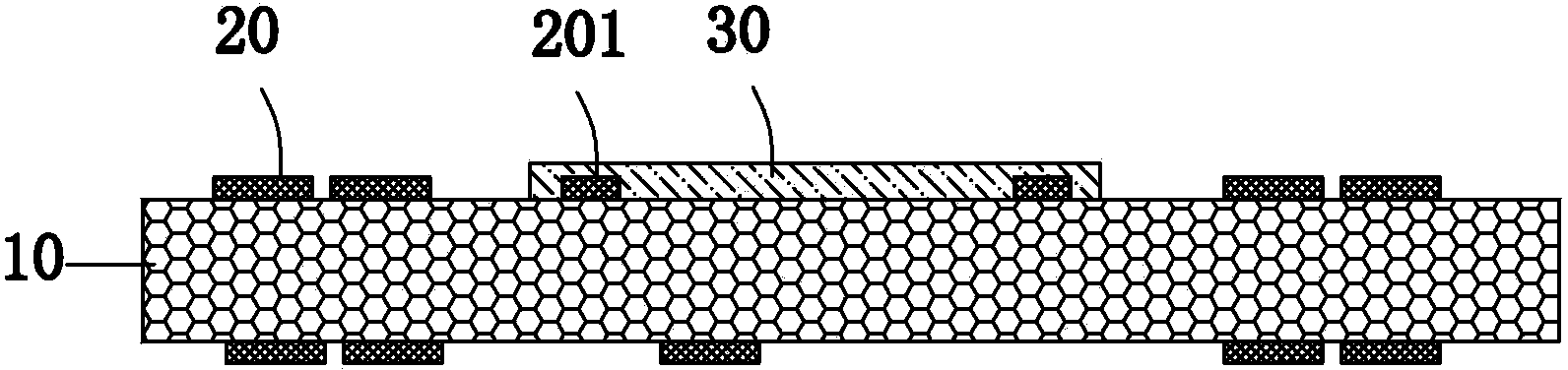

[0033] Covering the protective material layer: determine the target cavity area on the core board 10 after the inner layer is completed, and cover the protective material layer 30 above the wire bonding gold finger 201 in the target cavity area, so that the wire bonding gold finger 201 is covered by the protective material layer 30 full coverag...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com