Layered antenna checking method of integrated circuit layout graph verification

A technology of integrated circuits and inspection methods, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as reducing the yield in the production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

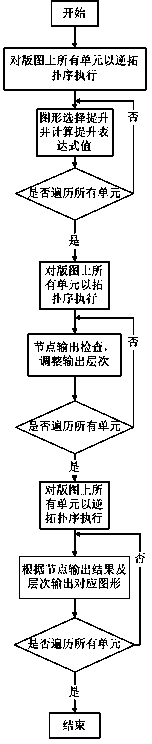

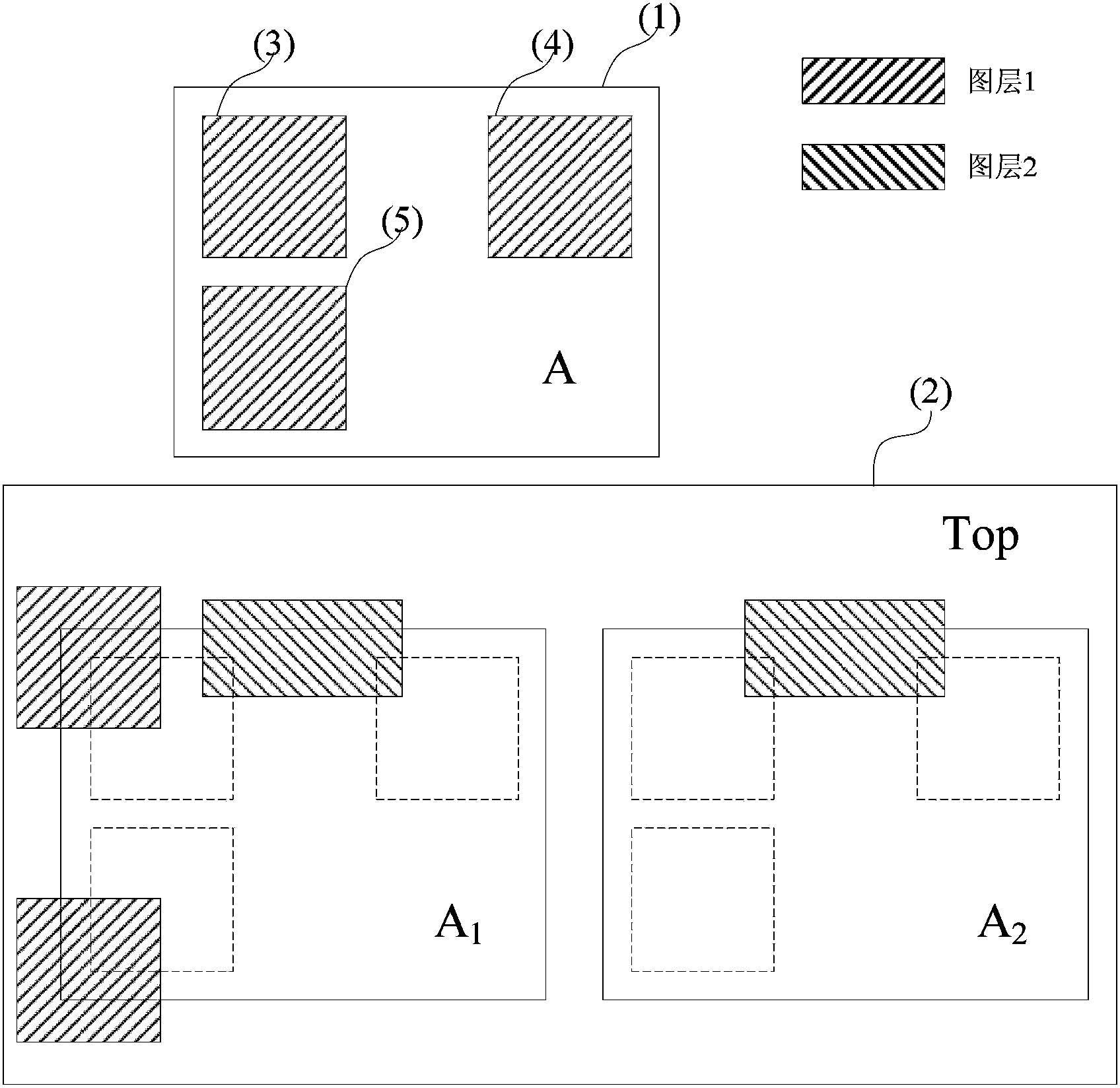

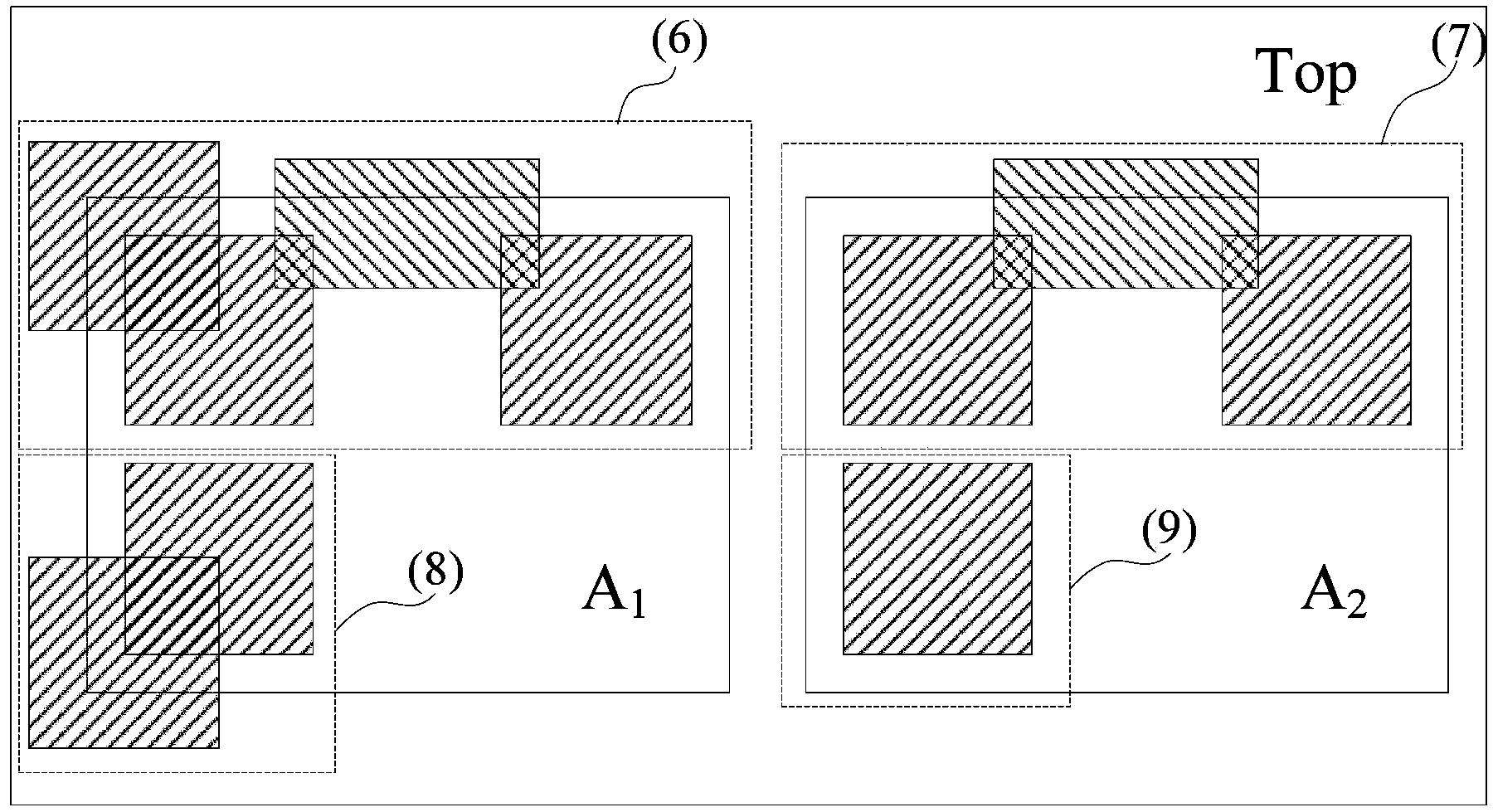

[0015] The processing flow of this method is as follows figure 1 shown. Introduce the concrete implementation of this method below in conjunction with example, Figure 2a Shown is the layout for the example, which contains the lower cell A ( Figure 2a (1)) and the top unit Top ( Figure 2a (2)), the graphics contained in the two units involve two layers, namely layer 1 and layer 2, and the node connection relationship has been established on layer 1 and layer 2. After the connection relationship is established, the nodes constituted as contained in unit A Figure 2a (3) (4) (5) Three nodes, the unit top contains Figure 2b (6) (7) (8) (9) four nodes. The graphic position relationship information is shown in the figure. All layer 1 graphics are specified as squares with an area of 100 units and a perimeter of 40 units. In this example, the node expression is set as "the node whose sum of the graphic area of layer 1 (denoted as area (layer 1)) is greater than 110 uni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More