Placement method of lithography alignment mark

A photolithographic alignment and marking technology, applied in the field of integrated circuit manufacturing, to achieve the effect of placing alignment marks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to have a more specific understanding of the technical content, characteristics and effects of the present invention, now in conjunction with the illustrated embodiment, the details are as follows:

[0017] The specific method of placing the photolithographic alignment mark in this embodiment is as follows:

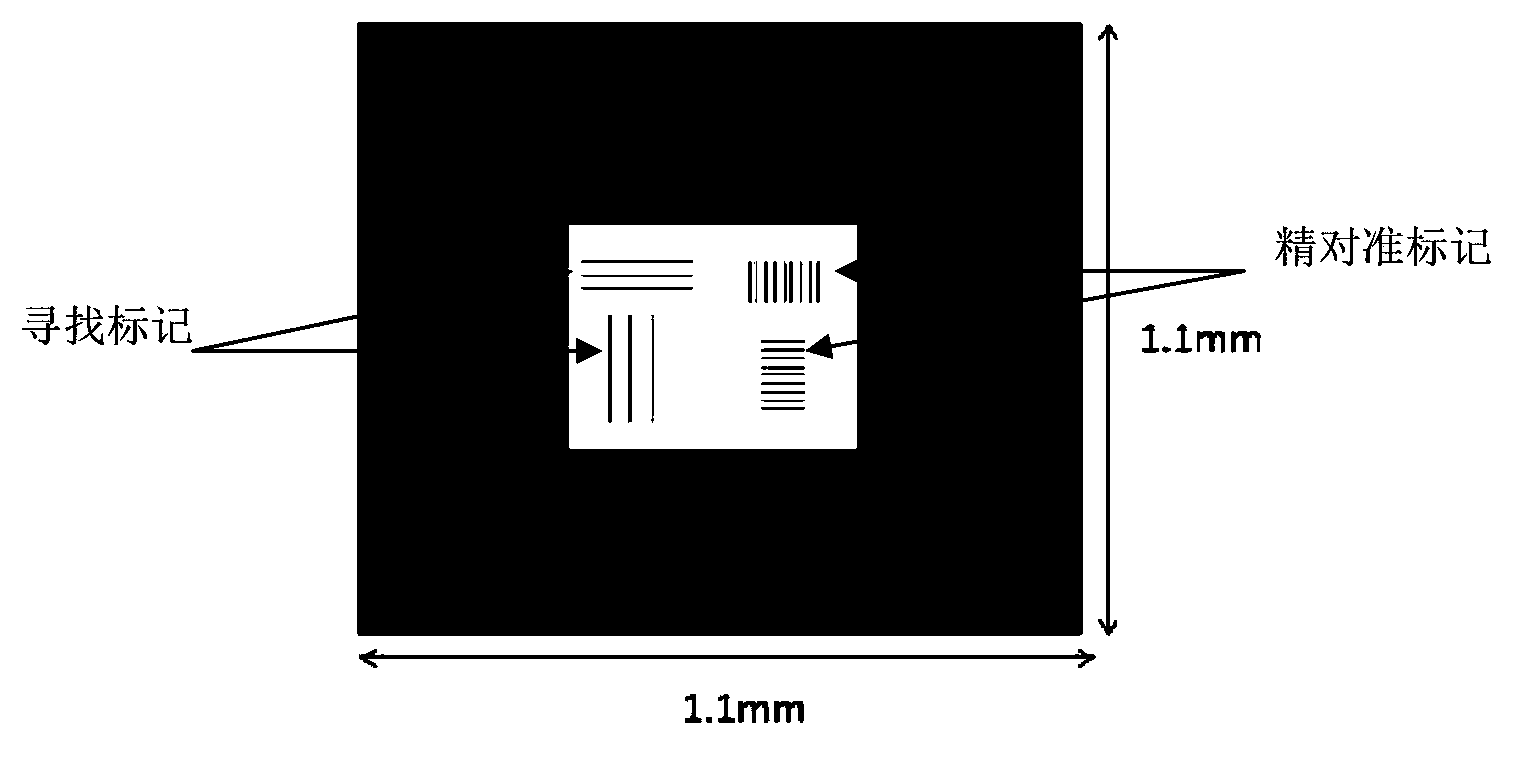

[0018] Step 1, first, integrate the search mark (search mark) and EGA mark (fine alignment mark) required for lithography in a space of 0.5mm×0.5mm on the mask to make an integrated pattern, plus 0.3mm chromium protection area, and make a photolithography plate together with the main pattern of the current layer, such as figure 2 shown. Calculate the coordinates of each photolithographic alignment mark relative to the center of the integrated pattern. For example, the coordinates of the search mark relative to the center of the integrated graphics are (Xs, Ys).

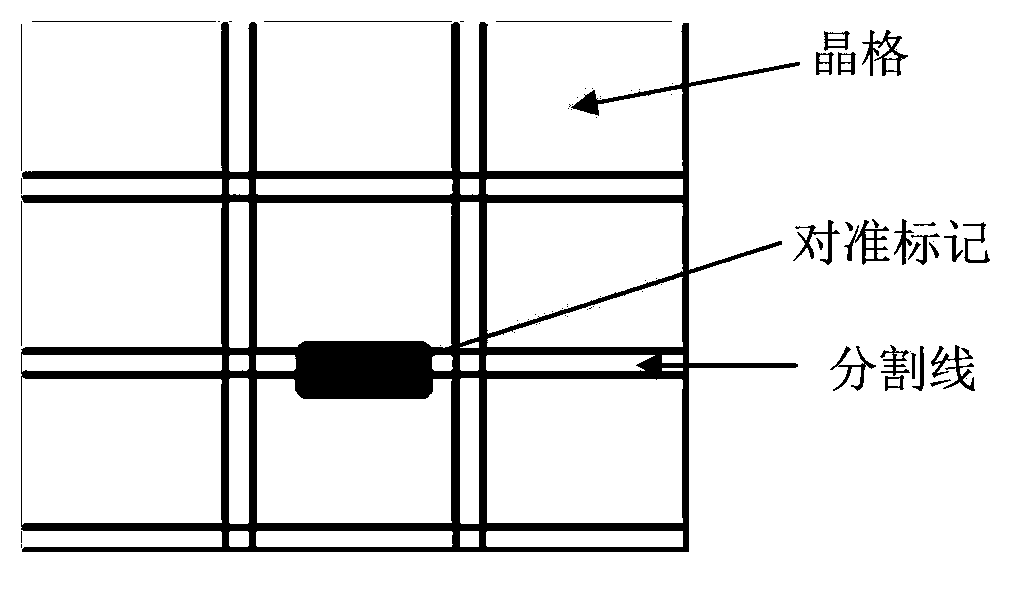

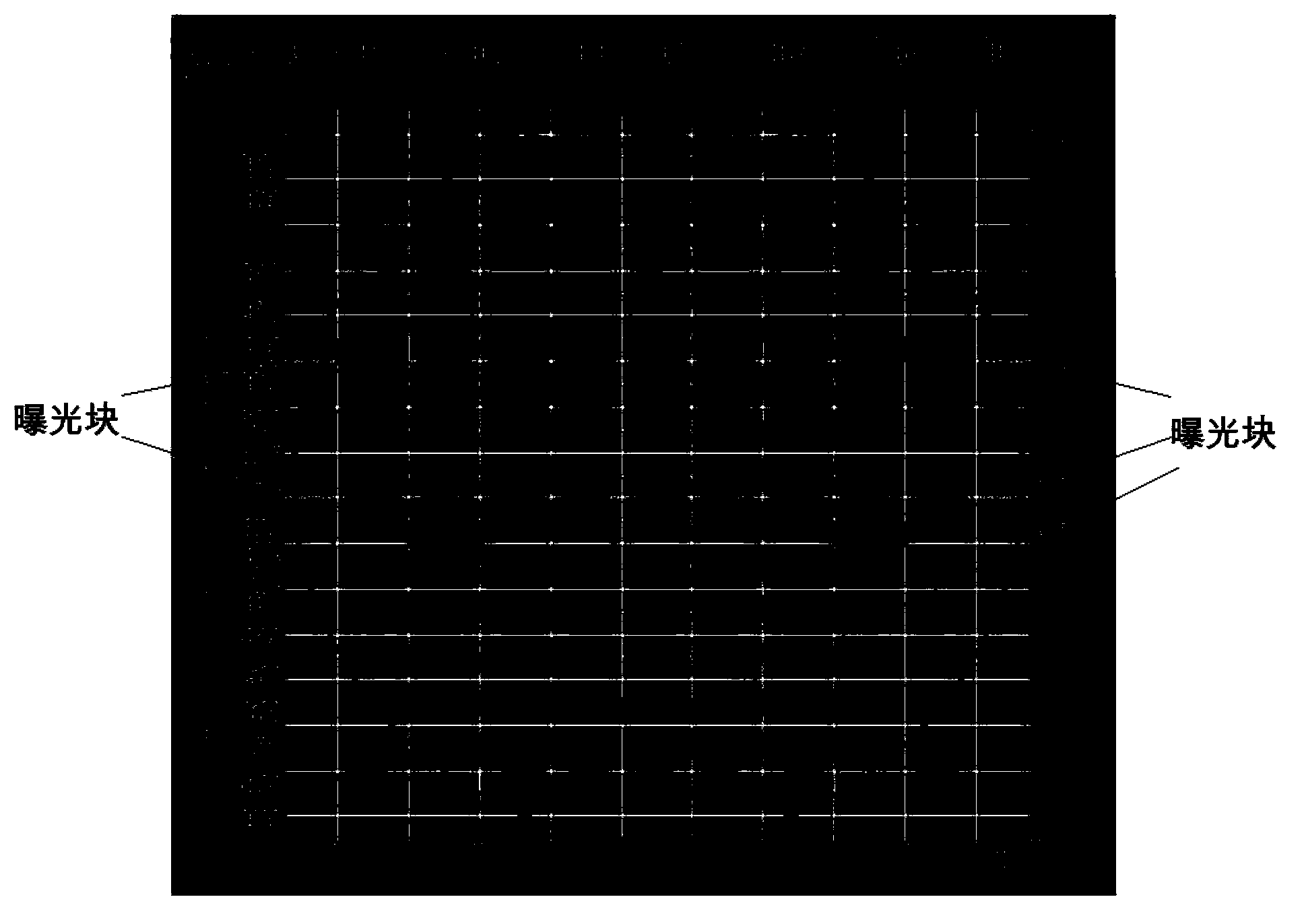

[0019] Step 2, according to the size of the lattice, select five special areas on the wafe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More