Multi-core processor soft error pressure test program generating system and method

A multi-core processor, stress testing technology, applied in the field of processors, which can solve problems such as architectural type restrictions, the use of a large number of different test programs, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

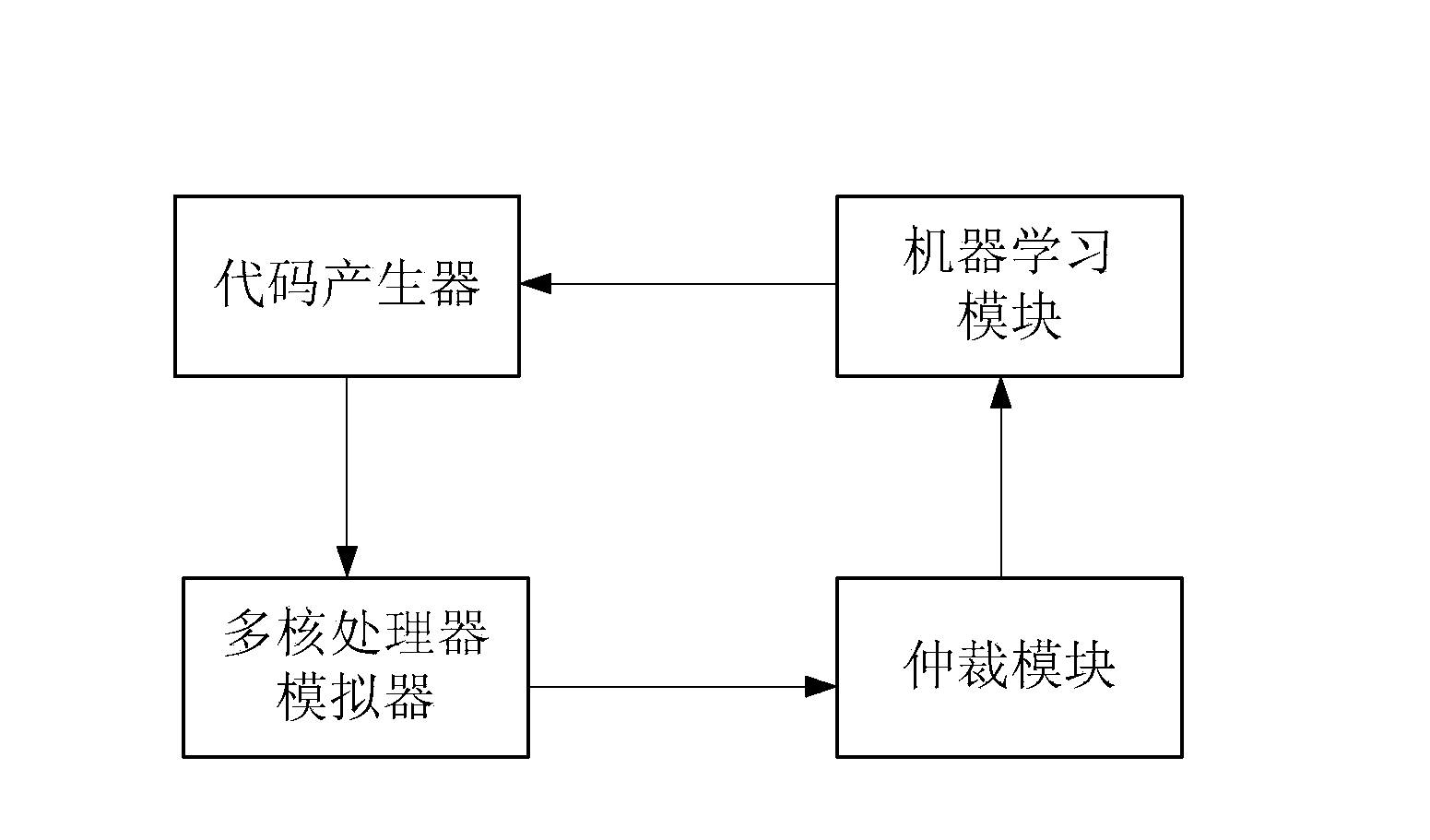

[0037] see figure 1 , is a schematic structural diagram of a system for generating a multi-core processor soft error stress test program according to an embodiment of the present invention. The multi-core processor soft error stress test program generating system according to the embodiment of the present invention includes a code generator, a multi-core processor simulator, an arbitration module and a machine learning module connected in sequence. Wherein, the connection includes a physical connection, an electrical connection, or a signal connection.

[0038] The code generator generates the AV...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More