Pump capacitor multiplexing circuit, charge pump, flash memory and pump capacitor multiplexing method

A flash memory and multiplexing circuit technology, applied in the direction of conversion equipment without intermediate conversion to AC, can solve the problems of unfavorable flash memory layout area design optimization, large space for pump capacitors, etc., to achieve layout area optimization and design optimization , The effect of facilitating the promotion and application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

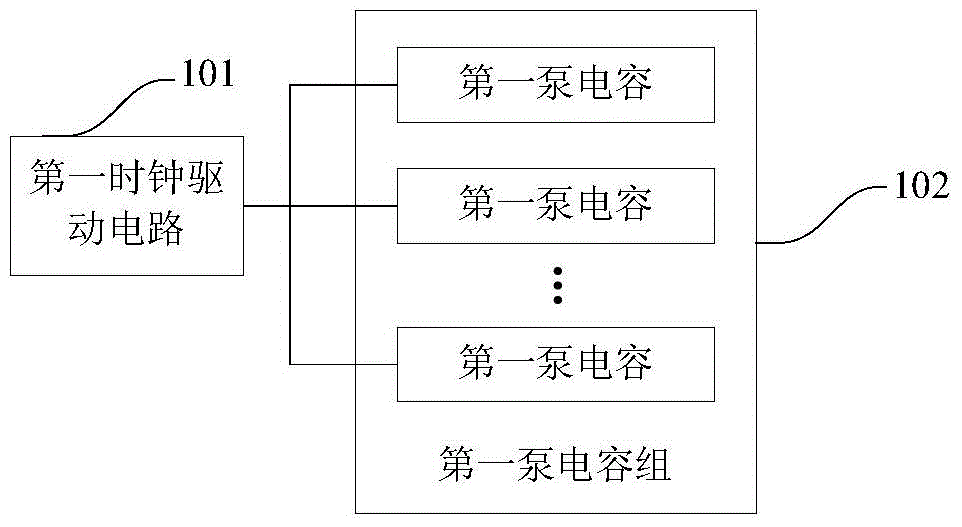

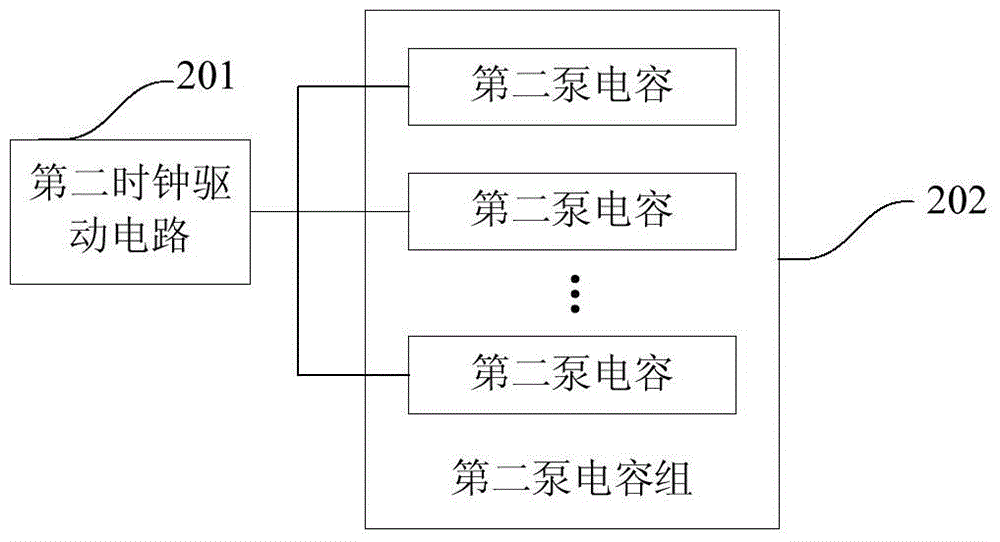

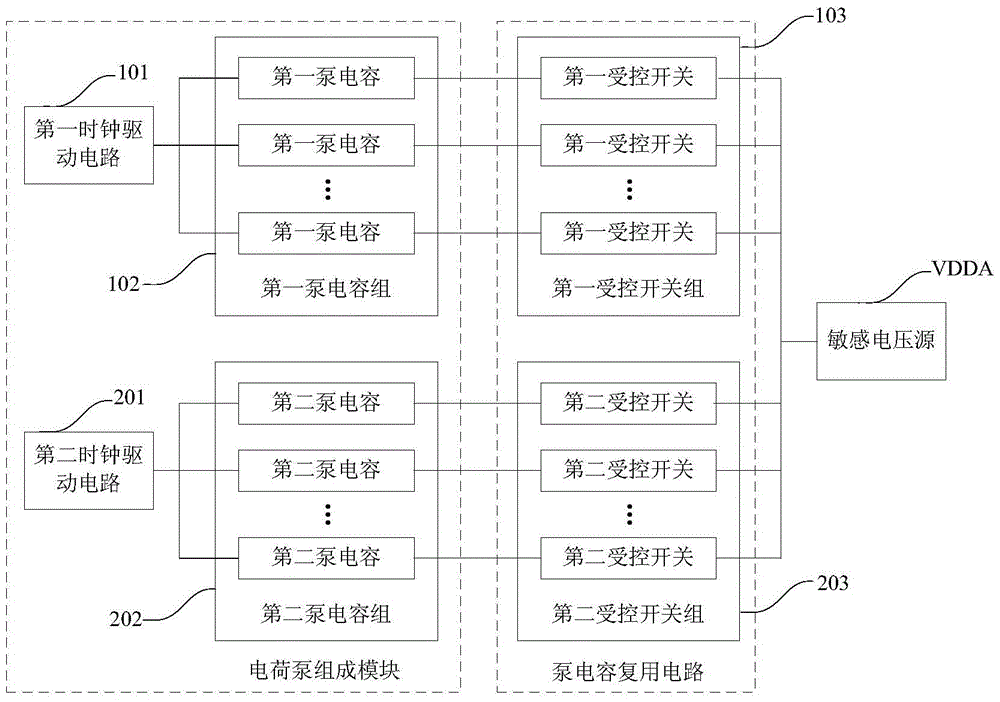

[0052] see figure 2 , Embodiment 1 of the present invention discloses a pump capacitor multiplexing circuit, which is applied to a flash memory to realize design optimization of the layout area of the flash memory; specifically, the pump capacitor multiplexing circuit includes:

[0053] The first controlled switch group 103, the second controlled switch group 203 and the control circuit (not shown in the figure);

[0054] Wherein, the first controlled switch group 103 includes first controlled switches whose number is equal to the number of the first pump capacitors in the first pump capacitor combination 102; each of the first controlled switches is located in one of the first The connection point between the pump capacitor and the sensitive voltage source VDDA;

[0055] The second controlled switch group 203 includes second controlled switches equal to the number of the second pump capacitors in the second pump capacitor group 202; each of the second controlled switches ...

Embodiment 2

[0066] Based on Embodiment 1, Embodiment 2 of the present invention discloses yet another pump capacitor multiplexing circuit, which is applied to a flash memory to realize design optimization of the layout area of the flash memory. The pump capacitor multiplexing circuit includes:

[0067] a first controlled switch group, a second controlled switch group and a control circuit;

[0068] Among them, the first controlled switch group and the second controlled switch group described in the second embodiment are compared with the first controlled switch group 103 and the second controlled switch group 203 described in the first embodiment in terms of circuit connection relationship and structural composition. There is no difference in

[0069] The control circuit described in the second embodiment is used for

[0070] Acquiring the operating mode information of the flash memory, the first clock signal output by the first clock drive circuit, and the second clock signal output b...

Embodiment 3

[0076] Based on Embodiment 2, Embodiment 3 of the present invention discloses yet another pump capacitor multiplexing circuit, which is applied to a flash memory to realize design optimization of the layout area of the flash memory. See image 3 , the pump capacitor multiplexing circuit includes:

[0077] The first controlled switch group 103, the second controlled switch group 203 and the control circuit 300;

[0078] Wherein, each of the first controlled switches in the first controlled switch group 103 and each of the second controlled switches in the second controlled switch group 203 can use MOS transistors; the advantage is that the MOS transistors ( Also known as power MOSEEF) has many advantages such as high switching speed, high operating frequency, and good thermal stability;

[0079] There are various types and structures of the MOS tubes, and the most widely used NMOS tubes can be preferred in the third embodiment; the NMOS tubes have the working characteristics...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More