Array substrate, manufacturing method and display device

A technology of an array substrate and a manufacturing method, which is applied in the field of display devices, and can solve the problems of affecting the aperture ratio of the display device, reducing the display effect of the display device, and large non-pixel area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

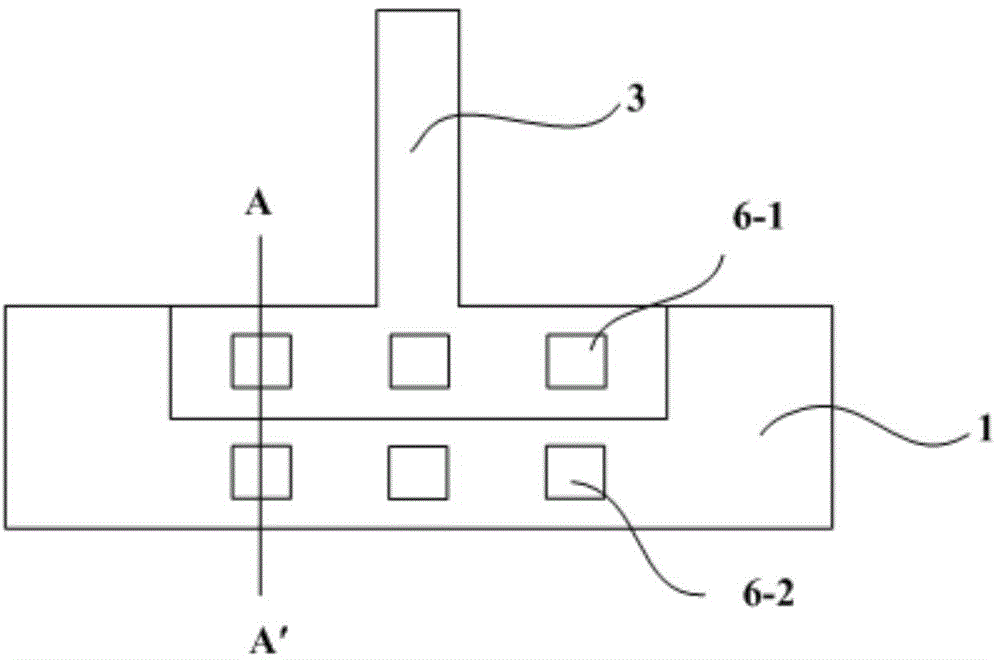

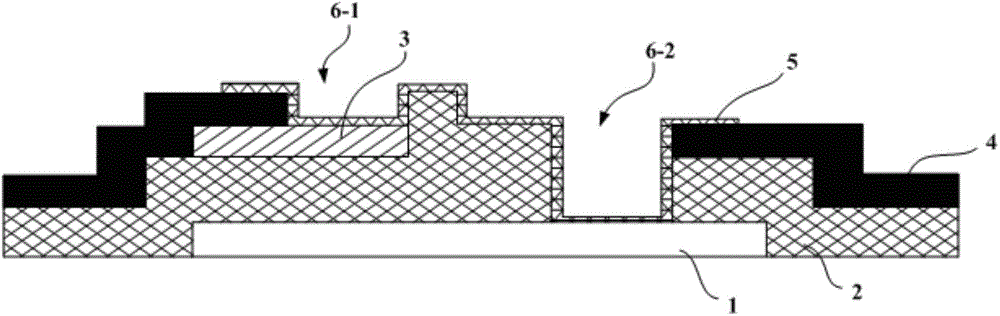

Embodiment 1

[0060] Step 1. Form the first gate lead 10 on the substrate; specifically, expose and develop the photoresist in the area other than the metal of the first gate lead 10 through a mask, and wet-etch the metal of the first gate lead 10 The metal other than is etched away, leaving the metal of the first gate lead 10;

[0061] Step 2, forming the insulating layer 40 of the first gate lead 10 on the first gate lead 10; directly deposited by plasma enhanced chemical vapor deposition;

[0062] Step 3: Expose and develop the photoresist in the area other than the metal of the second gate lead 30 through a mask, and etch away the metal other than the metal of the second gate lead 30 by wet etching, leaving the second gate lead 30 Metal;

[0063] Step 4, depositing and forming an insulating layer 40 on the first gate lead 10 by plasma-enhanced chemical vapor deposition;

[0064] Step 5: Expose and develop the photoresist at the position of the via hole 60 through a mask, and etch the ...

Embodiment 2

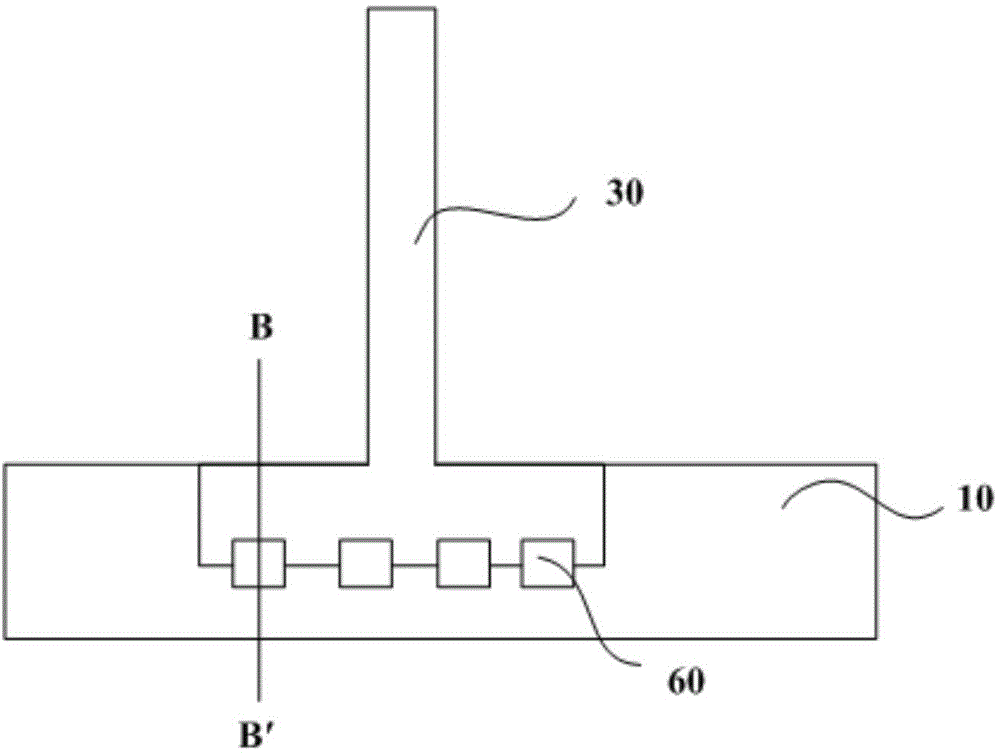

[0068] The array substrate is an array substrate with two transparent conductive layers, and its manufacturing method is as follows:

[0069] Step 1, such as Figure 9a As shown, the first gate lead 10 is formed on the substrate; specifically, the photoresist in the area other than the metal of the first gate lead 10 is exposed and developed through a mask, and the metal of the first gate lead 10 is wet-etched. The metal other than is etched away, leaving the metal of the first gate lead 10;

[0070] Step two, such as Figure 9b As shown, a gate insulating layer 20 is formed on the first gate lead 10; it is directly deposited by plasma enhanced chemical vapor deposition;

[0071] Step three, such as Figure 9c As shown, the photoresist in the area other than the metal of the second gate lead 30 is exposed and developed through a mask, and the metal other than the metal of the second gate lead 30 is etched away by wet etching, leaving the second gate lead 30 Metal;

[0072...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More