Obstacle bypassing wiring method based on optimization of shortest wire length in large-sized integrated circuit design

A large-scale integrated circuit and wiring method technology, which is applied in computing, electrical digital data processing, special data processing applications, etc., can solve the problems of increasing the number of pins and increasing the difficulty of wiring, and achieves effective wiring methods with short wire lengths. , the best effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0033] The specific description of the wiring problem in the embodiment of the present invention is as follows:

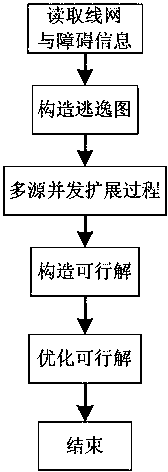

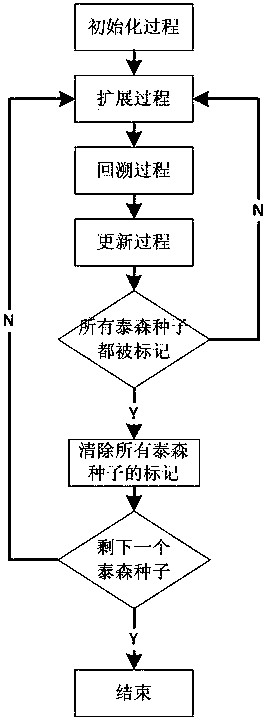

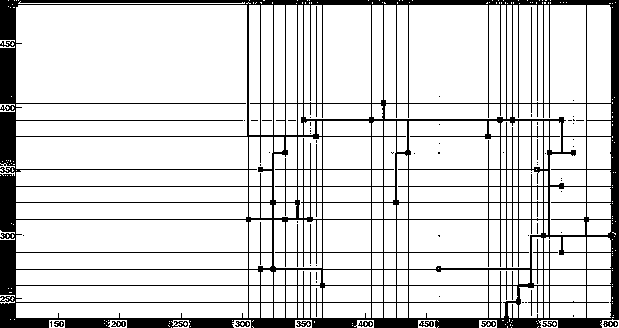

[0034]Given the wire mesh information and obstacle information, the given wire mesh information includes the two-dimensional coordinate information of each wire mesh pin on the plane, and the given obstacle information includes the four corners of each rectangular obstacle (4 vertex) on the two-dimensional coordinate information on the plane; the pin is required not to fall inside the obstacle, but can be on the boundary of the obstacle; it is required that two obstacles will not overlap each other, but can be adjacent on the boundary; the problem goal is , construct a Steiner tree composed of only horizontal and vertical lines without passing through any obstacles, and connect all the net pins to minimize the bus length.

[0035] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More