RS decoder low in hardware complexity

A technology of complexity and decoder, applied in the field of communication channel coding and decoding, which can solve the problems of consuming large hardware resources and computing speed, and cannot meet the requirements of low cost or high speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0084] The specific embodiment of the present invention is further described below in conjunction with accompanying drawing:

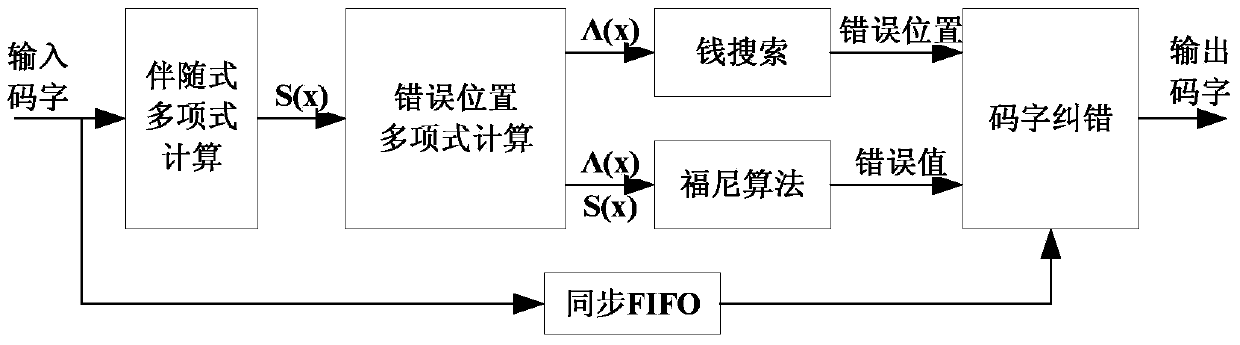

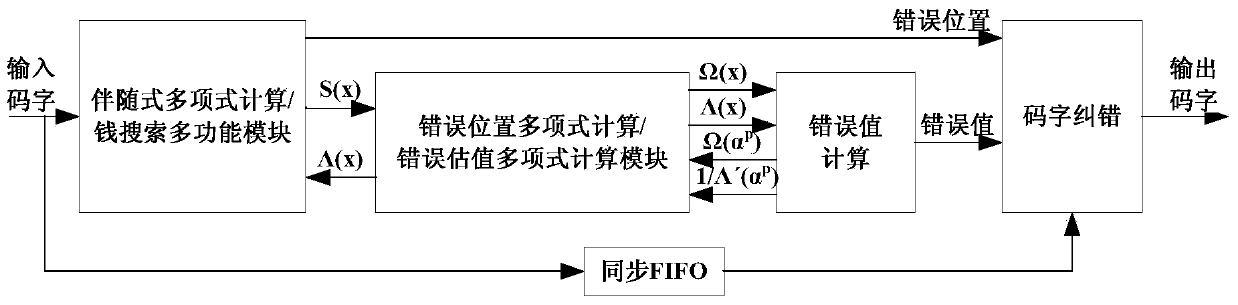

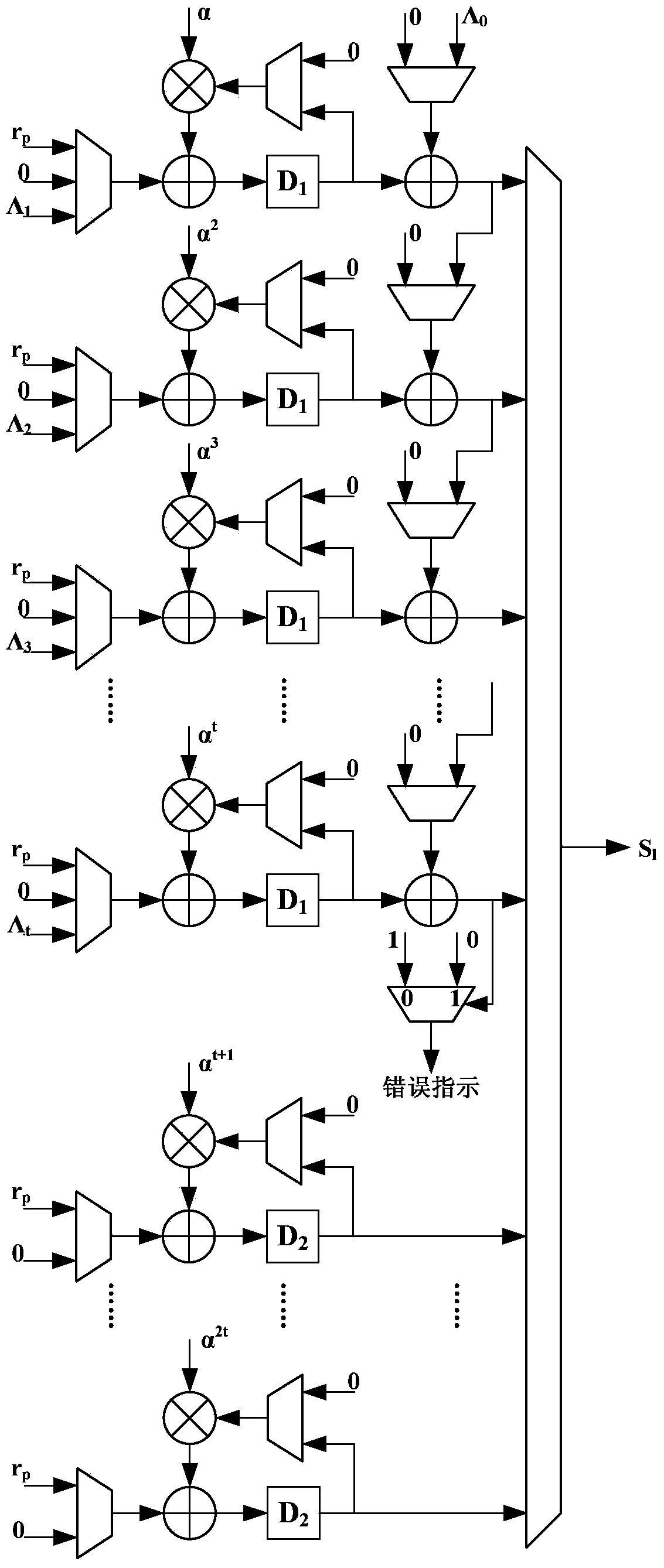

[0085] The structural block diagram of the RS decoder of the low hardware complexity described in the present invention is as figure 2 As shown, it includes a synchronous FIFO, an adjoint polynomial calculation / money search multifunctional module, an error position polynomial / error estimation polynomial calculation module, a Forney algorithm module and a codeword error correction module. Among them, the adjoint polynomial calculation / money search multifunctional module uses the same hardware to complete the calculation of adjoint polynomial coefficients and the function of money search through time-division multiplexing, which significantly saves hardware resources; In the value polynomial calculation module, the inversion operation is eliminated when the DiBM algorithm is used to iteratively solve the error position polynomial. Compared with the iBM ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More