Control method of outer layer deviation of circuit board

A control method and circuit board technology, applied in the fields of printed circuit manufacturing, printed circuit, electrical components, etc., can solve the difficult and fast outer layer alignment ability, not to mention the deviation model analysis, optimized alignment ability, positioning holes Damage and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Embodiments of the present invention are described in detail below:

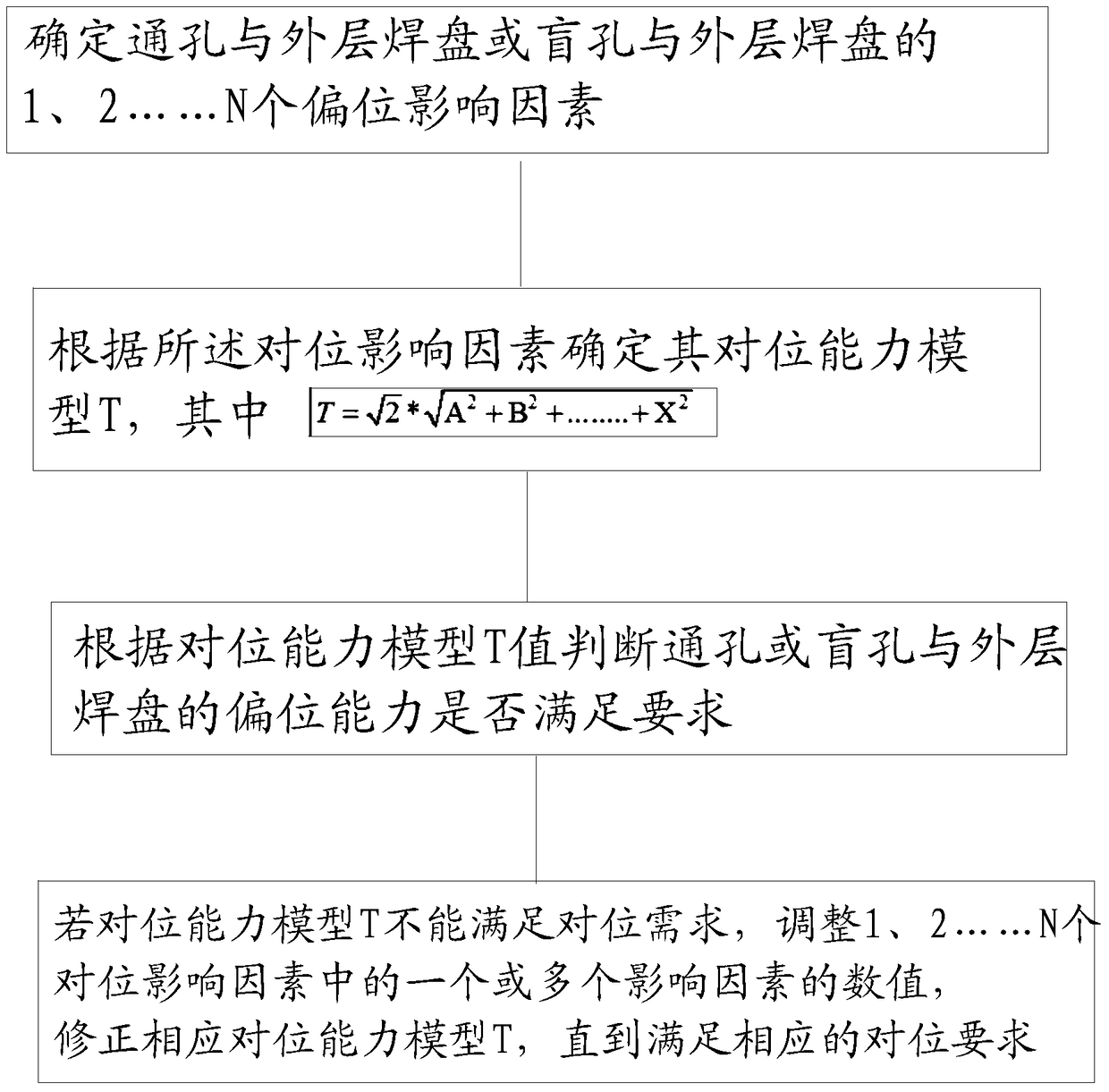

[0027] Determine the 1, 2...N offset influencing factors of through holes or blind holes and outer pads;

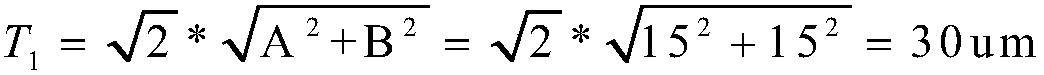

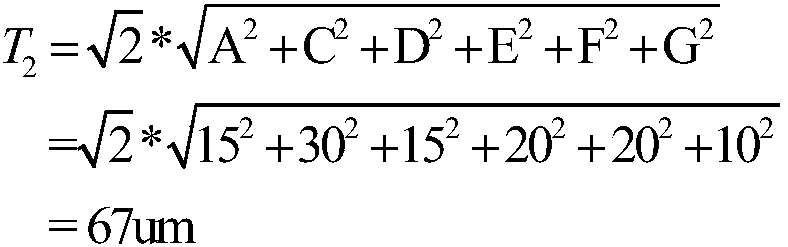

[0028] Determine its alignment capability model T according to the offset influencing factors, wherein 1, 2...N offset influence factors correspond to the influence values respectively A, B...X;

[0029] According to the T value of the alignment ability model, judge whether the offset ability of the through hole or blind hole and the outer pad meets the requirements;

[0030] If the alignment ability model T cannot meet the alignment requirements, adjust the values of one or more of the 1, 2...N offset influencing factors, and modify the corresponding alignment ability model T until the corresponding alignment requirements are met. .

[0031] Among them, N represents the unknown specific number of deviation influencing factors, and does not represent its specific number.

[0032] Taking ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More