CDM (Charged-Device-Model) electrostatic protection circuit

An electrostatic protection and circuit technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problem that gate oxide is easy to be broken down

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

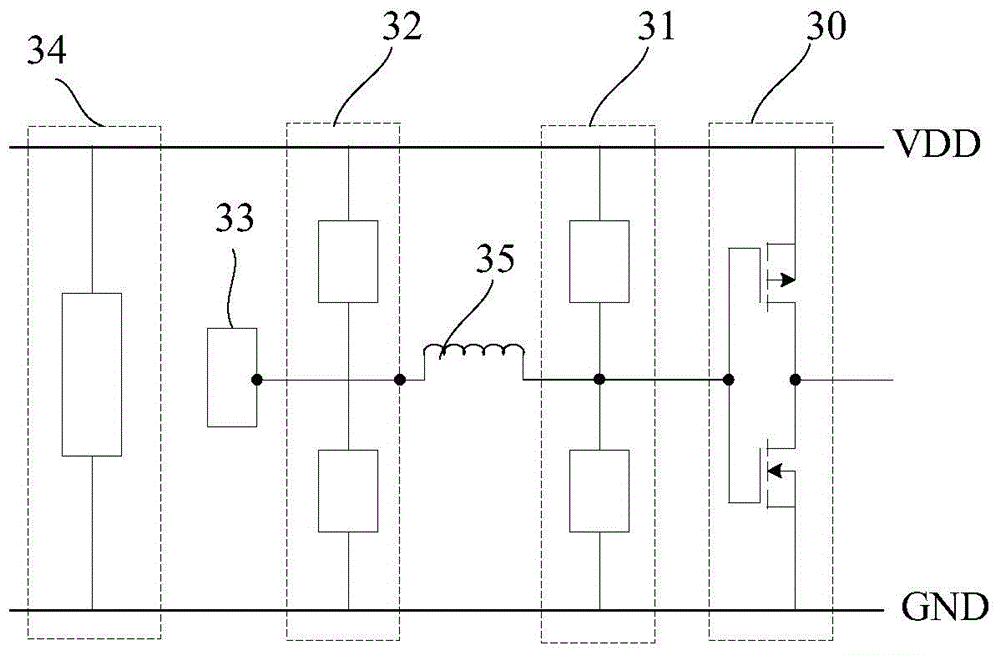

[0041] refer to Figure 4As shown, the functional unit 30 includes a PMOS transistor 301 and an NMOS transistor 302, the gate of the PMOS transistor 301 is connected to the gate of the NMOS transistor 302, and the drain of the PMOS transistor 301 is connected to the gate of the NMOS transistor 302. The drains are connected, and the gate of the PMOS transistor 301 is connected to the input / output pin 33 . The source of the PMOS transistor 301 is connected to VDD, and the source of the NMOS transistor 302 is connected to GND.

[0042] The second level protection unit 31 is GGMOS, the second level protection unit 31 includes a second PMOS transistor 311 and a second NMOS transistor 312, the drain of the second PMOS transistor 311 and the second NMOS transistor 312 The drain of the second PMOS transistor 311 is connected to VDD, the gate and source of the second NMOS transistor 312 are connected to GND.

[0043] The first level protection unit 32 is GCMOS, the first level protec...

no. 2 example

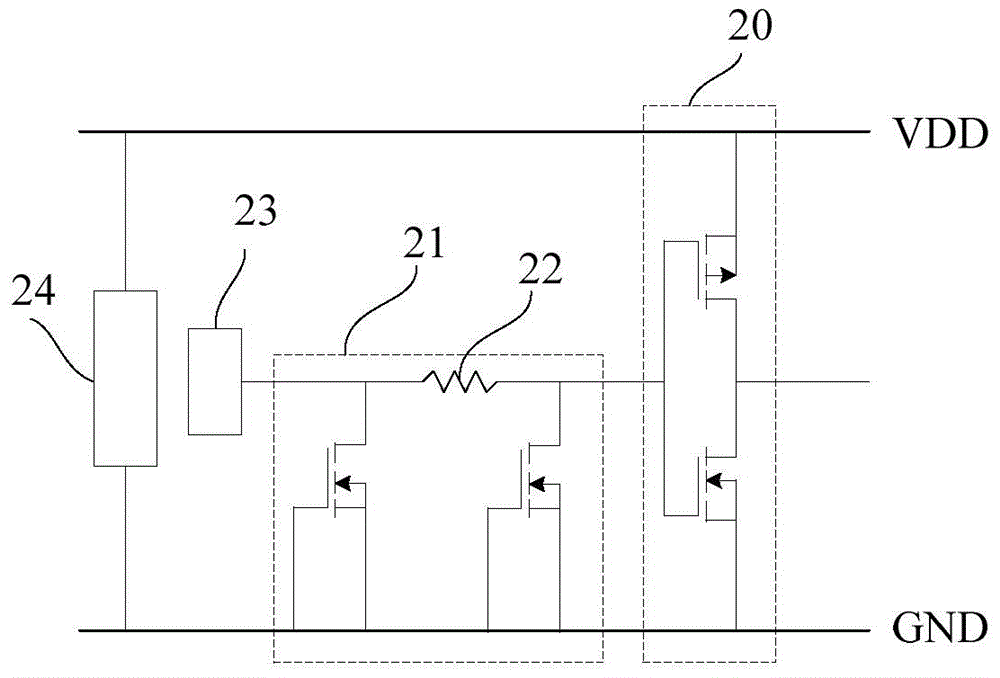

[0048] refer to Image 6 As shown, the second-level protection unit 41 and the first-level protection unit 42 adopt an open-source connection mode, the second-level protection unit 41 includes a second NMOS transistor, and the drain of the second NMOS transistor is connected to The input / output pin 43, the gate and the source of the second NMOS transistor are connected to GND. The first level protection unit 42 includes a first NMOS transistor, the drain of the first NMOS transistor is connected to the input / output pin 43 , and the gate and source of the first NMOS transistor are connected to GND. Similarly, an inductance coil 45 is connected in series between the second-level protection unit 41 and the first-level protection unit 42 . In this embodiment, the structures and connections of the functional unit 40 , the clamping circuit 44 , and the inductance coil 45 are the same as those in the first embodiment, and will not be repeated here.

[0049] In the same way, same as...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More