Multi-chip mixed packaging type semiconductor device and manufacturing method thereof

A hybrid packaging and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of increasing device thickness and ineffective heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

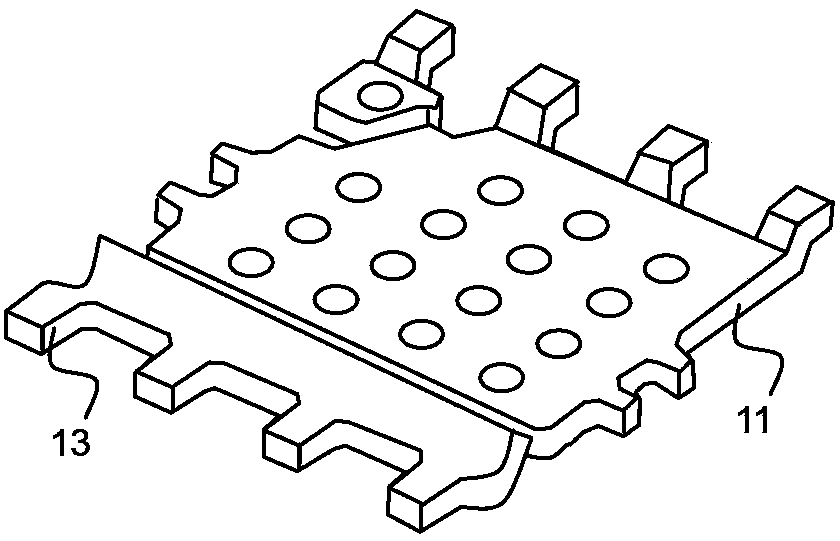

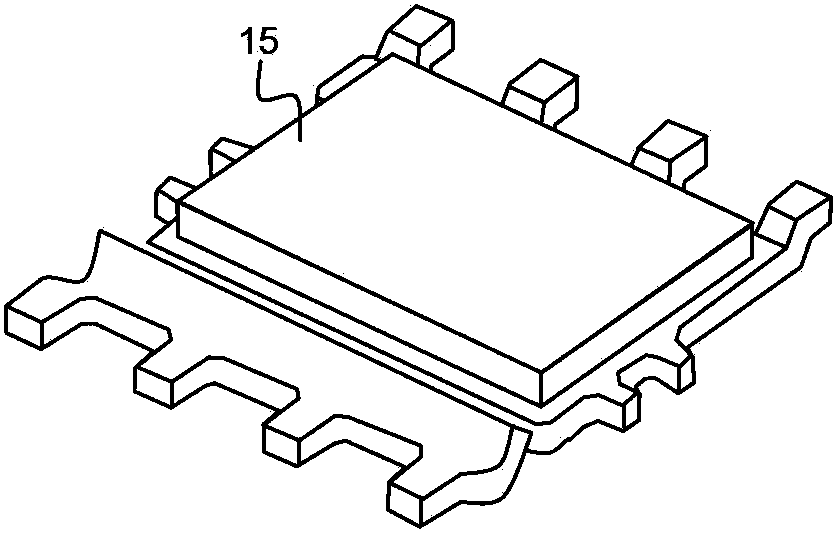

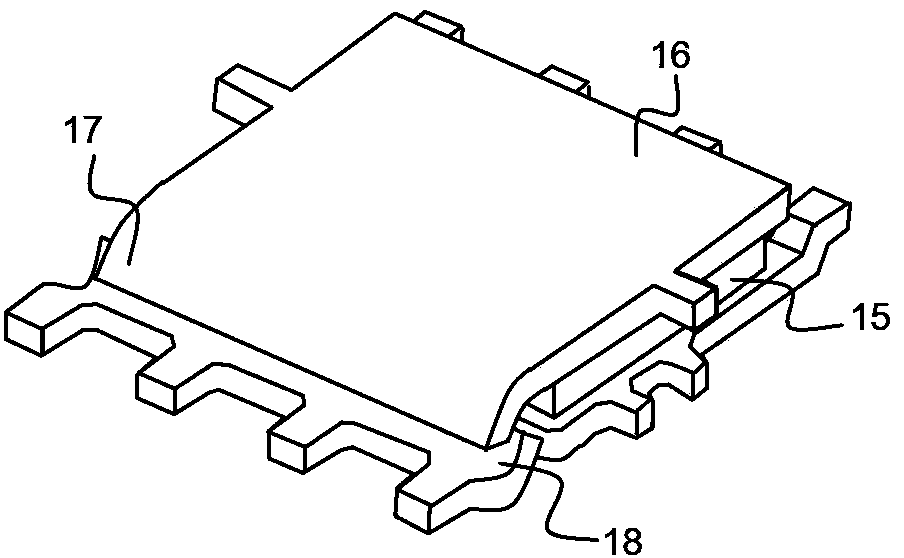

[0046] Such as Figure 3A , shows a structural schematic diagram of a chip mounting unit, usually each lead frame will contain a plurality of such units, for the sake of brief introduction, the present invention is only illustrated with one chip mounting unit. The chip mounting unit includes a first base 111, a second base 112, and first to fourth pins 101-104 that are separated from each other. The adjacent first bases 111 and second bases 112 are arranged side by side. They are roughly All are presented as square. For the convenience of description, in the plane where the chip mounting unit is located, the parallel extending direction of the first and second bases is defined as the longitudinal direction, and the separated extending direction is defined as the transverse direction. The first base 111 has a set of opposite first transverse edges 111a, second transverse edges 111b and another set of opposite first longitudinal edges 111c, second longitudinal edges 111d, and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com