FPGA-based time division multiplexing cascaded integrator-comb decimation filter and realization method thereof

A cascaded integral comb and decimation filter technology, which is applied in impedance networks, digital technology networks, electrical components, etc., can solve the problem of consuming FPGA resources, reduce hardware resource occupation, increase computing speed, and improve structural efficiency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

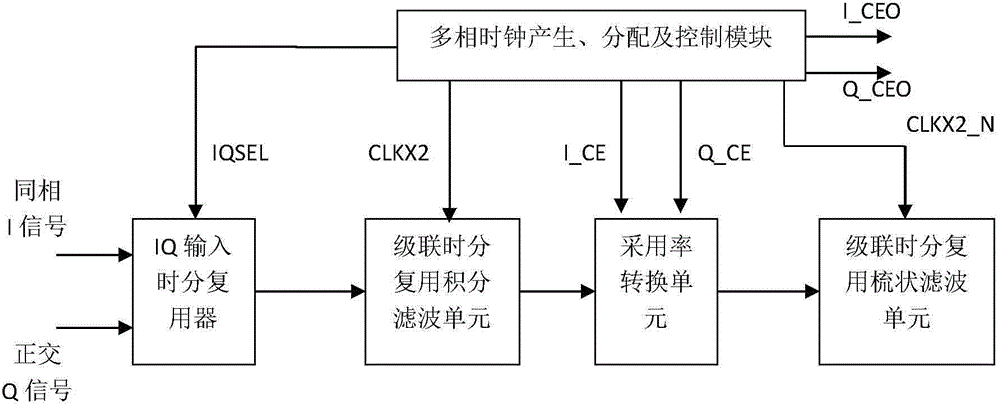

[0032] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

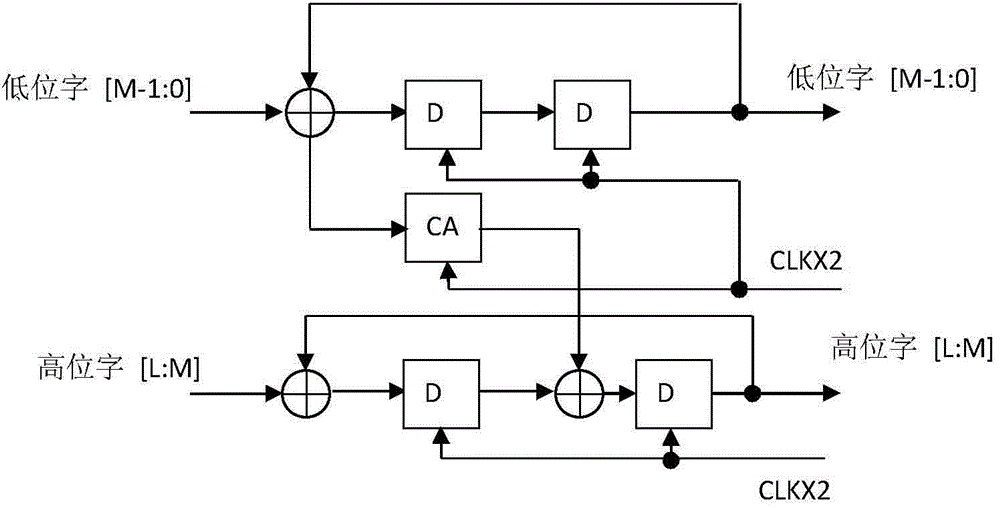

[0033] The present invention provides a method for realizing FPGA-based time-division multiplexing cascaded integral-comb decimation filtering, performing cascaded integral-comb filtering on the in-phase signal and the quadrature signal in a time-division multiplexing manner, specifically: the in-phase The signal and the orthogonal signal are time-division multiplexed and combined into one signal. After cascaded integral filtering, resampling is performed, and then filtered by a cascaded comb filter unit, and finally the output signal is demultiplexed into the processed synchronous The phase signal and the processed quadrature signal are two signals.

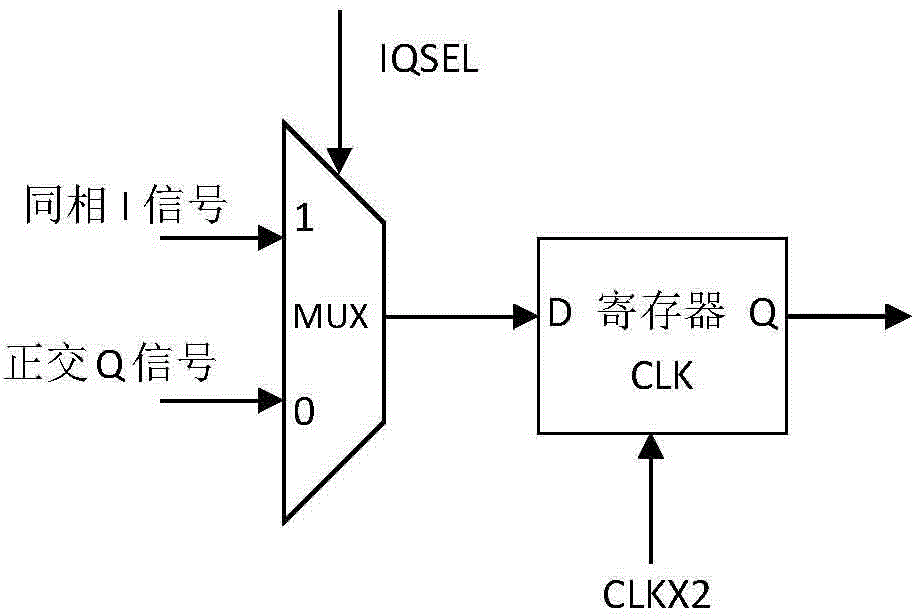

[0034] More specifically, the in-phase signal and the quadrature signal are alternately input into one input signal through a gate signal with the same frequency as the input signal sampling clo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More