Random number validation method for processor arithmetic logic unit instruction

A technology of arithmetic logic unit and verification method, which is applied in the field of random number verification of processor arithmetic logic unit instructions, and can solve the problems of low random pertinence, low error coverage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

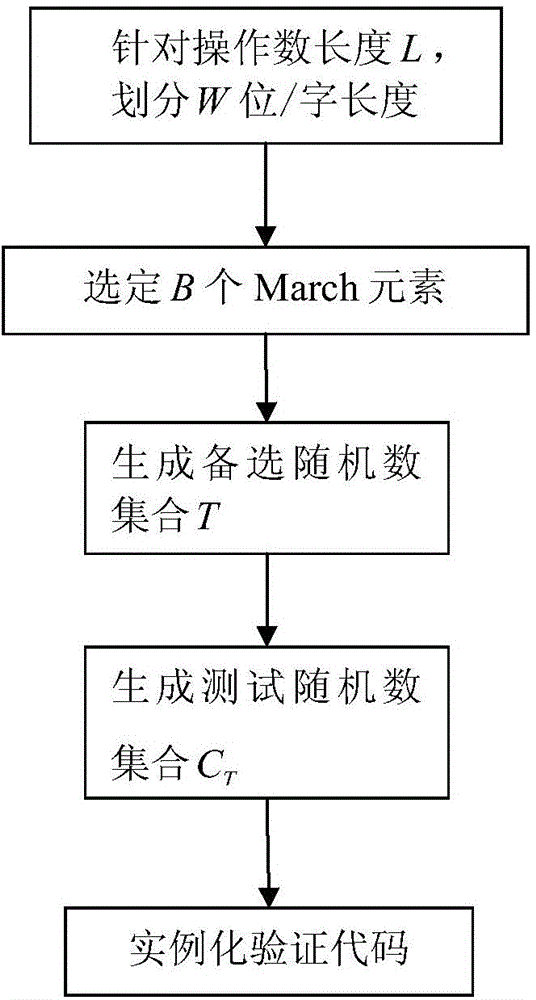

[0022] see figure 1 , the random number verification method of the present invention comprises:

[0023] Step 1, divide the W bit / word length of the operand storage unit according to the operation instruction operand length L and the test workload, and select the data background;

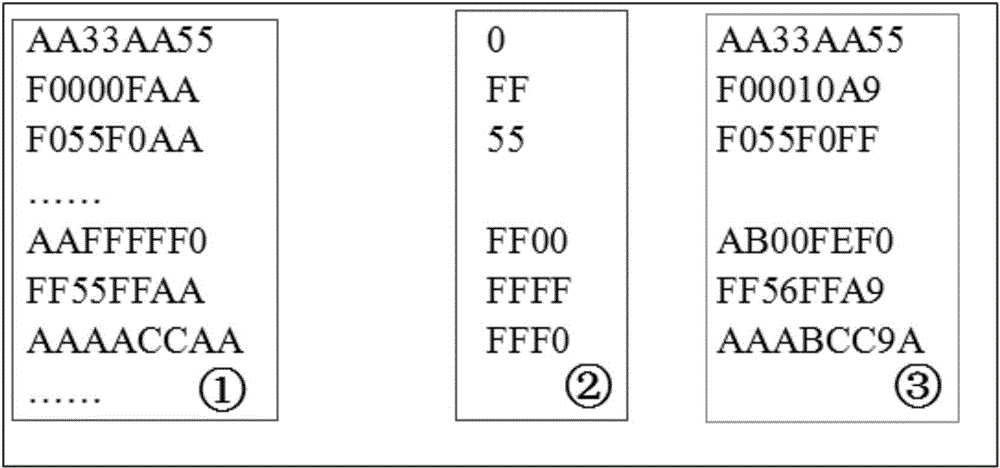

[0024] For W=2 n bit / word memory, take log 2 W+1 data background, if W≠2 n ,Pick Bit / word data background, and select the W bit in this group of data background;

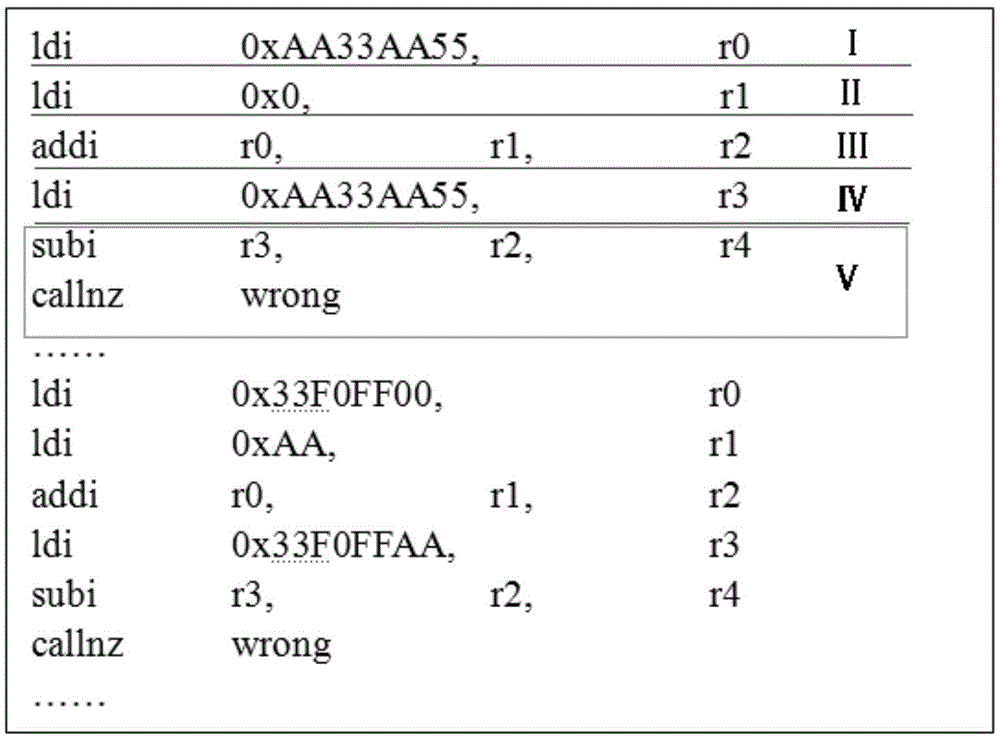

[0025] Step 2. According to the "word"-oriented March C-algorithm principle, the selected data background is reversed. The March algorithm repeatedly reads / writes 0 or 1 for each address, and according to the data background generation principle, selects The data background and its inverted data ensure that the test codes between each two bytes ap...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More