Distributive control and double-clock asynchronous sending and receiving module and FIFO (First In First Out) device

A distributed control and asynchronous transmission technology, applied in the directions of generating/distributing signals, data conversion, instruments, etc., can solve problems such as difficulty in delay control of clock tree signals, and achieve the effect of reducing complexity and balance overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Below in conjunction with specific embodiment, further illustrate the present invention. It should be understood that these examples are only used to illustrate the present invention and are not intended to limit the scope of the present invention. In addition, it should be understood that after reading the teachings of the present invention, those skilled in the art can make various changes or modifications to the present invention, and these equivalent forms also fall within the scope defined by the appended claims of the present application.

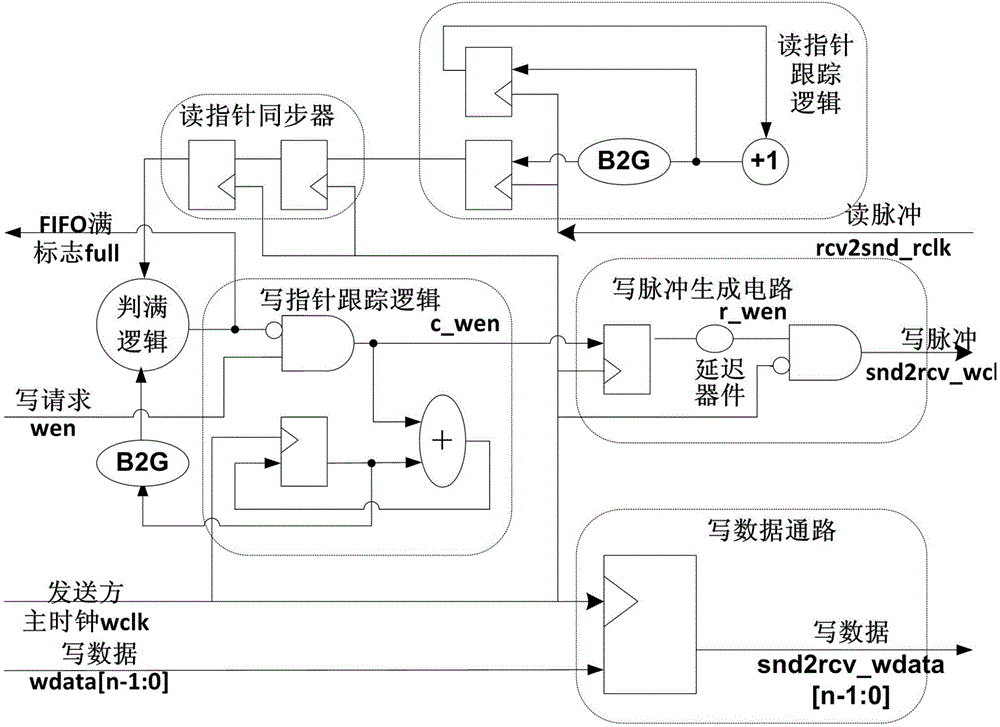

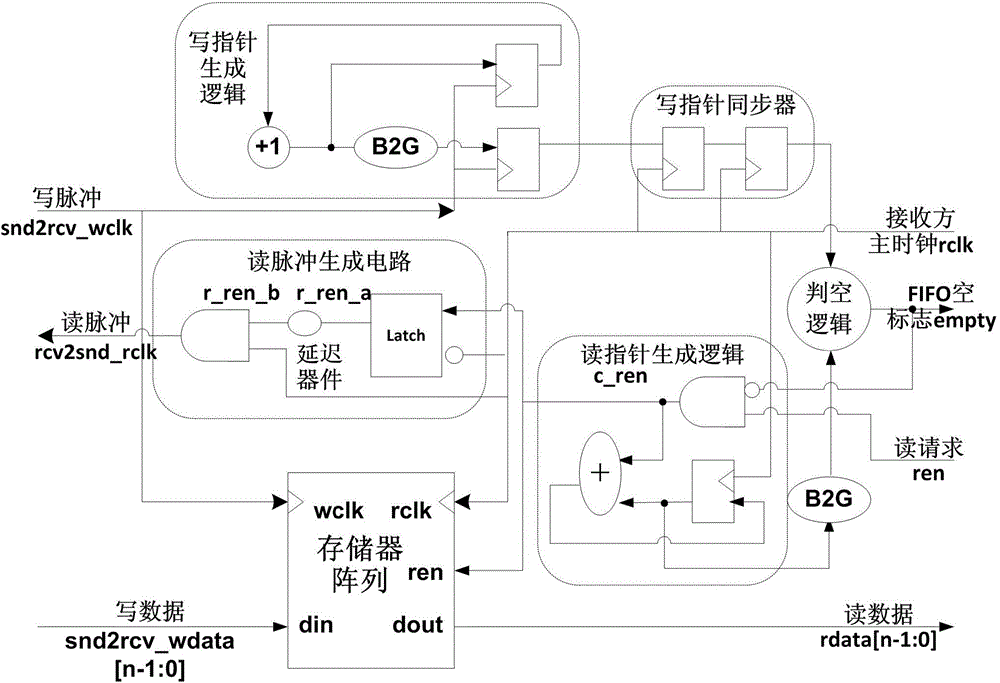

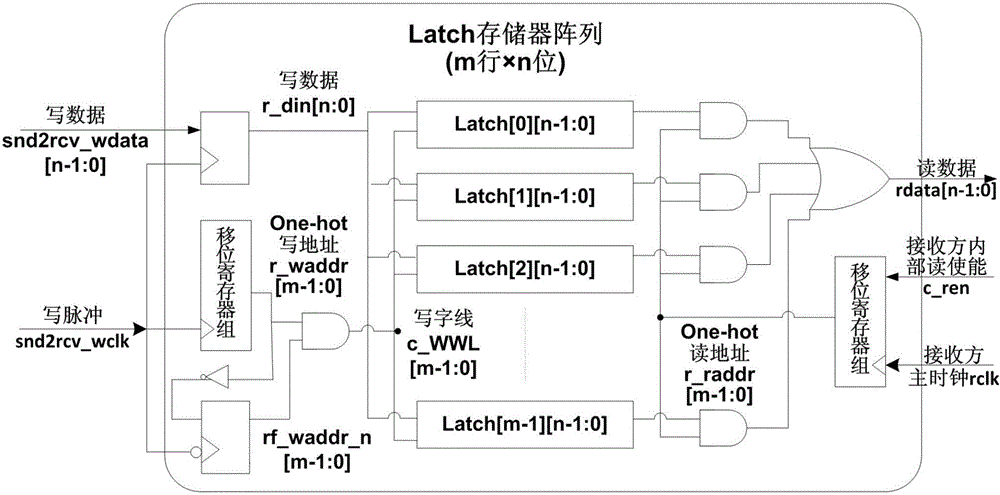

[0024] The first embodiment of the present invention relates to a distributed control dual-clock asynchronous sending module, such as figure 1 As shown, it includes a source synchronous signal generation logic circuit and a full flag generation logic circuit connected to each other, and the source synchronous signal generation logic circuit includes a write pulse generation circuit and a write data path, and the write pulse gen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More