JTAG signal generation method and generator

A signal generator and signal generation technology, applied in the direction of instruments, parts of electrical measuring instruments, measuring devices, etc., can solve problems such as error-prone and increase JTAG test workload, so as to reduce workload, improve efficiency, and improve appearance wrong effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

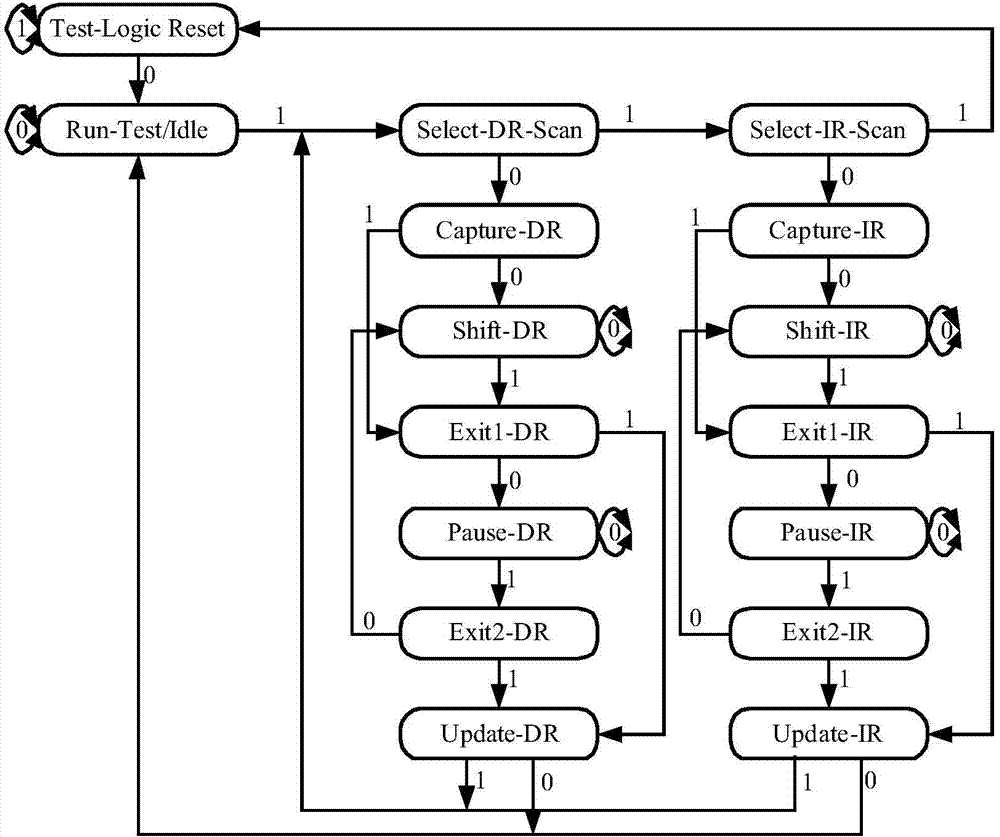

[0053] In order to enable those skilled in the art to better understand the technical solution of the present invention, a JTAG signal generation method and generator provided by an embodiment of the present invention will be described in detail below with reference to the accompanying drawings.

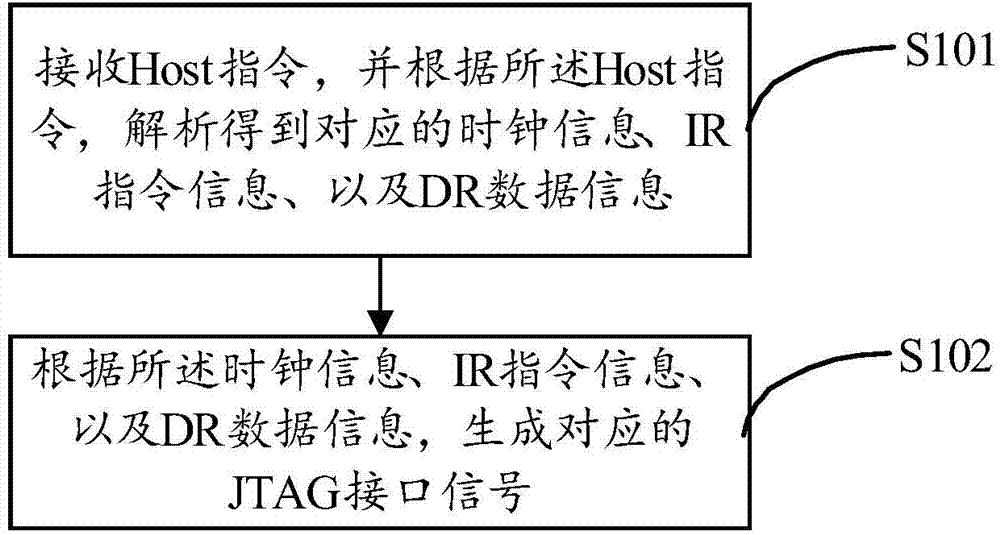

[0054] see figure 2 , a schematic flow chart of a method for generating a JTAG signal provided by an embodiment of the present invention, such as figure 2 As shown, the JTAG signal generation method that the embodiment of the present invention provides comprises:

[0055] Step S101, receiving a Host command, and analyzing and obtaining corresponding clock information, IR command information, and DR data information according to the Host command;

[0056] Step S102 , generating a corresponding JTAG driving signal according to the clock information, IR command information, and DR data information.

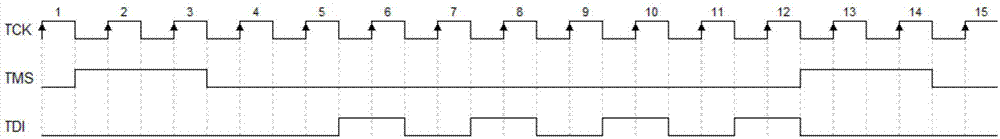

[0057] In the embodiment of the present invention, the Host instruction is a kind o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More