A duty ratio adjustment circuit

A technology for adjusting the circuit and duty cycle, which is applied in the direction of electrical components, electric pulse generation, pulse technology, etc., can solve the problem that the duty cycle of the output signal cannot be adjusted to 50%, and achieve the effect of simple structure and wide application range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solution of the present invention will be further described in detail below in conjunction with the accompanying drawings, but the protection scope of the present invention is not limited to the following description.

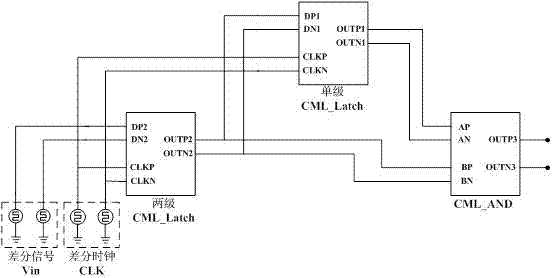

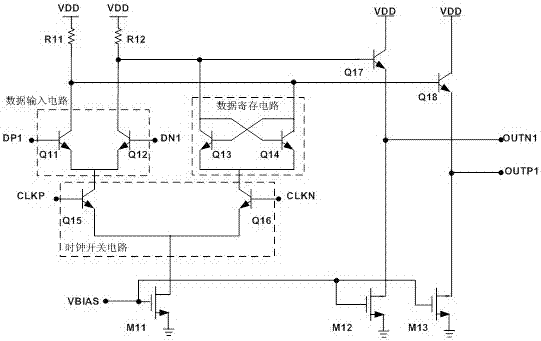

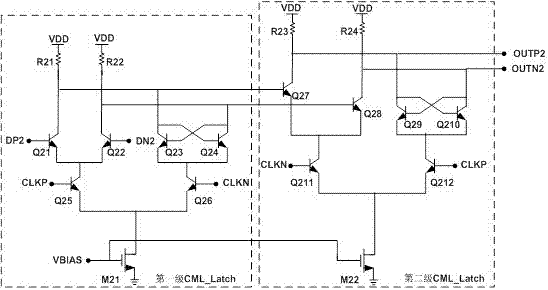

[0025] Such as figure 1 As shown, a duty cycle adjustment circuit, which includes a single-stage current-mode logic latch (single-stage CML_Latch), a two-stage current-mode logic latch (two-stage CML_Latch) and a current-mode logic AND gate (CML_AND), The differential clock CLK is respectively connected to the clock signal input terminals (CLKN and CLKP) of the single-stage current-mode logic latch (single-stage CML_Latch) and the two-stage current-mode logic latch (two-stage CML_Latch), and the differential clock CLK is input to Clock signal for the channel divider. The differential signal Vin is connected to the differential signal input terminals (DP2 and DN2) of the two-stage current mode logic latch (two-stage CML_Latch). The differen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More