A Pulse Width Adaptive Configurable Memory IP Structure

A self-adaptive, memory technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of unoptimized IP working pulse width, device performance impact, etc., to achieve fast read time, optimized device performance, low read The effect of power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

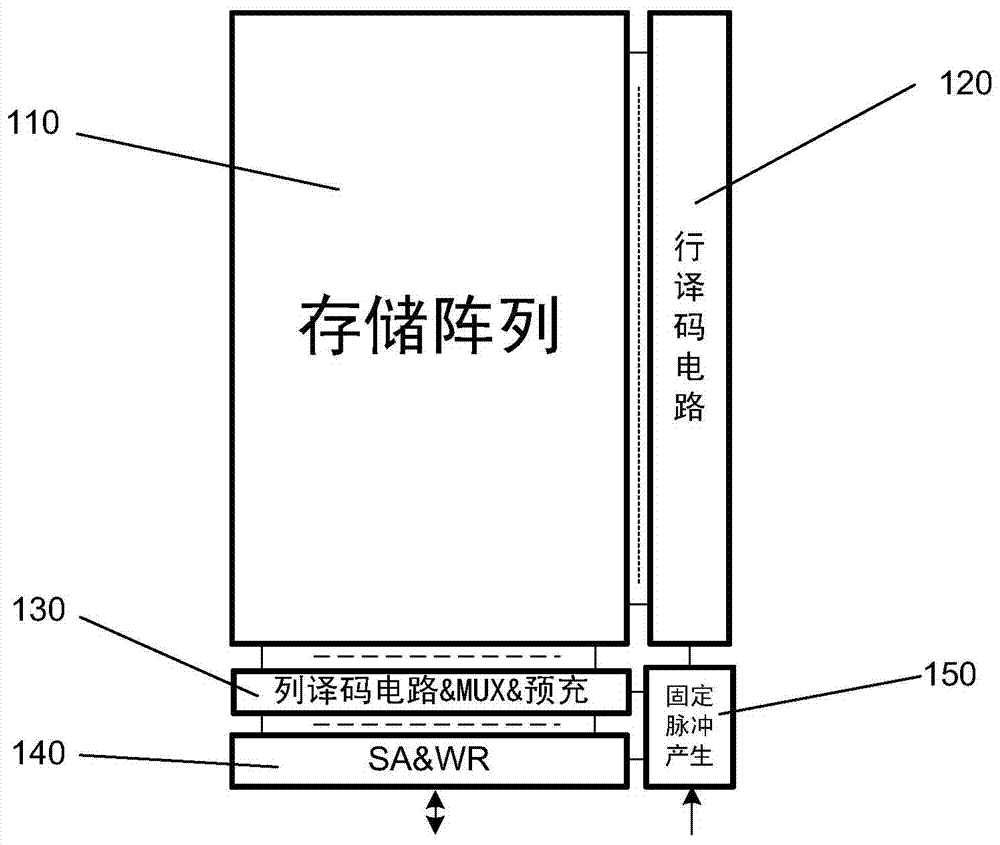

[0028] like figure 1 As shown, the traditional memory IP circuit structure includes a memory array 110 , a row decoding circuit 120 , a column decoding & MUX & precharging circuit 130 , a sensitive amplifier SA & WR 140 and a fixed pulse generator 150 . Fixed pulse generation 150 generates control pulses with fixed pulse width T during IP read / write operations, and sends them to row decoding circuit 120, column decoding & MUX & pre-charging circuit 130, sensitive amplifier SA & WR 140 to generate pulsed IP reading and writing timing. During the IP read operation, the row decoding circuit 120 generates a unique row strobe signal, which is used to strobe the only memory cell row in the memory array, and the selected row unit is turned on and discharges the connected bit line pair , and generate the bit line pair voltage difference; the column decoding & MUX & precharge circuit 130 generates a unique column strobe signal for each group of MUX, which is used to transmit the bit l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com