Dual cpu communication method, system and system-on-chip

A communication method and technology of a communication system, which is applied in the field of embedded devices, can solve problems such as channel data confusion, application program response delay, and affecting the normal operation of the CPU, and achieve the effects of shortening response delay, increasing speed, and improving user experience

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

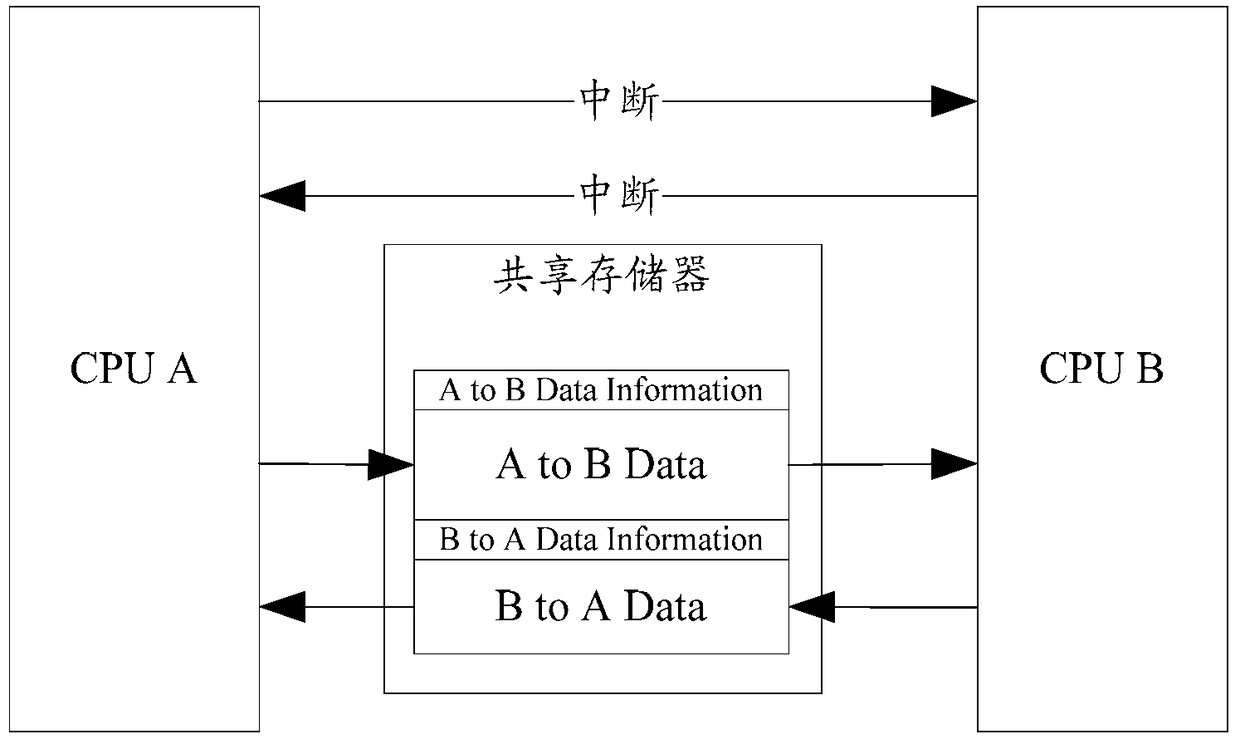

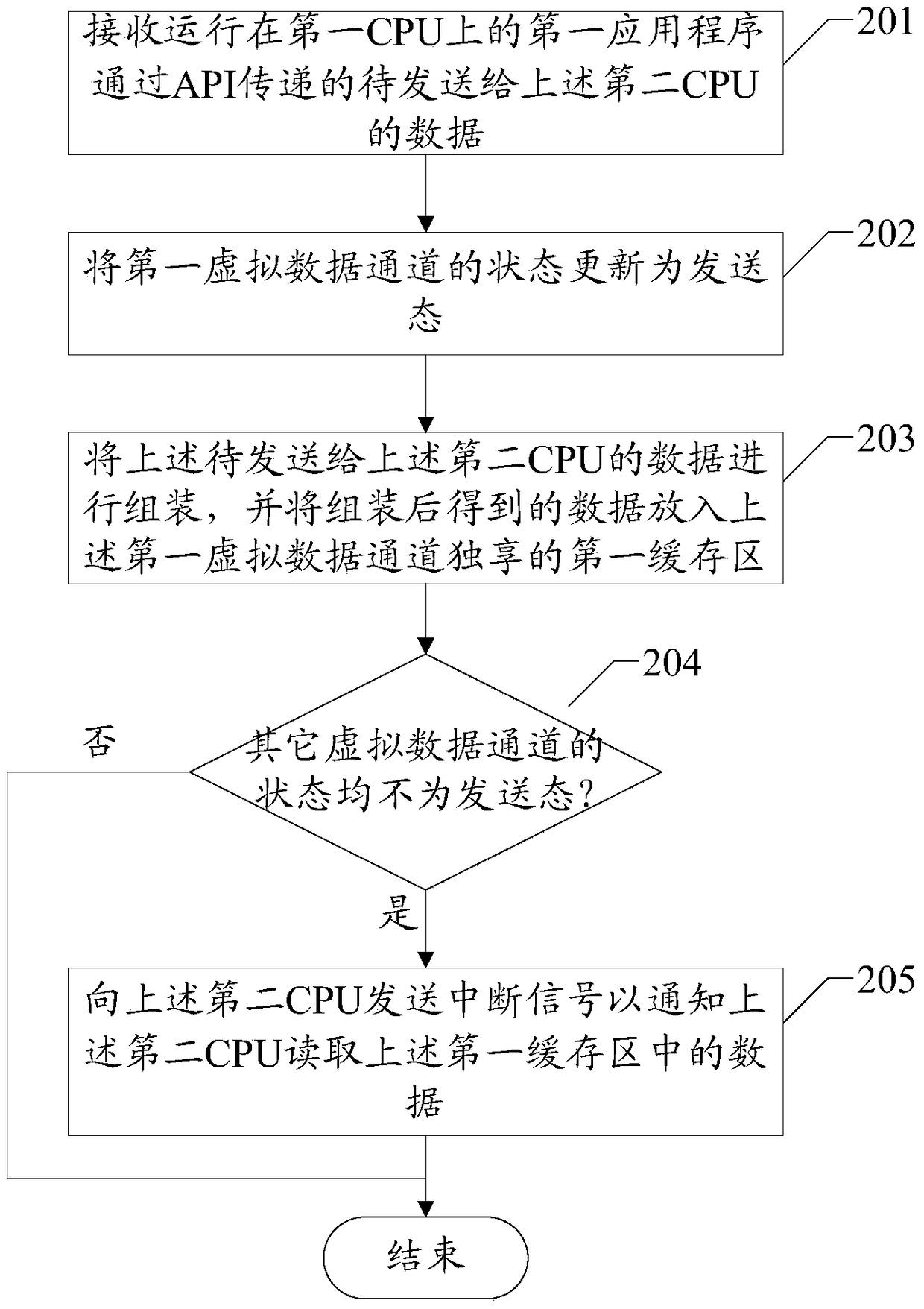

[0034] The present invention provides a dual-CPU communication method, the dual-CPU may include a first CPU and a second CPU, such as figure 2 As shown, the dual-CPU communication method may include:

[0035] 201. Receive data to be sent to the second CPU from a first application program running on the first CPU through an API (Application Programming Interface, application program interface);

[0036] It should be noted that the first CPU is any one of the dual CPUs, and the second CPU is another CPU of the dual CPUs;

[0037] The first application program may be any application program running on the first CPU;

[0038] 202. Update the state of the first virtual data channel to the sending state;

[0039] Wherein, the above-mentioned first virtual data channel is a virtual data channel exclusive to the first application program. In this embodiment, exclusive means that the first virtual channel can only be used by the first application program to pass the first The virtu...

Embodiment 2

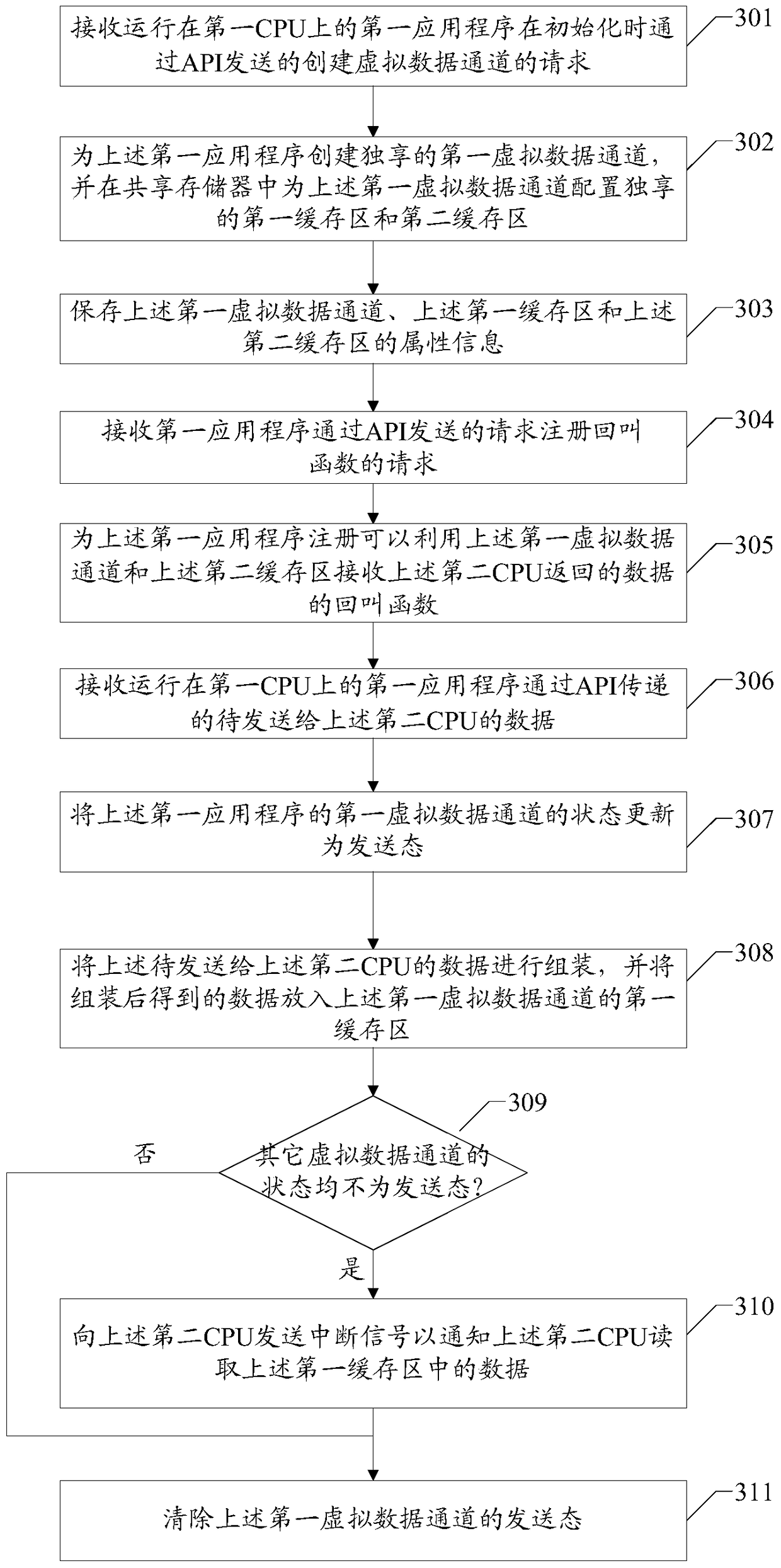

[0046] The present invention also provides a dual-CPU communication method, the dual-CPU may include a first CPU and a second CPU, such as image 3 As shown, the dual-CPU communication method may include:

[0047] 301. Receive a request for creating a virtual data channel sent by the first application program running on the first CPU through the API during initialization;

[0048] In this embodiment, when the application program is initialized, it can send a request to create a virtual data channel through the API interface;

[0049] 302. Create an exclusive first virtual data channel for the first application program, and configure an exclusive first buffer area and a second buffer area for the first virtual data channel in the shared memory;

[0050] After receiving the above request, an exclusive virtual data channel can be created for each application, and a two-way data buffer area can be allocated to the virtual data channel. Similarly, the buffer area is also exclusive...

Embodiment 3

[0092] The present invention also provides a dual-CPU communication system, which can be used to execute the method described in Embodiment 1 or 2, wherein the first CPU is any one of the dual CPUs, and the second CPU is the other one, such as Image 6 As shown, the system can include:

[0093] The receiving unit 601 is configured to receive the data to be sent to the second CPU transmitted by the first application program running on the first CPU through the application program interface API;

[0094] Wherein the first application program may be any application program running on the first CPU;

[0095] The channel status management unit 602 is configured to update the status of the first virtual data channel to the sending status; wherein, the first virtual data channel is a virtual data channel exclusive to the first application program, and in this embodiment, the exclusive means that the first virtual channel can only be used by the first application program to send data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More