Base-16 fixed point divider based on carry-save adder

An adder and fixed-point technology, applied in the digital field of computers, can solve the problems of complex circuits, insignificant performance improvement, long operation cycle, etc., and achieve the effect of eliminating delay and increasing operating frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

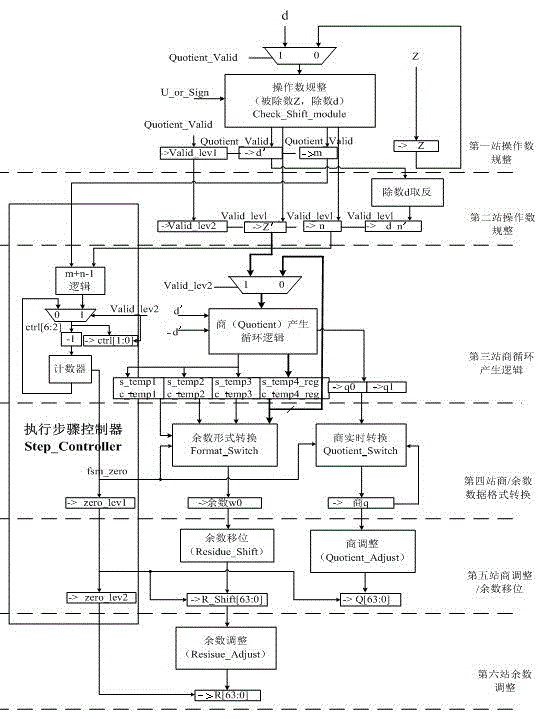

[0046] Take 64-bit data as an example:

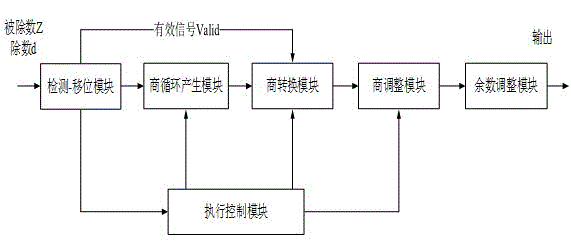

[0047] A base-16 fixed-point divider based on a carry-save adder, including a detection-shift module, a quotient cycle generation module, a quotient conversion module, a quotient / remainder adjustment module, and an execution control module;

[0048] The detection-shift module accepts the divisor d and the dividend, and divides the 64-bit data into 4 groups, each group is 16 bits. Align with the most significant bit of the divisor to eliminate unnecessary sign bits; the regularized divisor is d';

[0049] The detection-shift module includes a symbol judger, a negation generator, a leading 1 data selector, and a shifter;

[0050] The sign judger and the inversion generator are used to receive the sign of the divisor and the dividend. If the data is judged to be positive, the data will be passed through the inversion generator to turn it into a negative number for operation;

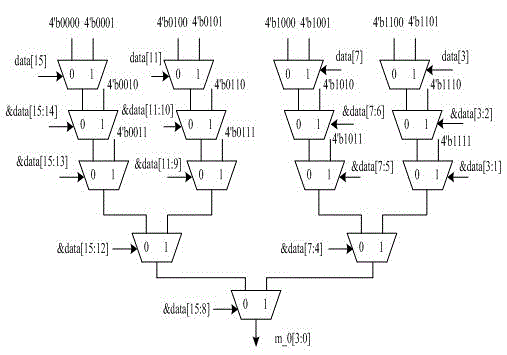

[0051] Find the leading 1 data selector, receive the data of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More