CMOS on-chip direct-current negative voltage generation circuit

A technology for generating circuits and negative voltages, applied to electrical components, adjusting electrical variables, instruments, etc., can solve problems such as inability to provide DC negative voltages

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

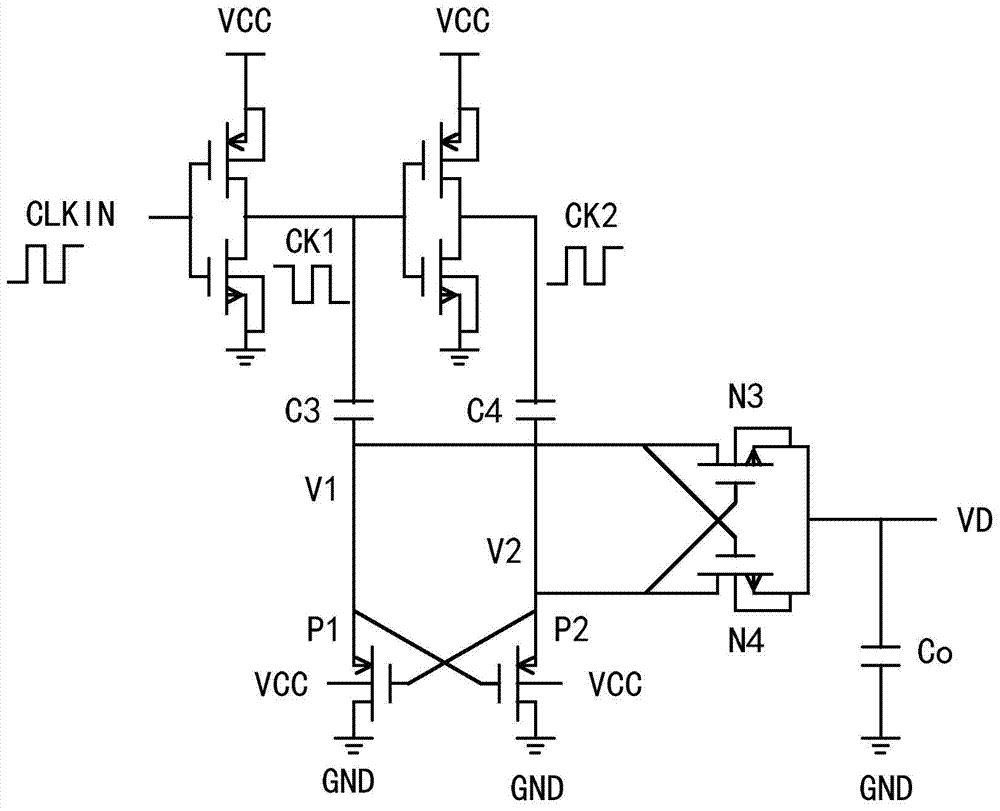

[0033] In order to make the technical means, creative features, goals and effects achieved by the present invention easy to understand, the present invention will be further described below in conjunction with specific illustrations.

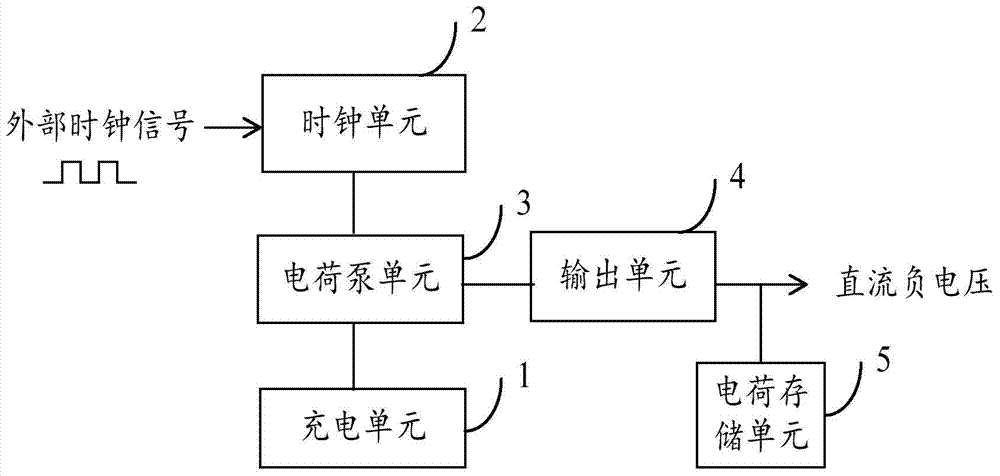

[0034] Please refer to figure 2 As shown, the present invention provides a CMOS on-chip DC negative voltage generating circuit, including a charging unit 1, a clock unit 2, a charge pump unit 3, an output unit 4 and a charge storage unit 5; wherein,

[0035] The charging unit 1 is configured to charge the charge pump unit 3;

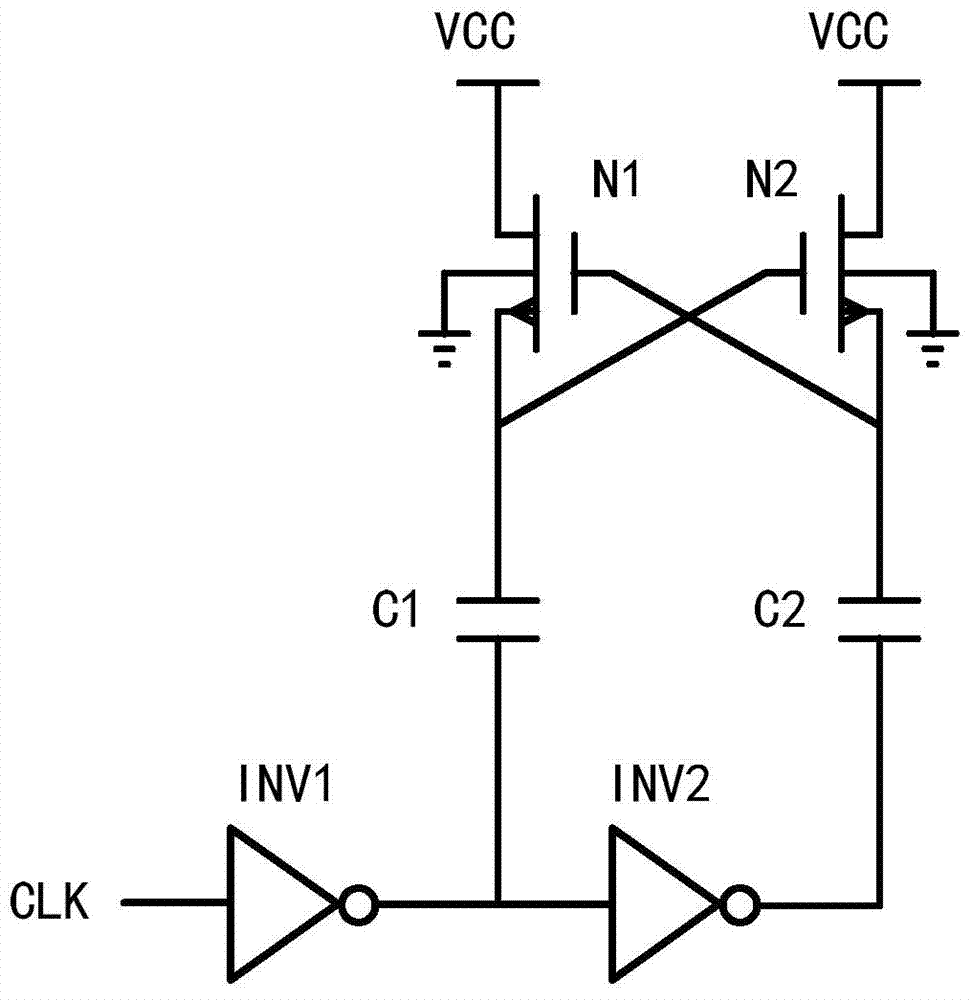

[0036] The clock unit 2 is configured to provide the required clock signal to the charge pump unit 3;

[0037] The charge pump unit 3 is used to generate a negative pulse voltage whose amplitude is equal to the positive power supply voltage;

[0038] The output unit 4 is configured to convert the negative pulse voltage generated by the charge pump unit 3 into a DC negative voltage, the magnitude of which is equal to the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More