Fin-type field effect transistor forming method

A fin-type field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve high deposition quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

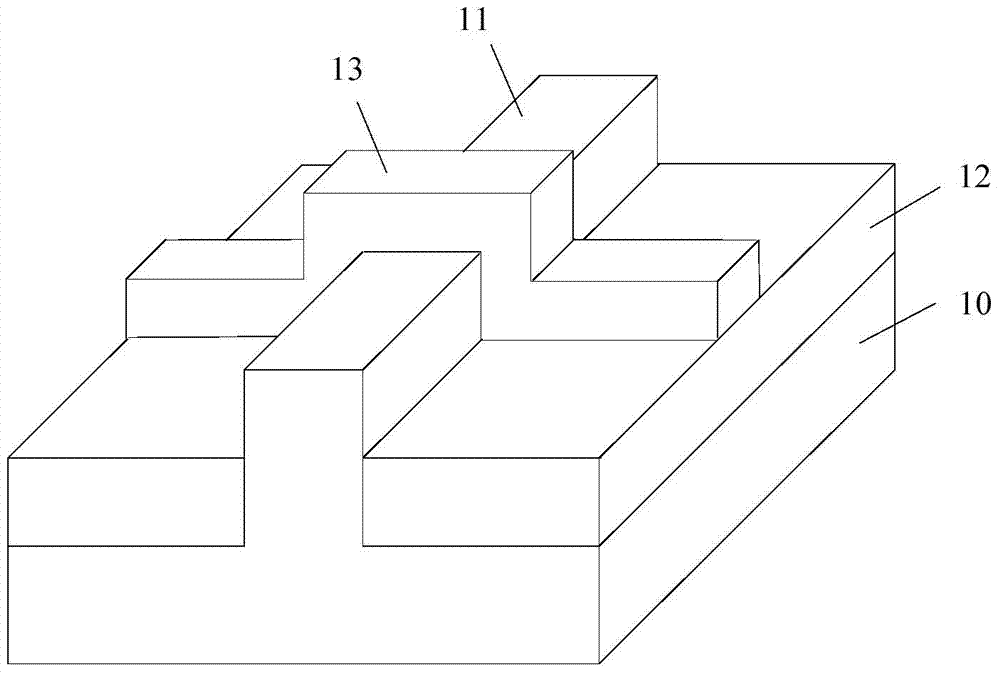

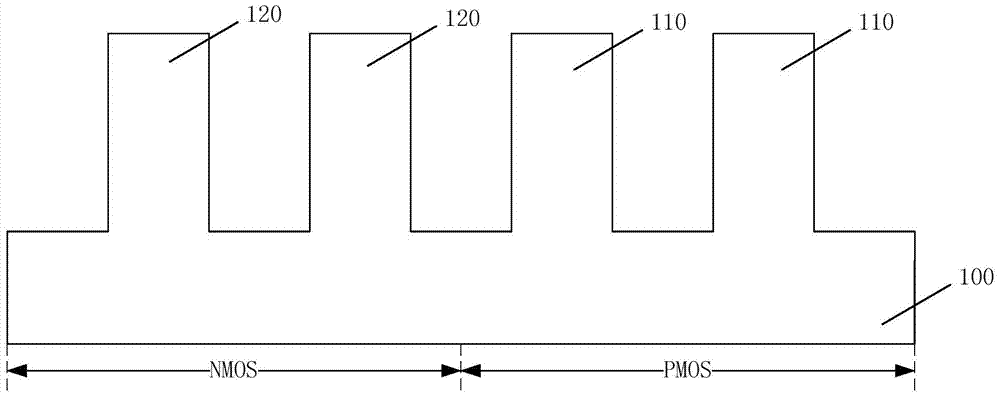

[0034] As mentioned in the background art, the performance of the fin field effect transistor formed in the prior art needs to be further improved.

[0035] Research has found that performing ion implantation on the source and drain regions of the fin field effect transistor to form the source and drain tends to cause more defects in the source and drain regions, and because the fin The size of the fins of the fin field effect transistors is smaller, which is more likely to affect the performance of the formed fin field effect transistors.

[0036] The source and drain electrodes formed on the fin portion of the fin field effect transistor by using the in-situ doping process can reduce the damage caused by ion implantation to the fin portion, but due to the gradual shrinking of the fin field effect transistor size, adjacent The distance between the fins of the N-type Fin Field Effect Transistor and the P-Type Fin Field Effect Transistor is small, and the distance between the e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More