How the transistor is formed

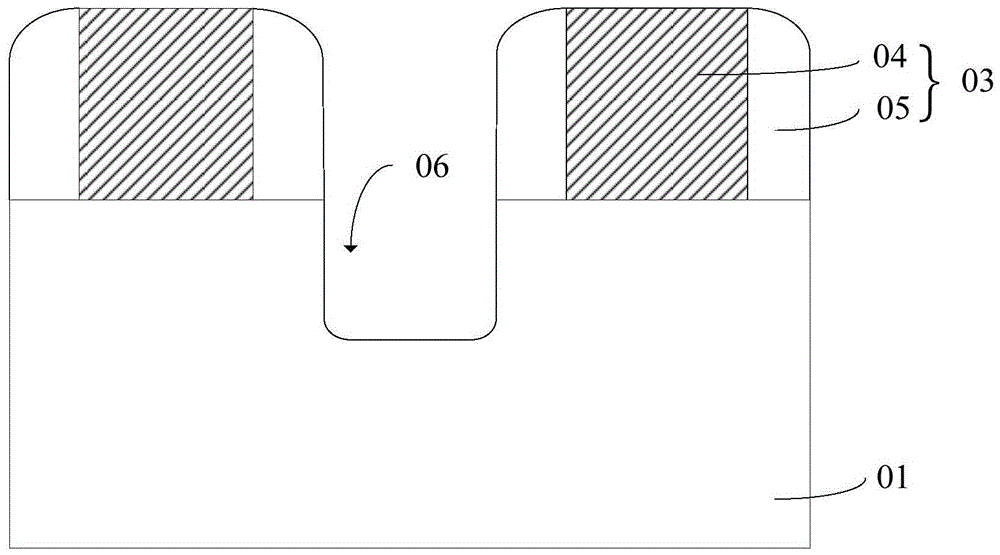

A transistor, dry etching technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as the large difference in the depth of the Σ-shaped groove and the large difference in the depth of the rectangular groove 06. The effect of enhancing controllability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In the process of forming Σ-shaped grooves in the prior art, how to better control dry etching to form grooves with a uniform depth and reduce the vertical and lateral distances of the Σ-shaped grooves has become an urgent problem to be solved.

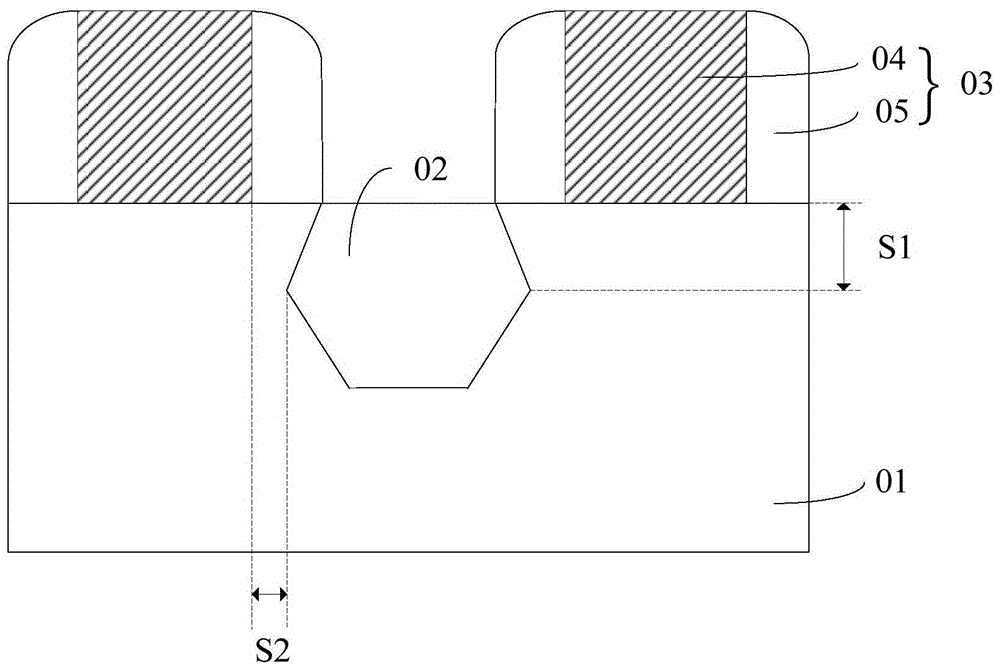

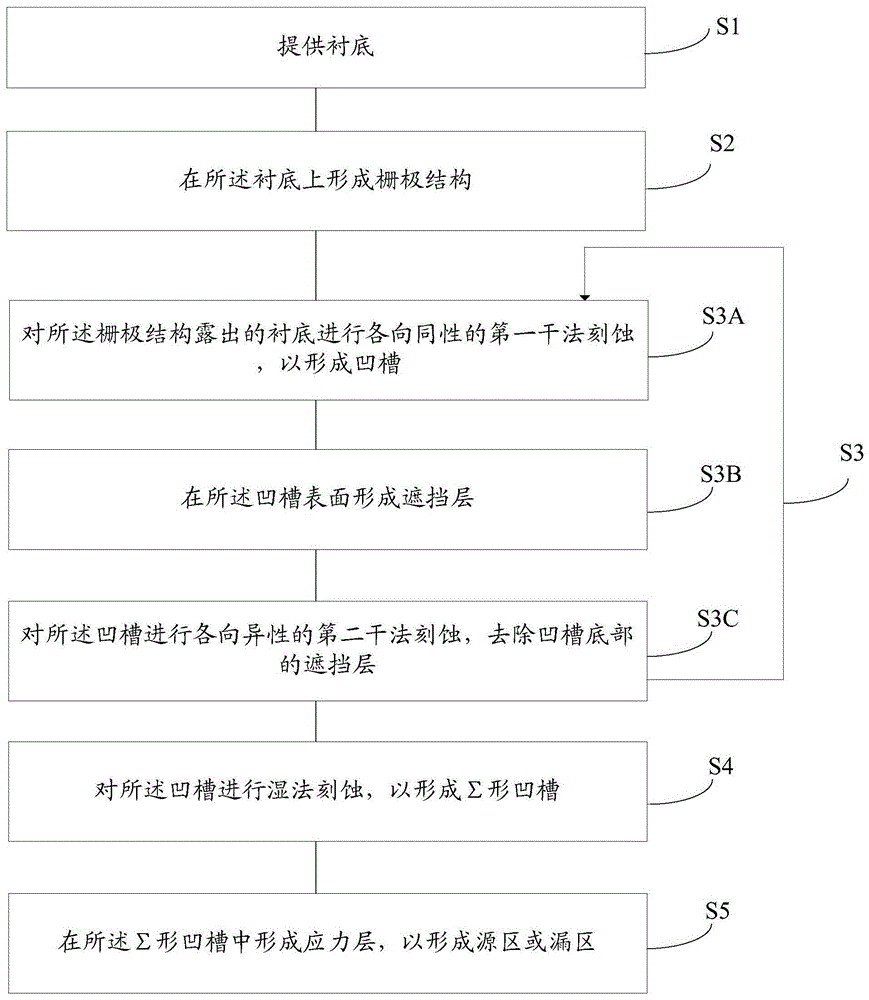

[0039] In order to solve the above technical problems, the present invention provides a method for forming a transistor, which can form an altar-shaped groove with a concave side wall in the substrate, and wet-etch the altar-shaped groove to form a Σ-shaped groove The vertical distance and the lateral distance of the groove are smaller, and the stress layer is formed in the Σ-shaped groove to form the source region or the drain region, which can optimize the performance of the transistor. And the etching of the groove is divided into repeated steps of multi-step isotropic and anisotropic dry etching, which enhances the controllability of dry etching, so that grooves of different sizes may be located in the center of the wafer T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More