Semiconductor etching method and semiconductor etching system

An etching system and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, electrical components, etc., can solve problems such as ineffective reduction of errors, device differences, and inability to reduce errors. Achieve the effect of improving etching precision, reducing error and reducing depth difference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

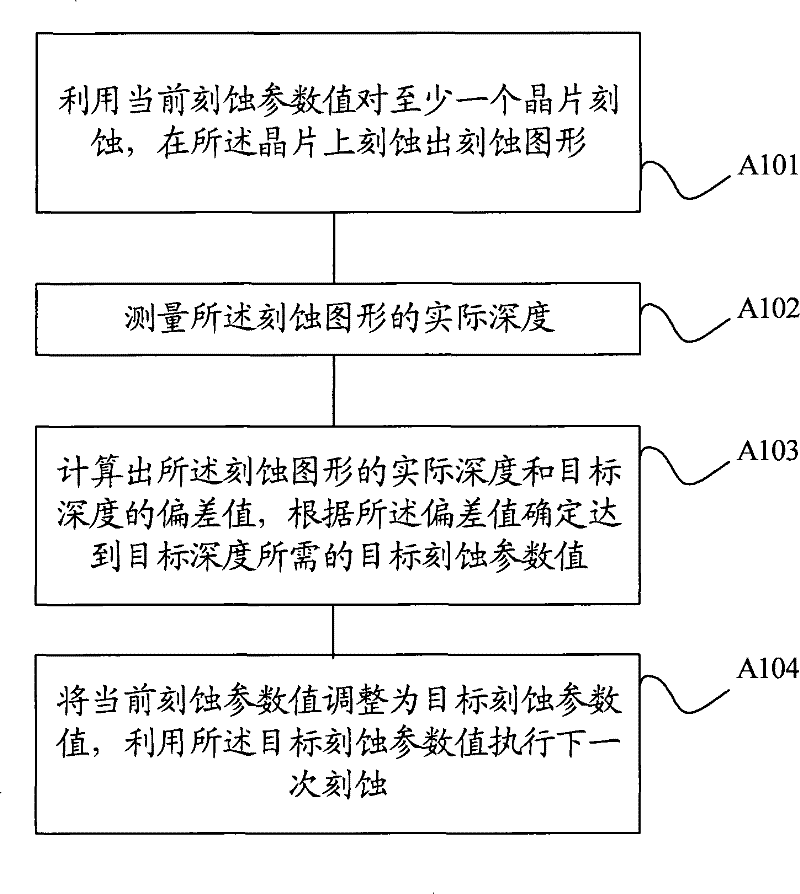

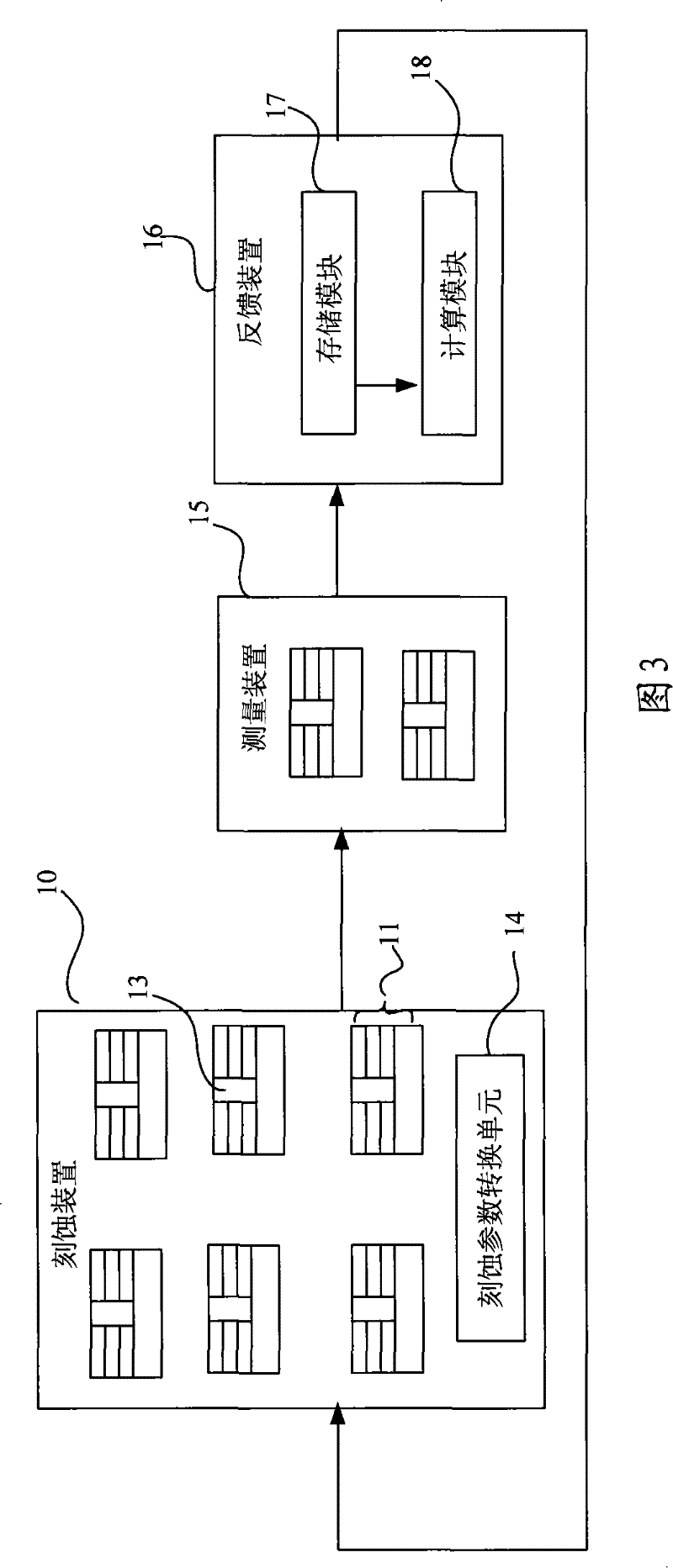

[0033] In order to make the above-mentioned purposes, features and advantages of the present invention more obvious and understandable, the specific implementation modes of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the above-mentioned and other purposes, features and advantages of the present invention will be clearer. Like reference numerals designate like parts throughout the drawings. The drawings have not been drawn to scale, emphasis instead being placed upon illustrating the gist of the invention.

[0034] For clarity, in the following description, well-known functions and constructions are not described in detail since they would obscure the invention with unnecessary detail. It should be appreciated that in the development of any actual embodiment, numerous implementation details must be worked out to achieve the developer's specific goals, such as changing from one embodiment to another in accordance...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More