A k-nearest neighbor classification acceleration method based on opencl and soc-fpga

A technology of K-nearest neighbors and classification data, which is applied in the acceleration field of K-nearest neighbors classification technology, which can solve the problems of occupying a lot of hardware resources, large system delay, and large amount of computation, and achieve low power consumption, small system delay, and data throughput high volume effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

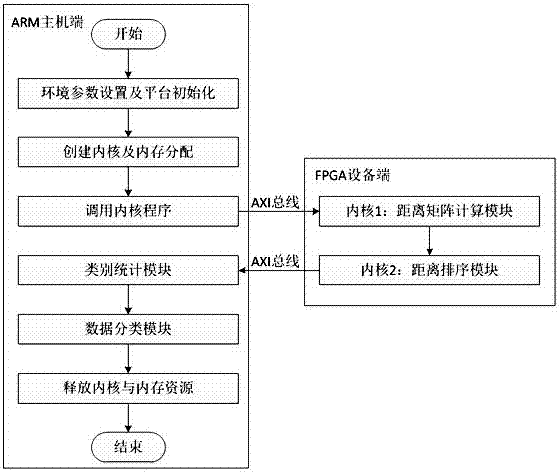

[0032] Further describe the technical scheme of the present invention in detail below in conjunction with accompanying drawing:

[0033] The procedure of this method is as follows figure 1 As shown, the ARM is the host side, which is connected to the FPGA device side through the AXI bus. The high bandwidth feature of the AXI on-chip bus will greatly shorten the communication delay between the host and the device and improve the system throughput. According to the task allocation of the K-nearest neighbor classification algorithm, the calculation-intensive and suitable parallel distance matrix calculation and distance sorting part are executed on the FPGA side in the form of kernel programs, and the light-calculating and difficult-to-parallel parts such as category statistics and classification are executed on the ARM side. .

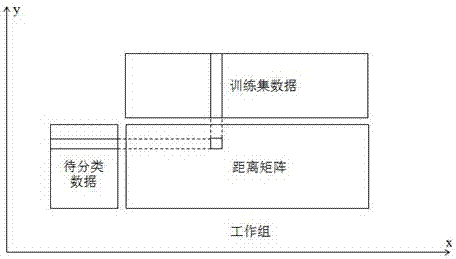

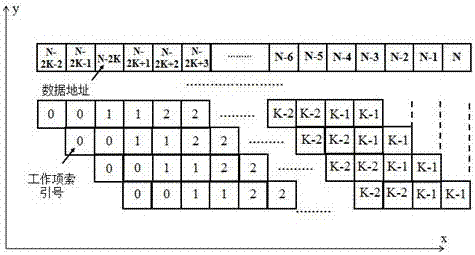

[0034] The memory model provided by the OpenCL standard includes global memory, local memory, and private memory, etc. Since the global memory has many...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More