Clock control method and apparatus

A clock control and clock technology, applied in data processing power supply, signal generation/distribution, etc., can solve problems affecting chip performance, increase software complexity, etc., achieve the effect of increasing reusability, reducing software complexity, and improving processing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

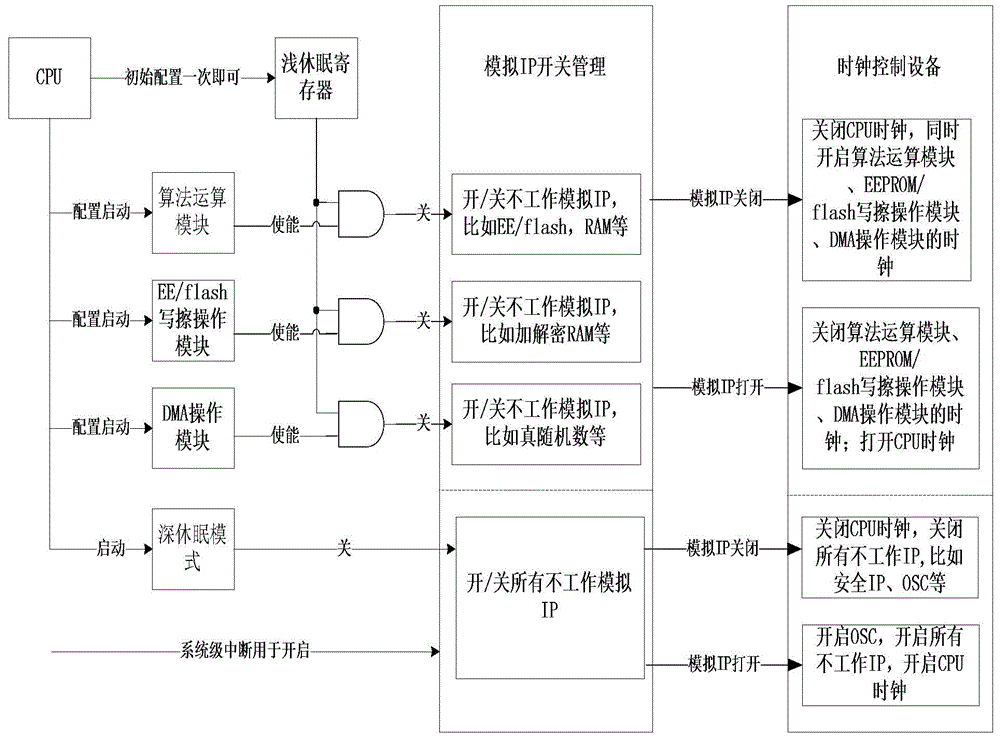

[0026] Hereinafter, the present invention will be described in detail with reference to the drawings and examples. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

[0027] Such as image 3 As shown, it includes: CPU, shallow sleep register, algorithm operation module, EEPROM / flash write and erase operation module, DMA (Direct Memory Access, memory direct access) operation module, deep sleep mode, analog IP switch management, clock control device.

[0028] Pre-configure the clock control strategy in the shallow sleep register;

[0029] When the business module is running, the clock control device closes the non-working analog IP in the light sleep mode according to the clock control strategy obtained from the light sleep register;

[0030] Turning off the analog IP that does not work in shallow sleep mode includes: turning off the CPU clock, turning on the clock...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com