Floating point processing unit integration circuit and method of RISC processor

A technology for processing units and integrated circuits, applied in machine execution devices, concurrent instruction execution, etc., can solve the problems of low versatility of integration methods, many logic modifications, and reduced instruction execution performance, and achieves small design logic changes and selectivity. Wide, floating-point integrated structure for clear effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be further described in detail below in conjunction with specific embodiments, which are for explanation rather than limitation of the present invention.

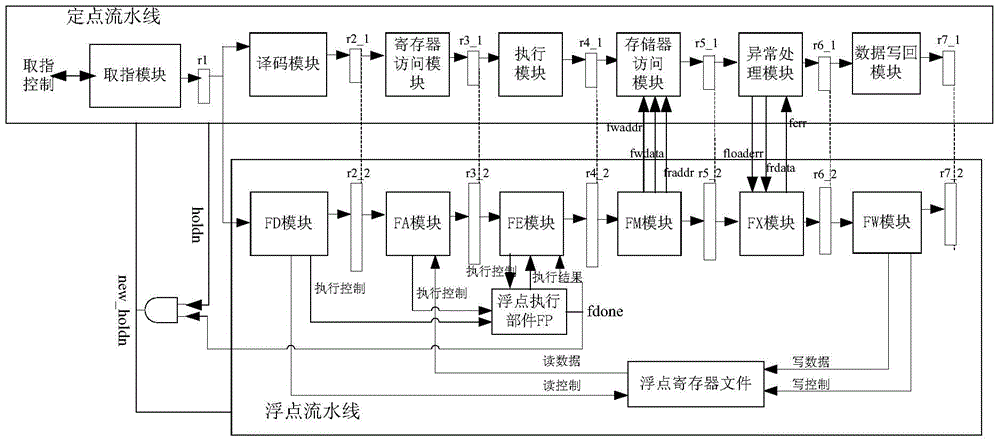

[0052] The present invention is aimed at a processor with a seven-stage pipeline (fetching stage, decoding stage, register access stage, execution stage, memory access stage, exception handling stage and data write-back stage) for efficient operation of fixed-point instructions and floating-point instructions.

[0053] First, like figure 1 As shown, on the basis of the seven-stage fixed-point pipeline, the instruction fetch stage, the decoding stage, the register access stage, the execution level, the memory access level, the exception handling stage, and the data write-back stage, the other six stages except the instruction fetch stage are added. Floating point pipeline includes decoding stage, register access stage, execution stage, memory access stage, exception handling stage, data write-back...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More