Memory solder joint realizing interconnection of 3D packaging chips

A technology for chip mounting and memory, applied in the field of three-dimensional packaging of electronic devices, to achieve the effect of high service life and high reliability requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

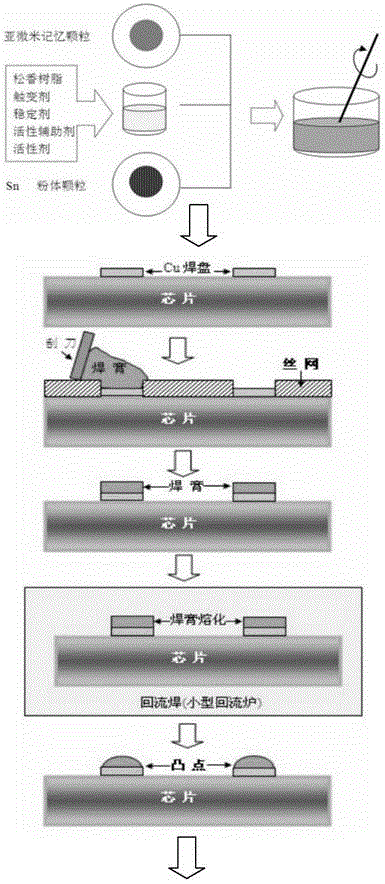

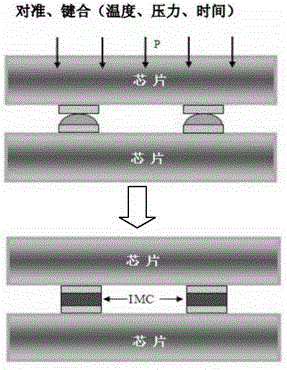

Method used

Image

Examples

Embodiment 1

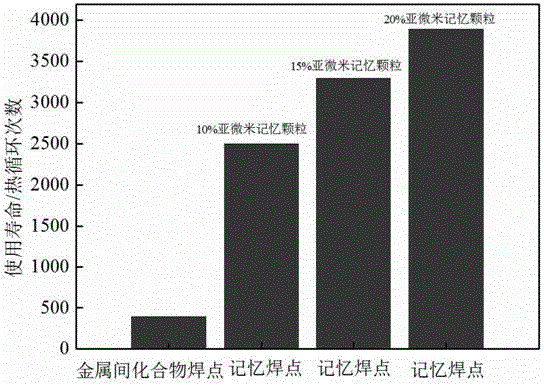

[0016] The solder paste containing submicron memory particles used for interconnection of 3D packaged chips has a submicron memory particle content of 10%, and the balance is Sn. Mix rosin resin, thixotropic agent, stabilizer, active auxiliary and active agent to prepare solder paste.

[0017] The service life of the memory solder joint formed after bonding (235℃, 9MPa) is about 2500 thermal cycles (taking into account the test error), and the solder paste has excellent solderability.

Embodiment 2

[0019] The solder paste containing sub-micron memory particles used for interconnection of 3D packaged chips has a sub-micron memory particle content of 12%, and the balance is Sn. Mix rosin resin, thixotropic agent, stabilizer, active auxiliary and active agent to prepare solder paste.

[0020] The service life of the memory solder joint formed after bonding (255℃, 5MPa) is about 2850 thermal cycles (taking into account the test error), and the solder paste has excellent solderability.

Embodiment 3

[0022] The solder paste containing sub-micron memory particles used for interconnection of 3D packaged chips has a sub-micron memory particle content of 14%, and the balance is Sn. Mix rosin resin, thixotropic agent, stabilizer, active auxiliary and active agent to prepare solder paste.

[0023] The service life of the memory solder joint formed after bonding (245℃, 10MPa) is about 3000 thermal cycles (taking into account the test error), and the solder paste has excellent solderability.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com