Display panel and manufacturing method thereof, and TFT test method

A technology for display panels and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, electrical measurement, etc., and can solve problems such as the inability to comprehensively measure the display effect of electroluminescent layers and the electrical characteristics of thin-film transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

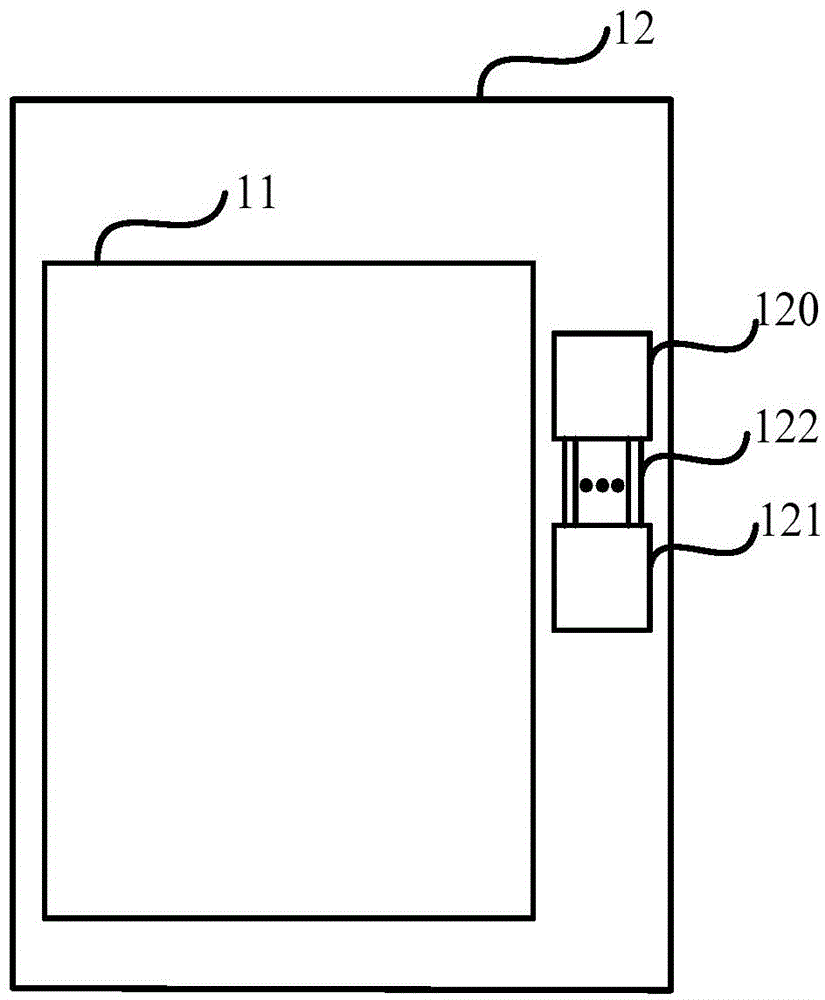

[0043] See figure 1 A display panel provided by an embodiment of the present invention includes a display area 11 and a peripheral area 12 outside the display area. The peripheral area 12 includes: an electroluminescent layer test area 120, a TFT test area 121, and a lead line 122; among them,

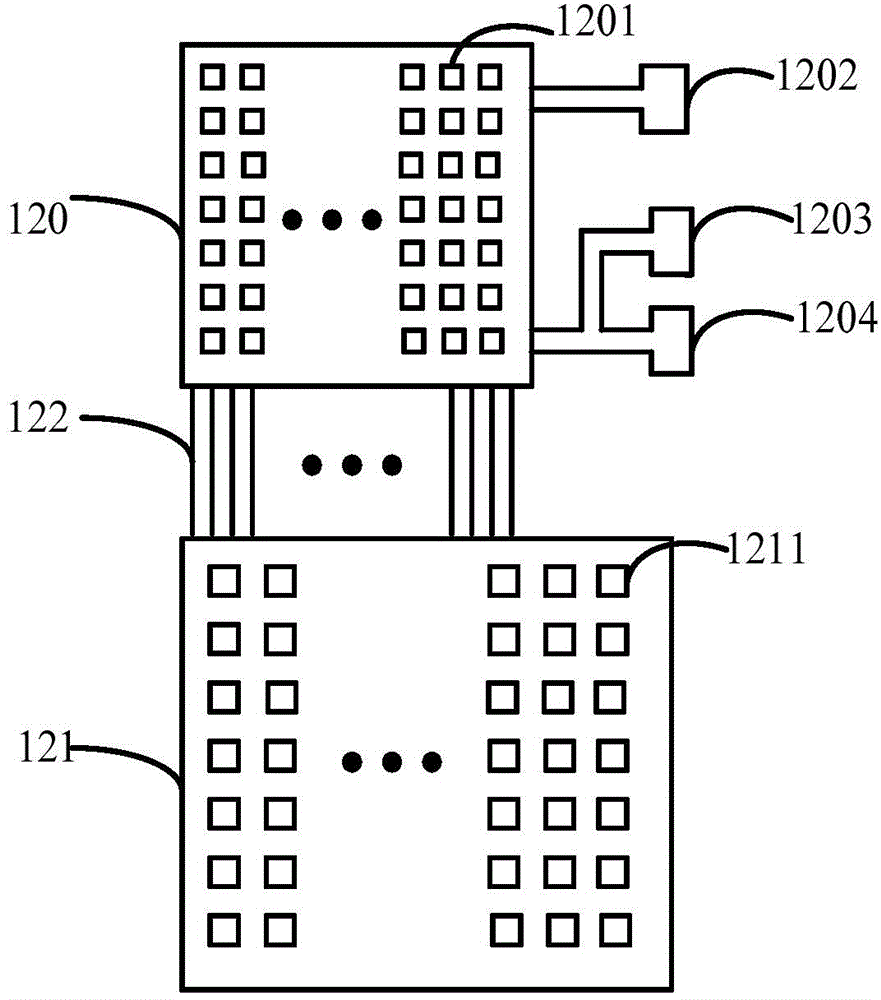

[0044] See figure 2 The specific structure of the electroluminescent layer test area 120, the TFT test area 121, and the lead line 122 in the peripheral area provided by the embodiment of the present invention. The electroluminescence layer test area 120 includes a plurality of thin film transistors 1201 having electroluminescence layers, a first test line 1202 connecting the sources of the plurality of thin film transistors having electroluminescence layers, and connecting a plurality of thin film transistors having electroluminescence layers. The switch lead 1203 and the second test line 1204 of the gate of the thin film transistor of the layer;

[0045] The TFT test area 121 includes a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More