System and method for quick frame header synchronization

A synchronization system and frame header technology, which is applied in the field of satellite data transmission data receiving and processing, can solve the problem that the frame header synchronization method cannot meet the data processing speed requirements, and achieve the effect of meeting the data processing speed requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

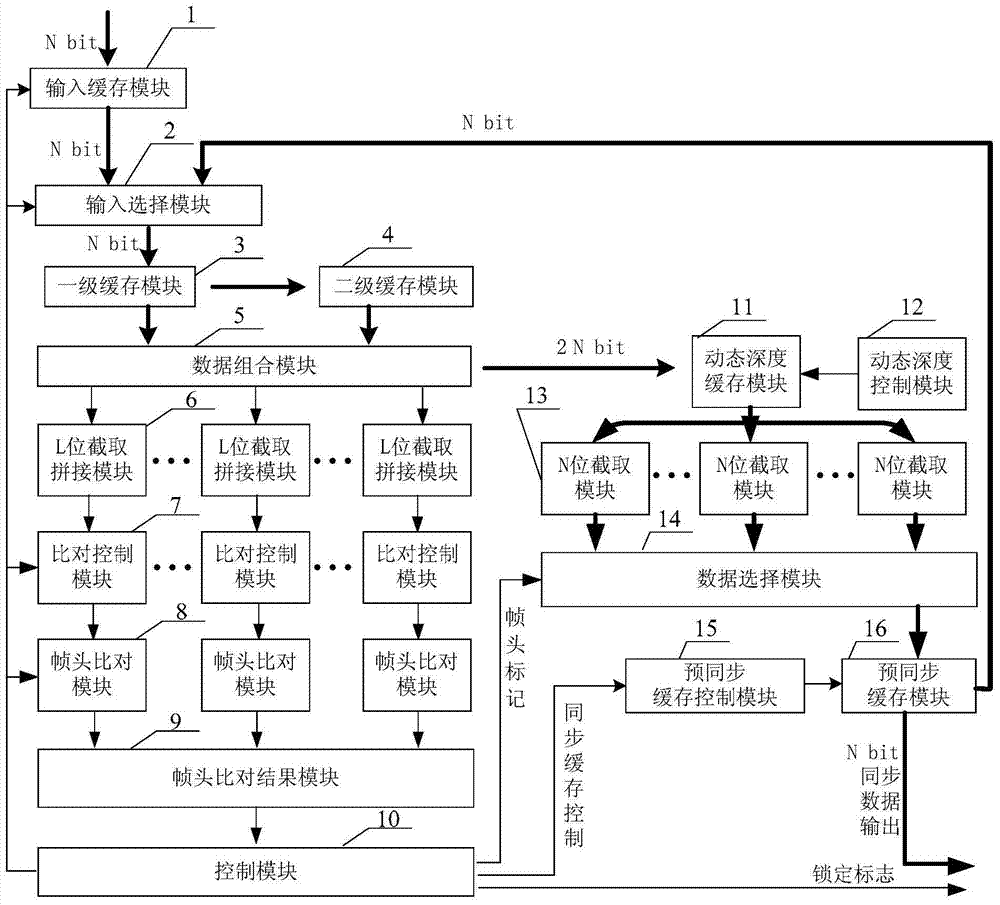

[0043] Specific implementation mode one: the following combination figure 1 and figure 2 Describe this embodiment, the frame header fast synchronization system described in this embodiment includes:

[0044]An input buffer module 1 for buffering unsynchronized N bit parallel frame data and outputting N bit parallel frame data under the control of the control module 10; N is an integer multiple of 8, ranging from 32 to 512;

[0045] An input selection module 2 for selecting and outputting the N bit parallel frame data received in the input buffer module 1 and the N bit pre-synchronized buffer data received in the pre-synchronized buffer module 16 under the control of the control module 10; the value of L is 8 Integer multiples of , ranging from 8 to 64; L is less than N;

[0046] A first-level cache module 3 for performing a first-level cache of the N bit data selected and output by the input selection module 2;

[0047] A secondary cache module 4 for receiving N bit data o...

specific Embodiment approach 2

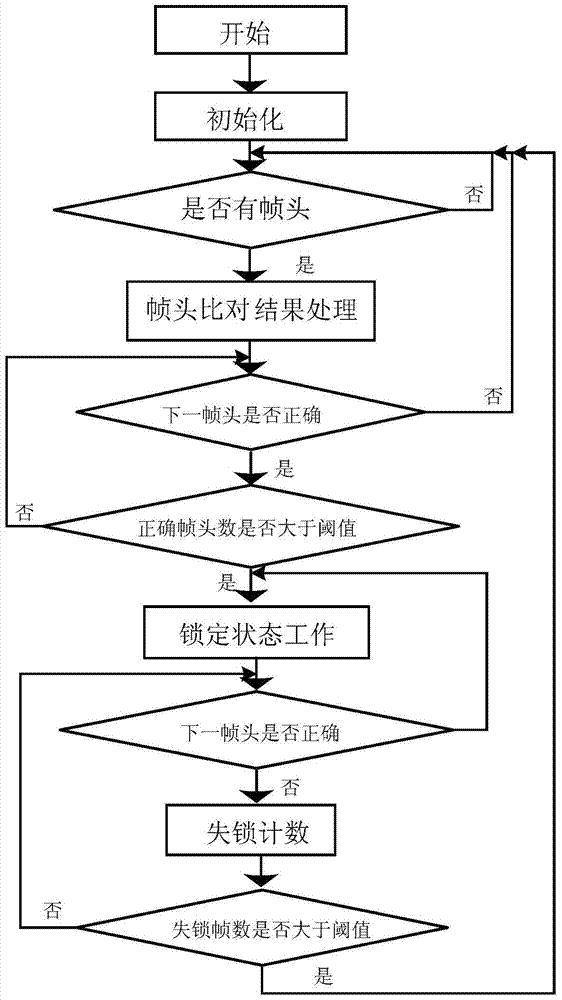

[0060] Specific embodiment two: this embodiment is further described to embodiment one, and the specific process that control module 10 determines to retrieve frame header is: judge whether there is frame header in the N bit data that frame header comparison result module 9 outputs, if in one time If a 1 occurs in the N bit data output by the frame header comparison result module 9 in the comparison, then it is determined to be a frame header mark; 1, then select the lowest 1 and determine it as the frame header mark.

specific Embodiment approach 3

[0061] Specific implementation mode three: the following combination figure 1 and figure 2 Describe this embodiment, the frame header fast synchronization method described in this embodiment includes:

[0062] A step for buffering unsynchronized N bit parallel frame data through the input buffer module 1, and outputting N bit parallel frame data under the control of the control module 10; N is an integer multiple of 8, ranging from 32 to 512;

[0063] A step for selecting and outputting the N bit parallel frame data received in the input buffer module 1 and the N bit pre-synchronized buffer data received in the pre-synchronized buffer module 16 under the control of the control module 10 through the input selection module 2; The value is an integer multiple of 8, ranging from 8 to 64; L is less than N;

[0064] A step for performing a first-level cache of the N bit data selected and output by the input selection module 2 through the first-level cache module 3;

[0065] A st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More