Wear balancing method of non-volatile memory based on multi-level cell

A technology of wear leveling and multi-layer units, applied in the direction of memory address/allocation/relocation, etc., can solve the problems of reduced service life and performance degradation, and achieve high service life, low space overhead, high service life and security Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

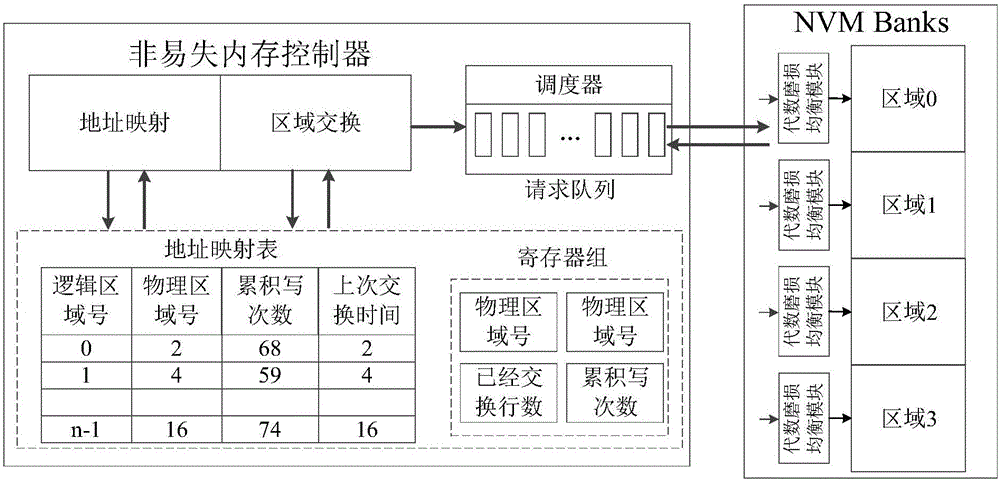

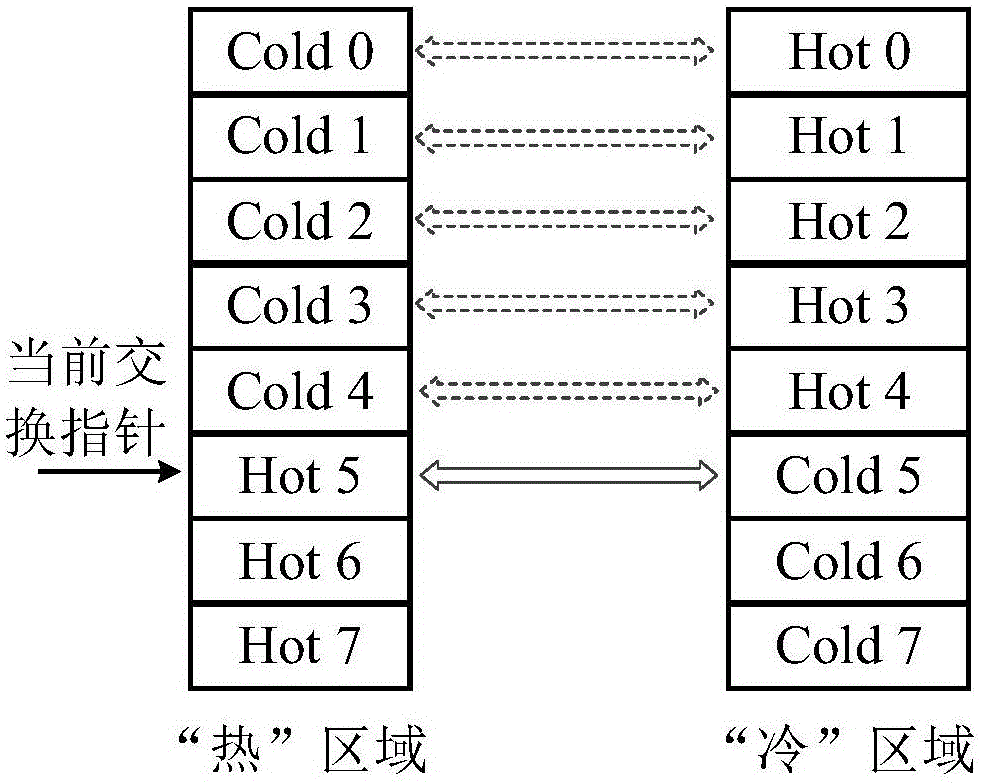

[0020] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

[0021] In order to facilitate understanding of the present invention, at first the following nouns appearing in the present invention are explained:

[0022]Physical row: The most basic access unit of the memory system. In different systems, the row size can be different, usually a row size can be 64 bytes, 128 bytes, 256 bytes.

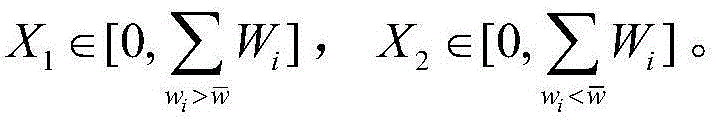

[0023] Sub-storage area: composed of several physical rows, usu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More