Time-domain hardened latch capable of resisting dual-node upset

A dual-node inversion and latch technology, applied in electrical components, logic circuits, pulse technology, etc., can solve problems such as few reports and inability to resist single-event pulses

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

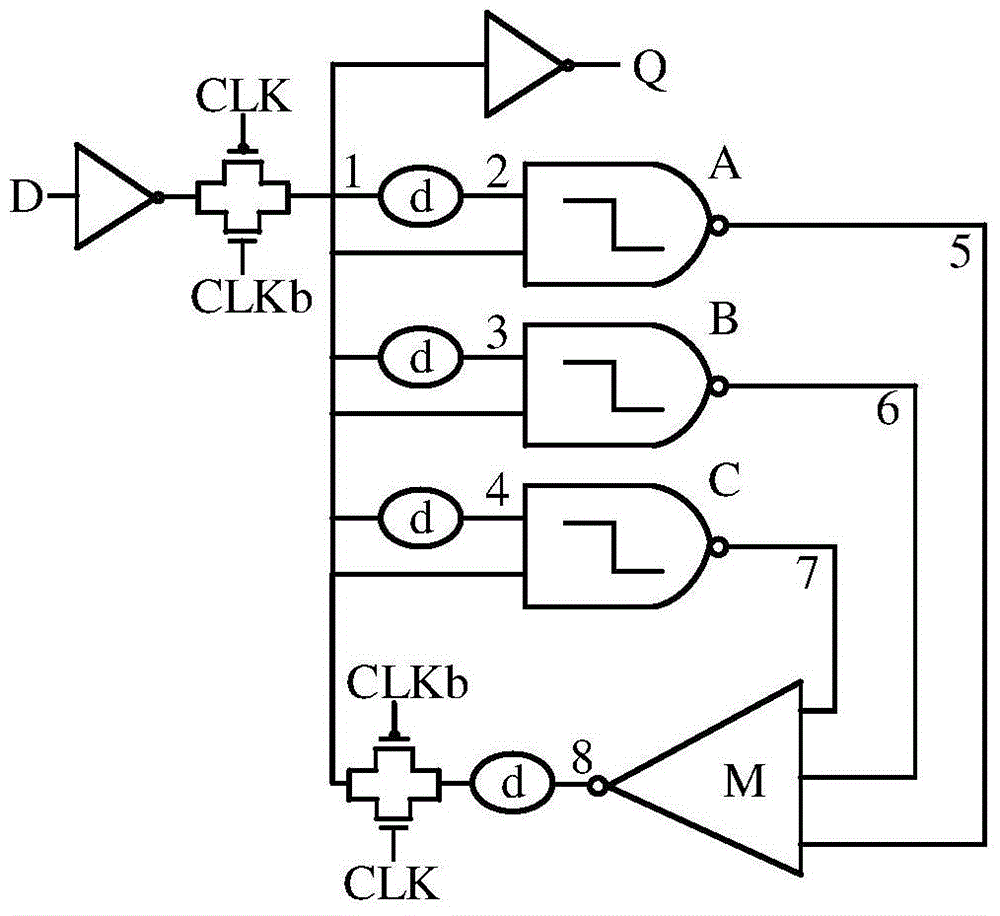

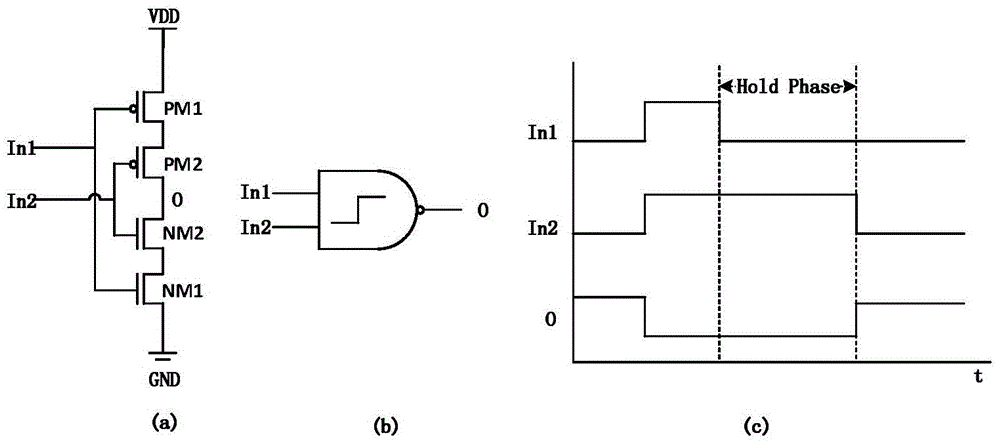

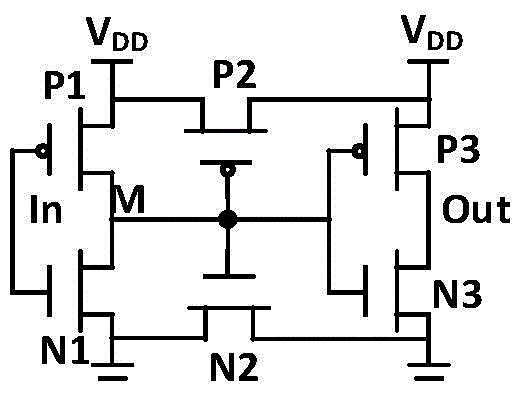

[0013] use as figure 1 The circuit configuration shown. The latch is composed of 3 double-input protection gates (DoubleInputGuard_gate, DIG), 4 delay units, 2 transmission gates, 2 inverters and 1 three-select two-way multiplexer. The node 1 after the input D passes through an inverter and a low-level conduction transmission gate, and the node 2 after it passes through the first delay unit are jointly used as the input of DIGA. 1 and its node 3 after the second delay unit are used as the input of DIGB. 1 and its node 4 after the third delay unit are used as the input of DIGC. The output nodes of A, B, and C are 5, 6, and 7 in turn, and they are also the input of the three-to-two multiplexer, and the output nodes are 8, 8. After the fourth delay unit and a high-level conduction transmission Feedback to 1 node behind the gate. Node 1 is connected to an inverter and then output, and the output node is Q. Since one of the inputs of DIG is delayed for a certain time, the effe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com