A kind of fpga virtual io inter-chip interconnection digital circuit based on re-encryption algorithm

A digital circuit, re-encryption technology, applied in the direction of encryption device with shift register/memory, etc., can solve the problems of limited number of interfaces, reduced security performance, and inability to meet user IC design.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

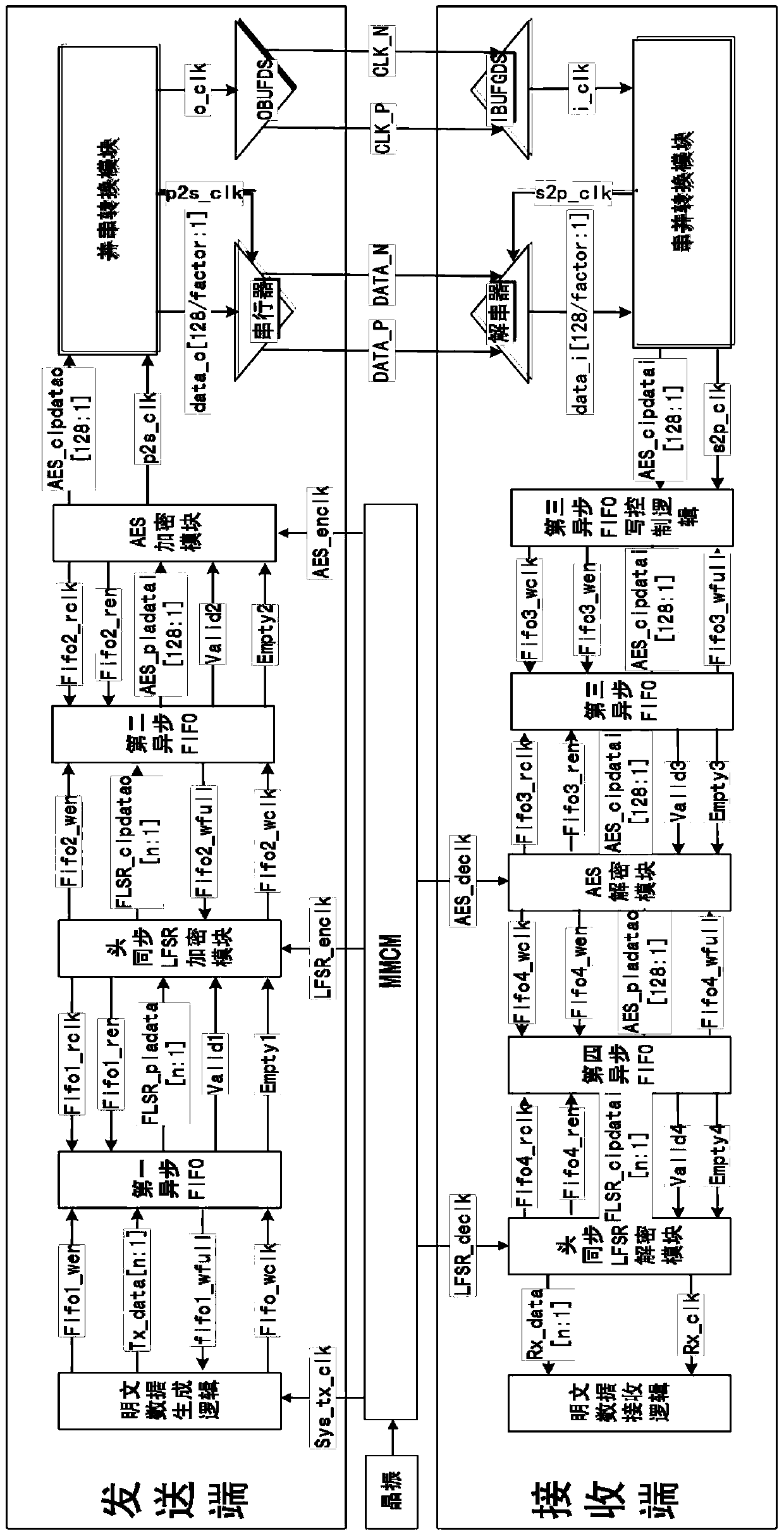

[0051] In the present embodiment, a kind of FPGA virtual IO inter-chip interconnection digital circuit based on re-encryption algorithm, it comprises: sending end digital circuit, receiving end digital circuit and clock generating module; Clock generating module comprises a crystal oscillator and an MMCM; Digital All clocks in the circuit are homologous clocks generated by MMCM;

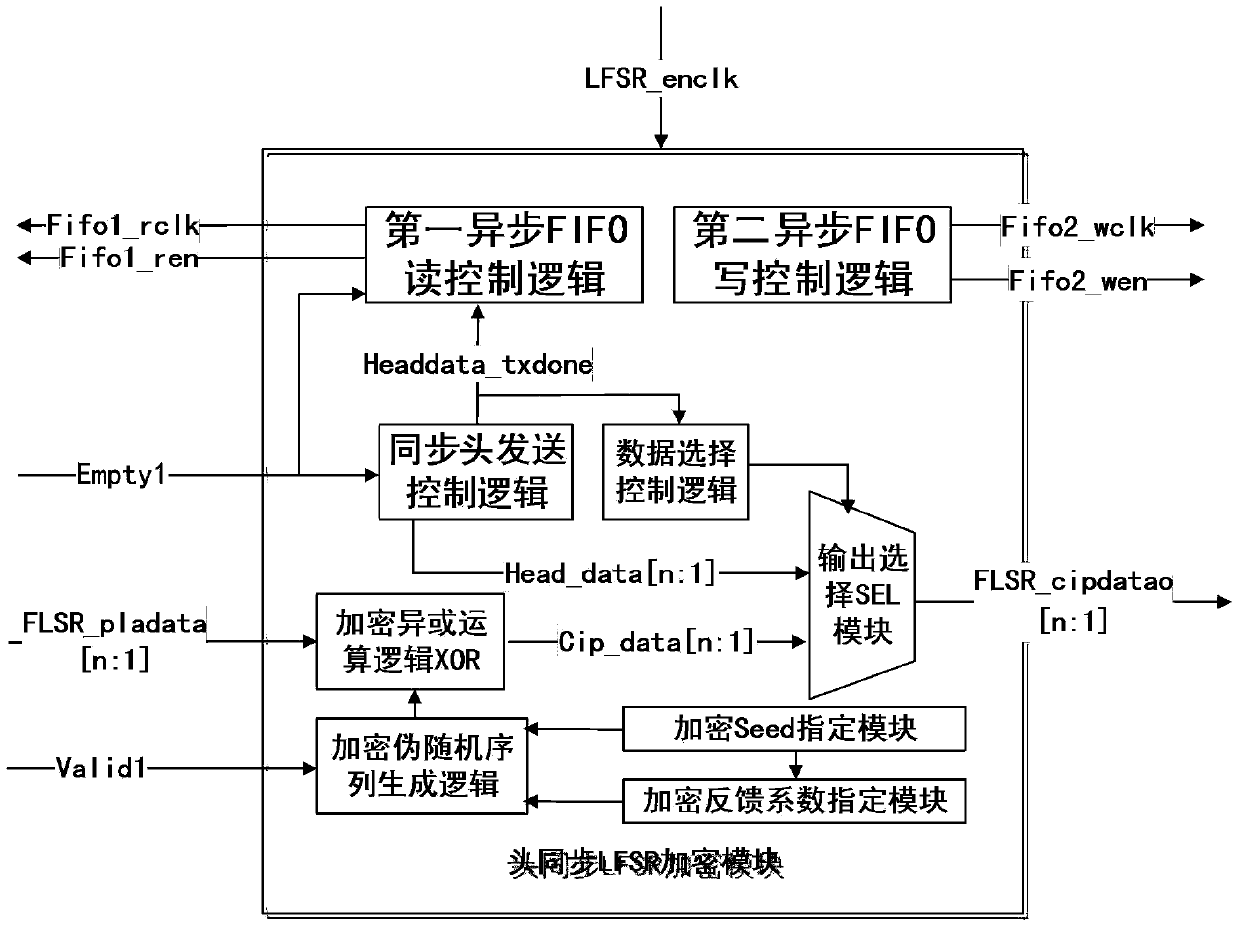

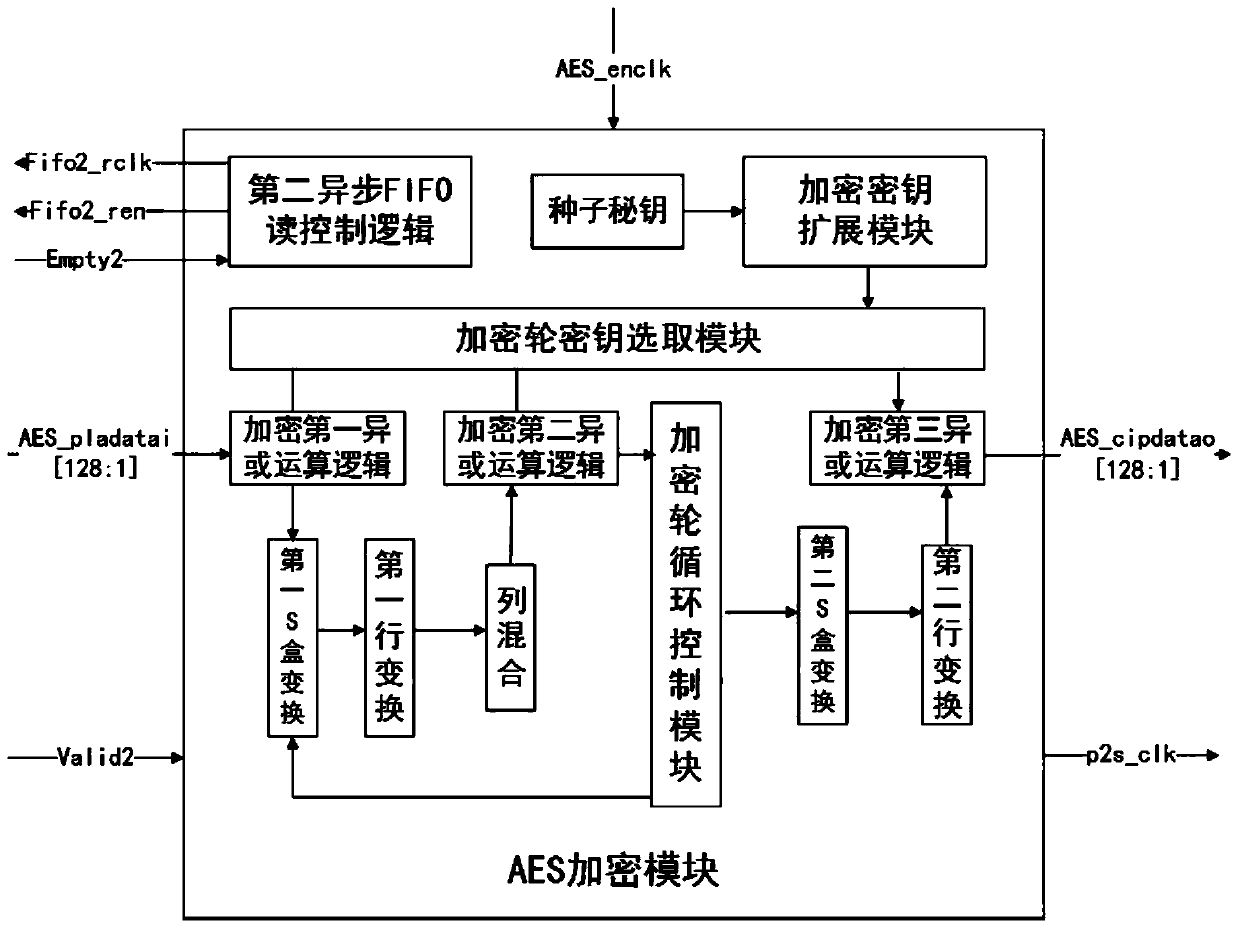

[0052] Such as figure 1 As shown, the digital circuit at the sending end includes plaintext data generation logic, a first asynchronous FIFO, a header synchronous LFSR encryption module, a second asynchronous FIFO, an AES encryption module, a parallel-to-serial conversion module, a serializer, and an OBUFDS module;

[0053] The digital circuit at the receiving end includes a deserializer, an IBUFGDS module, a serial-to-parallel conversion module, a third asynchronous FIFO write control logic, a third asynchronous FIFO, an AES decryption module, a fourth asynchronous FIFO, a header synchronous LFSR de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More