Formation method of semiconductor structure

A technology of semiconductor and dummy gate structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of unstable performance and poor reliability of fin field effect transistors, and achieve uniform and reliable atomic distribution density The effect of improving performance and stabilizing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] As mentioned in the background, the FinFETs formed in the prior art have unstable performance and poor reliability.

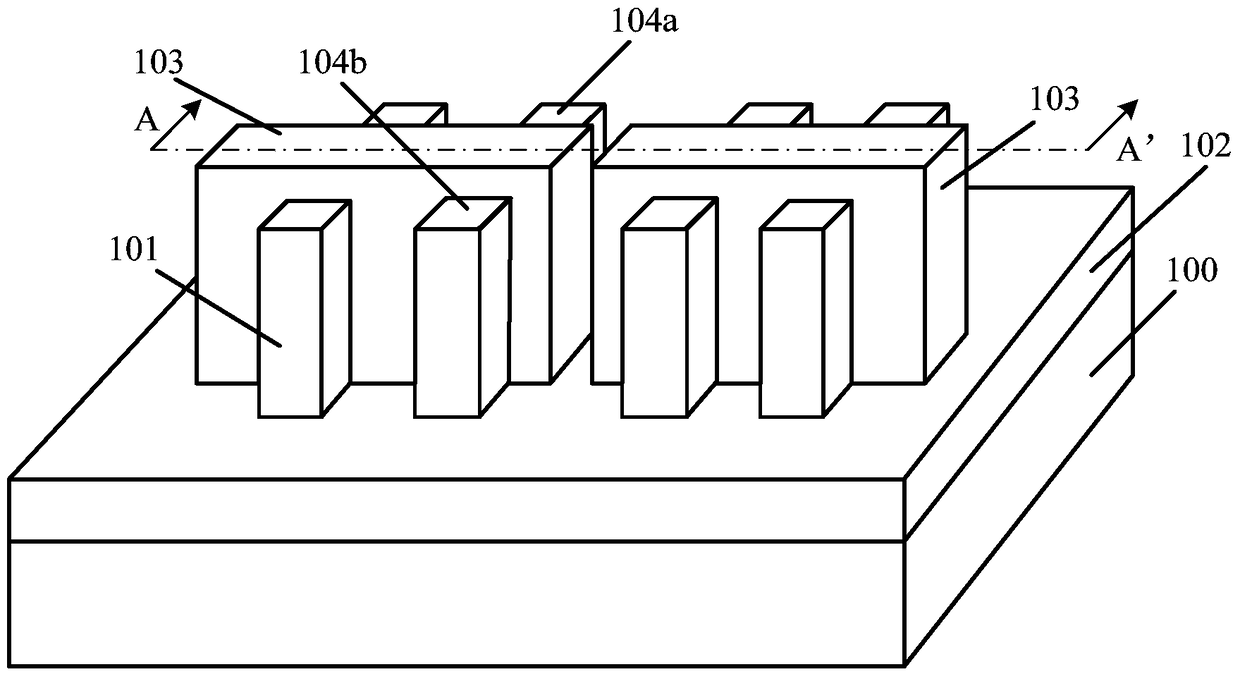

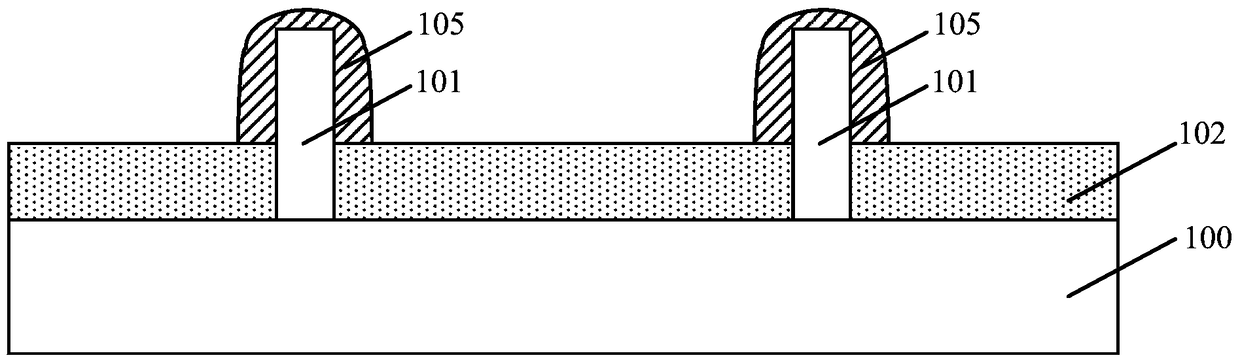

[0036] In order to further reduce the size of the semiconductor device and increase the integration of the semiconductor device, a high-K metal gate (High-K Metal Gate, HKMG for short) structure is introduced into the transistor. Please continue to refer figure 1 , the gate structure 103 includes: a gate dielectric layer located on the sidewall and top surface of the fin 101 , and a gate layer located on the surface of the gate dielectric layer. When the gate structure 103 is a high-K metal gate structure, the material of the gate dielectric layer is a high-K dielectric material, and the material of the gate layer is metal.

[0037] However, due to the large difference in lattice constant between the high-K dielectric material and the material of the fin portion 101, the lattice matching between the gate dielectric layer and the fin portion 101 is low, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More