Decoding method of low-density parity check codes

A low-density parity and check code technology, which is applied to the application of error detection coding of multiple parity bits, error correction/detection using block codes, data representation error detection/correction, etc., can solve the problem of consuming logic resources, Occupy logic resources, increase decoding delay and other issues, to achieve the effect of shortening decoding time, simplifying the decoding process, and providing parallel processing capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

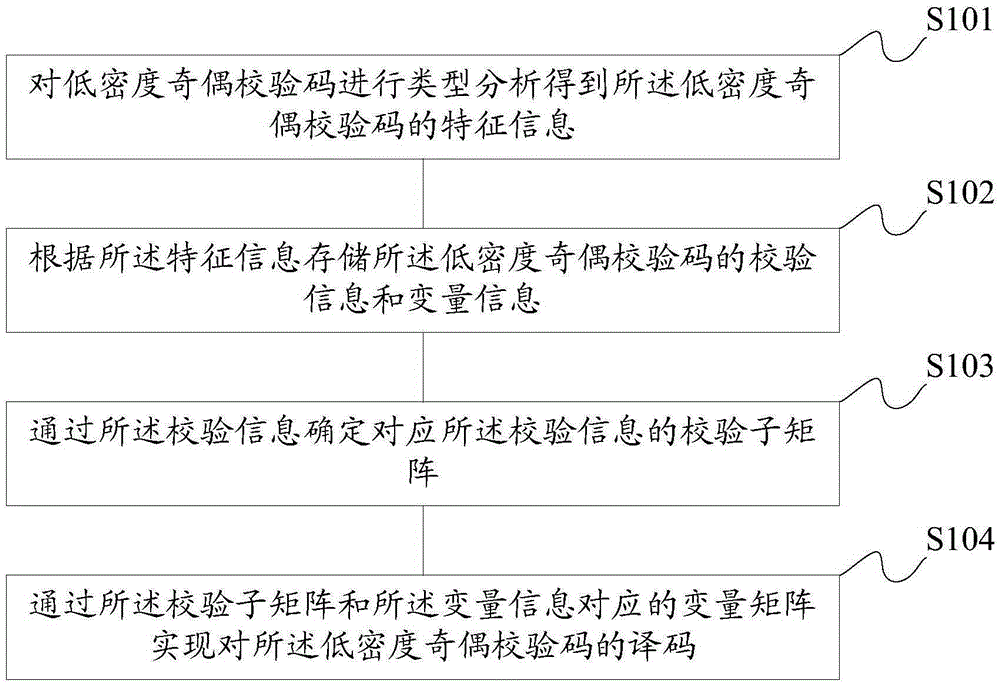

[0035] This embodiment provides a decoding method of LDPC codes, such as figure 1 As shown, the method of this embodiment includes:

[0036] Step S101, performing type analysis on the LDPC code to obtain characteristic information of the LDPC code;

[0037] LDPC code is a block error correction code with a sparse parity check matrix. It is applicable to almost all channels, so it has become a research hotspot in the coding field in recent years. Its performance is close to the Shannon limit, and its description and implementation are simple, easy to carry out theoretical analysis and research, simple decoding and parallel operation, suitable for hardware implementation. Generally, LDPC codes can be divided into regular LDPC codes and irregular LDPC codes according to the data format. Regular LDPC codes and irregular LDPC codes have different complexity in the decoding process. Therefore, regular LDPC codes and irregular LDPC codes can be classified first to reduce the deco...

Embodiment 2

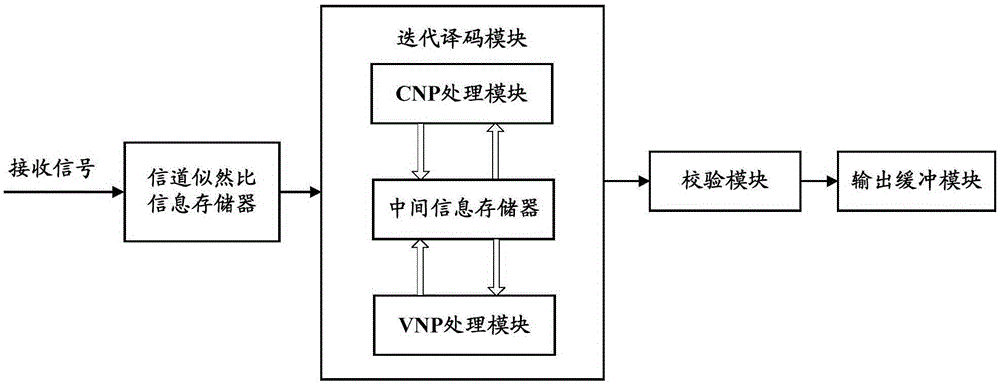

[0051] In order to overcome the existing design methods, there are large consumption of hardware resources, inflexible design of parallelism, and it is difficult to meet the requirements of high-speed, effective and reliable data communication. In the design scheme adopted by the present invention, the inherent block random access memory (BlockRAM) resource inside the FPGA can be utilized, a part of the BlockRAM is used as an address generation and control module, and the other part is used to store process data generated by iterative operations, realizing orderly control of a large number of The reading and writing of data does not require the design of data shifting and switching networks, which reduces the complexity of implementation and saves resources at the same time; adopts effective digital signal processing methods, first performs calculations, and truncates the resulting data according to requirements, reducing the cost of intermediate processing Accuracy loss; analy...

Embodiment 3

[0064] The method of the present invention will be described in further detail below in conjunction with the accompanying drawings.

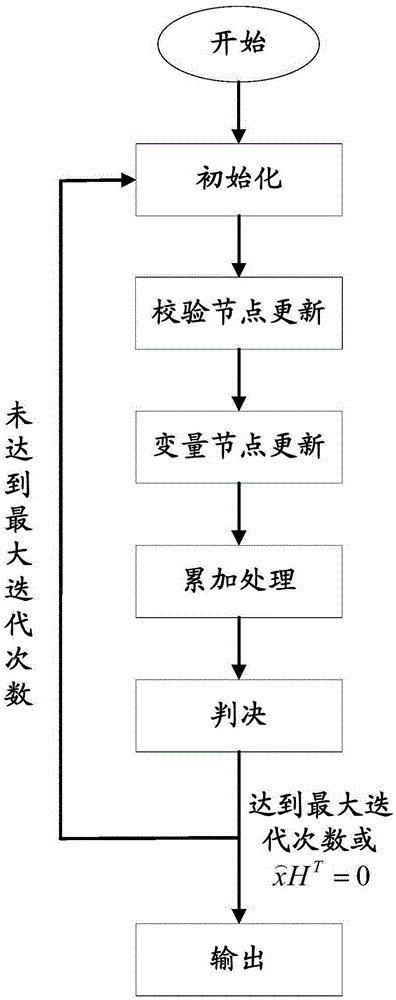

[0065] attached figure 2 The flow chart of the LDPC code decoding algorithm used in this method.

[0066] The decoding algorithm adopted in the present invention is the minimum sum algorithm with offset, and the specific decoding algorithm steps are as follows:

[0067] 1) Initialization. A priori probability of information bits is preset for a specific channel.

[0068] LLR n = y n , Z m n = LLR n , ∀ m - - - ( 1 )

[0069] Among them, LLR n is the log likelihood ratio; y n is the initial channel eigenvalue; Z mn Be the channel l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com