Adjusting and optimizing method utilizing PID to achieve fluctuations of CPU and internal storage VR output voltage

An output voltage and memory technology, applied in the field of general server power supply, can solve the problems of system downtime and large voltage fluctuation, and achieve the effect of improving product quality, ensuring power supply stability, and improving debugging efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

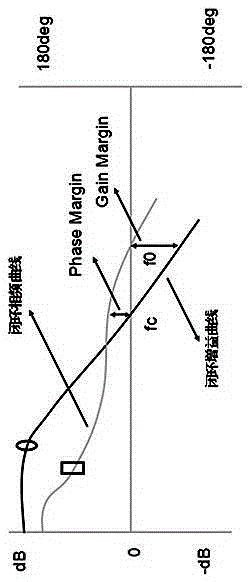

[0029] An optimization method that uses PID to realize the output voltage fluctuation of CPU and memory VR. By adjusting the PID parameters in the main chip of CPU and memory VR, combined with the measurement of VR Bode diagram, the optimal PID parameters are obtained to achieve The adjustment of the CPU and memory VR output voltage keeps the CPU and memory VR output voltage within a small fluctuation range under various load conditions, enhancing the power supply stability of the server system.

Embodiment 2

[0031] On the basis of embodiment 1, the implementation steps of the method described in this embodiment are as follows:

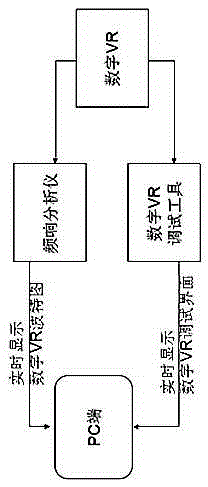

[0032] 1) if figure 2 As shown, build a debugging platform: select the mainboard of the server to be debugged, connect the signal probe of the frequency response analyzer to the 10ohm resistor of the feedback terminal of the CPU or memory VR to be tested (the 10ohm resistor has been reserved for debugging when the motherboard is designed , after mass production, the resistor will be removed);

[0033] 2) Connect the frequency response analyzer to the PC computer with a USB-GPIB conversion cable;

[0034] 3) Connect the digital VR debugging tool to the I2C interface of the motherboard, and plug the other end of the tool into the USB interface of the PC;

[0035] 3) After the debugging platform is built, open the installed digital VR debugging software (such as Infineon's Powercode4.3) on the PC. At the same time, open the installed Bode plot (ie: bodepl...

Embodiment 3

[0043] On the basis of Embodiment 2, this embodiment solidifies the obtained optimal PID in the digital VR chip, which can realize the optimization of VR output voltage fluctuation, and realize the output voltage of CPU and memory VR under all user loads , the voltage fluctuations are within the safe voltage range, ensuring the stability of the power supply of the server system.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com